Видеокамера

Иллюстрации

Показать всеИзобретение относится к бытовой цифровой видеотехнике, может использоваться для записи и воспроизведения видеоизображения. Технический результат - получение при съемке правого и левого кадров стереопар и восприятие при воспроизведении зрителем объемного изображения достигается тем, что в видеокамеру вводятся второй объектив, двухканальный фотоэлектрический преобразователь, пять АЦП видеосигнала, шесть кодеров и устройство воспроизведения, содержащее каналы видеосигналов R, G, В, каждый из которых включает декодер, блок обработки кодов и блок импульсных усилителей, и включающее ИК-передатчик, ЗД-очки (три-Д-очки) и ИК-приемник на оправе очков. 13 ил., 1 табл.

Реферат

Изобретение относится к бытовой цифровой видеотехнике, может использоваться для записи и воспроизведения видеоизображения. Прототипом принята цифровая видеокамера [1, с.546], содержащая объектив, фотоэлектрический преобразователь из светочувствительных матриц трех ПЗС, АЦП видеосигнала и кодек, видеоискатель, устройство записи на накопитель цифровой информации, компоненты управления и внешний интерфейс. Недостатком прототипа является отсутствие формирования и воспроизведения для восприятия зрителем объемного изображения.

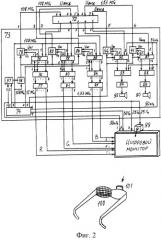

Цель изобретения ввести в процесс видеокамеры формирование и воспроизведение для восприятия зрителем объемного изображения. Техническим результатом является получение при съемке правого и левого кадров стереопар и восприятие зрителем при воспроизведении объемного изображения. Технический результат достигается введением в видеокамеру двухканального фотоэлектрического преобразователя, формирующего стерепары из правого и левого кадров, последовательно воспроизводимые на экране цифрового монитора и наблюдаемые зрителем раздельно через ЗД-очки, получая эффект объемного изображения. В видеокамере формируется изображение одного пространства в двух последовательно идущих правом и левом кадрах, составляющих стереопару. Частота стереопар 25 Гц, частота кадров 50 Гц /25+25/. Видеорежим в видеокамере: 600строк × 400отсчетов × 50кадров. Получаемая цифровая информация проходит сжатие в кодерах видеокамеры с коэффициентами от 2 до 255 и записывается в накопитель цифровой информации. Для воспроизведения накопитель цифровой информации подключается к устройству воспроизведения, в котором сжатые потоки кодов восстанавливаются, число отсчетов в каждой строке удваивается, и коды видеосигналов R, G, В стерепар подаются на цифровые входы применяемого цифрового монитора. Зритель объемное изображение воспринимает через ЗД-очки при помощи ИК-передатчика, устанавливаемого на корпусе монитора, и ИК-приемника, расположенного на оправе ЗД-очков.

Сущность заявляемого изобретения в том, что в видеокамеру, содержащую один объектив, фотоэлектрический преобразователь, АЦП видеосигнала, накопитель цифровой информации и видеоискатель, введены второй объектив, синтезатор частот, триггер, три ключа, со второго по шестой АЦП видеосигнала, два АЦП сигнала звука, с первого по шестой кодеры, с первого по пятый блоки элементов И и устройство воспроизведения, фотоэлектрический преобразователь содержит первый усилитель и первый пьезодефлектор с отражателем на торце, второй усилитель и второй пьезодефлектор с отражателем на торце, третий усилитель и третий пьезодефлектор с двумя отражателями на торце, шесть источников опорных напряжений, четыре дихроичных зеркала, шесть микрообъективов, шесть фотоприемников, шесть предварительных усилителей, блоки строчной и кадровой разверток, устройство воспроизведения содержит синтезатор частот, элемент И и ключ, три канала видеосигналов, каждый из которых включает ключ, декодер, блок обработки кодов и блок импульсных усилителей, два канала звука, каждый из ключа, декодера, регистра сигнала звука, блока формирования звукового аналового сигнала и громкоговорителя, и введены ИК-передатчик, ЗД-очки и ИК-приемник на оправе ЗД-очков.

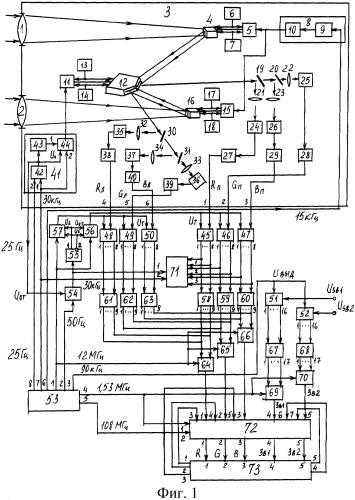

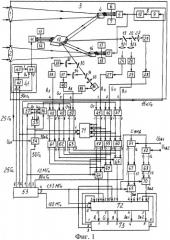

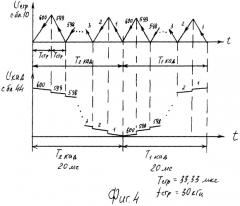

Функциональная схема видеокамеры на фиг.1, устройство воспроизведения на фиг.2, развертка кадра на фиг.3, формы управляющих напряжений на фиг.4, АЦП видеосигнала на фиг.5. АЦП сигнала звука на фиг.6, конструкция пьезодефлектора на фиг.7, суммирующий усилитель на фиг.8, блок элементов И на фиг.9, кодер на фиг.10, декодер на фиг.11, блок обработки кодов на фиг.12, развертка кадра на экране монитора на фиг.13.

Видеокамера включает /фиг.1/ первый объектив 1 /правый/, второй объектив 2 /левый/, фотоэлектрический преобразователь 3, являющийся датчиком видеосигналов двух изображений одного пространства: правого RП, GП, ВП и левого RЛ, GЛ, ВЛ, первый пьезодефлектор 4 с отражателем на торце, расположенный в фокальной плоскости первого объектива 1, первый усилитель 5, первый источник 6 положительного опорного напряжения, второй источник 7 отрицательного опорного напряжения, блок 8 строчной развертки из задающего генератора 9 и выходного каскада 10, последовательно соединенные второй усилитель 11 и второй пьезодефлектор 12, передний торец которого имеет две грани, расположенные под соответствующим углом друг к другу и с отражателем на каждой грани, третий источник 13 положительного опорного напряжения, четвертый источник 14 отрицательного опорного напряжения, последовательно соединенные третий усилитель 15 и третий пьезодефлектор 16 с отражателем на торце, расположенный в фокальной плоскости второго /левого/ объектива 2, пятый источник 17 положительного опорного напряжения, шестой источник 18 отрицательного опорного напряжения, второй объектив 2 расположен слева от первого объектива 1, оптическая ось его параллельна оптической оси объектива 1, расстояние между ними соответствует оптимальному получению стереоскопического эффекта для человеческого зрения, расположенные друг за другом последовательно первое 19 и второе 20 дихроичные зеркала, первый 21, второй 22, третий 23 микрообъективы, первый 24, второй 25, третий 26 фотоприемники, первый 27, второй 28, третий 29 предварительные усилители, расположенные последовательно друг за другом третье 30, четвертое 31 дихроичные зеркала, четвертый 32, пятый 33, шестой 34 микрообъективы, четвертый 35, пятый 36, шестой 37 фотоприемники, четвертый 38, пятый 39, шестой 40 предварительные усилители, блок 41 кадровой развертки, включающий последовательно соединенные элемент И 42, задающий генератор 43 и суммирующий усилитель 44. Видеокамера включает первый АЦП 45 /сигнал RП/, второй АЦП 46 /сигнал GП/, третий АЦП 47 /сигнал ВП/, четвертый АЦП 48 /сигнал RЛ/, пятый АЦП 49 /сигнал GЛ/, шестой АЦП 50 /сигнал ВЛ/, первый АЦП 51 сигнала звука Зв 1 и второй АЦП 52 сигнала звука Зв 2, синтезатор 53 частот, последовательно соединенные первый ключ 54 и триггер 55, второй ключ 56, третий ключ 57, с первого по шестой 58-63 кодеры, первый 64, второй 65, третий 66 блоки элементов И, первый 67, второй 68 кодеры сигнала звука, первый 69 и второй 70 блоки элементов И сигнала звука, видеоискатель 71, накопитель 72 цифровой информации и устройство 73 воспроизведения.

Устройство 73 воспроизведения /фиг.2/ содержит синтезатор 74 частот, канал видеосигнала R, включающий первый ключ 78 и последовательно соединенные первый декодер 75, первый блок 76 обработки кодов и первый блок 77 импульсных усилителей, канал видеосигнала G, включающий второй ключ 82 и последовательно соединенные второй декодер 79, второй блок 80 обработки кодов и второй блок 81 импульсных усилителей, канал видеосигнала В, включающий третий ключ 86 и последовательно соединенные третий декодер 83, третий блок 84 обработки кодов и третий блок 85 импульсных усилителей, содержит первый канал звука, включающий четвертый ключ 91 и последовательно соединенные первый декодер 87 кодов звука, регистр 88 сигнала звука, блок 89 формирования аналового звукового сигнала из ЦАП, фильтра низкой частоты и усилителя мощности, и громкоговоритель 90, второй канал звука, включающий пятый ключ 96 и последовательно соединенные второй декодер 92 кодов звука, регистр 93 сигнала звука, блок 94 формирования аналового звукового сигнала из ЦАП, фильтра низкой частоты и усилителя мощности, и громкоговоритель 95, и включает последовательно соединенные элемент И 97 и шестой ключ 98, ИК-передатчик 99, расположенный на корпусе цифрового монитора, ЗД-очки 100 и ИК-приемник 101, расположенный на оправе ЗД-очков. Для воспроизведения изображения применяется цифровой монитор с цифровым входом для кодов сигналов R, G, В раздельно. В качестве цифрового монитора могут использоваться цифровые плоскопанельные ЖК-мониторы технологии TFT [5, с.476, 487 табл.14.5], мониторы по технологии плазменных /РДР/ или светодиодных /LЕД/ элементов и электролюминесцентные цифровые мониторы [5, с.489], имеющие цифровые входы для приема кодов R, G, В, принимая коды правого и левого кадров стерепар и управляющие сигналы частоты строк 30 кГц, частоты кадров 50 Гц и частоты стереопар 25 Гц, цифровой монитор выполняет поочередно развертки правого и левого кадров, развертка растра и кадров должна соответствовать развертке растра и кадров фотоэлектрическим преобразователем 3, фиг.13.

Воспроизводимый видеорежим: 600строк × 800отсчетов × 50 Гц. Шесть АЦП 45-50 выполнены идентично /фиг.5/, каждый включает последовательно соединенные видеоусилитель 102 и пьезодефлектор 103 с отражателем на торце, источник 104 положительного опорного напряжения, источник 105 отрицательного опорного напряжения, излучатель из импульсного светодиода 106, щелевой диафрагмы 107 и микрообъектива 108, линейку 109 многоэлементного фотоприемника, входные окна которой расположены против отражателя пьезодефлектора 103 и оптически соединены с излучателем, и шифратор 110. Входом АЦП является вход видеоусилителя 102, выходом - выходы шифратора 110. Управляющим входом является вход импульсного светодиода 106. АЦП 51 и 52 идентичны /фиг.6/, каждый включает последовательно соединенные делитель 111 напряжения, блок 112 ключей, согласующий усилитель 113, усилитель 114 звуковой частоты и пьезодефлектор 115 с отражателем на торце, источник 116 положительного опорного напряжения, источник 117 отрицательного опорного напряжения, излучатель из импульсного светодиода 118, щелевой диафрагмы 119 и микрообъектива 120, линейку 121 многоэлементного фотоприемника, входные окна которой расположены против отражателя пъезодефлектора 115 и оптически соединены с излучателем, и последовательно соединенные первый дешифратор 122, шифратор 123 и второй дешифратор 124, и регистр 125, выходы которого являются выходами АЦП 51 /52/. Входом является вход делителя 111 напряжения, управляющим входом - вход импульсного светодиода 118. Пьезодефлекторы 3, 11, 16, 103, 115 выполнены одинаково /фиг.7/, каждый включает [3, с.118] первый 126, второй 127 пьезоэлементы, внутренний электрод 128, первый 129, второй 130 внешние электроды, один конец пьезопластин закреплен в держателе 131, на их свободном торце закреплен световой отражатель 132. Суммирующий усилитель 44 включает /фиг.8/ последовательно соединенные 10-разрядный счетчик 133 импульсов и дешифратор 134, первый 135 и второй 136 ключи, первый 137 и второй 138 формирователи импульсов и выходной усилитель 139. Входами являются первый вход выходного усилителя 139 и счетный вход счетчика 133 импульсов, управляющим входом являются объединенные входы управляющего входа счетчика 133 импульсов, первого управляющего входа ключа 135 и второго управляющего входа ключа 136, выходом является выход выходного усилителя 139. С первого по шестой кодеры 58-63 /фиг.10/ идентичны, каждый включает последовательно соединенные регистр 140, схема 141 сравнения /компаратор/, счетчик 142 импульсов и дешифратор 143, и последовательно соединенные блок 144 элементов задержек, блок 145 ключей и выходной регистр 146. 1-8 информационными входами являются поразрядно объединенные входы регистра 140, первые входы схемы 141 сравнения и входы блока 144 элементов задержек. Выходами являются выходы 1-9 разрядов выходного регистра 146.

Первый и второй кодеры 67, 68 сигнала звука выполнены аналогично кодерам 58-63, и соответственно 16-разрядным кодам сигналов звука регистр 140, схема 141 сравнения, счетчик 142 импульсов и дешифратор 143 являются 16-разрядными, блок 144 имеет 16 элементов задержек, блок 145 имеет 16 ключей /по числу разрядов в коде/, а выходной регистр 146 17-разрядный.

С первого по третий декодеры 75, 79, 83 /фиг.2/ идентичны, каждый включает /фиг.11/ последовательно соединенные 9-разрядный первый регистр 147, первый блок 148 ключей /8 ключей по числу разрядов в коде/ и 8-разрядный второй регистр 149, последовательно соединенные второй блок 150 ключей /из восьми ключей/, 8-разрядный вычитающий счетчик 151 импульсов и дешифратор 152, первый 153 и второй 154 ключи. Информационным входом декодера является информационный вход первого регистра 147, первым управляющим входом является первый управляющий вход первого регистра 147, вторым управляющим входом являются объединенные входы второго управляющего входа первого регистра 147 и сигнальные входы ключей 153, 154, первым управляющим выходом декодера является выход 9-го разряда первого регистра 147, вторым управляющим выходом декодера является выход дешифратора 152. Выходом декодера являются выходы 1-8 разрядов второго регистра 149. Декодеры 87, 92 кодов звука выложены аналогично декодеру 75, а так как коды звуковых сигналов 16-разрядные, то первый регистр 147 имеет 17 разрядов, первый 148 и второй 150 блоки ключей имеют по 16 ключей, вычитающий счетчик 151 импульсов и дешифратор 152 16-разрядные, второй регистр 149 является также 16-разрядным.

Блоки 76, 80, 84 обработки кодов идентичны, каждый включает /фиг.12/ триггер 155, первый 156, второй 157 блоки ключей /по 8 штук в каждом/, первый 158, второй 159, третий 160, четвертый 161 регистры, пятый 162 и шестой 163 регистры, блок 164 задержек, сумматор 165 и 16 диодов. 1-8 информационными входами являются поразрядно объединенные входы 156, 157 блоков ключей, на них поступают с частотой 12 МГц /12 Мбайт/с/ коды цветового сигнала R. Управляющим входом является вход триггера 155. Выходами являются поразрядно объединенные 1-8 выходы регистров 162, 163 и блока 144 задержек. С выхода блока 76 /80, 84/ коды в параллельном виде следуют с частотой 24 МГц /24 Мбайт/с/, период следования 41,5 нс, в блок 77 импульсных усилителей, которых в блоке 8 штук.

Накопитель 72 цифровой информации представлен пятью твердотельными носителями, например, типа РС Card [с.328], объединенными в один корпус для удобства размещения их в видеокамере. 1-3 твердотельные носители производят синхронное накопление 9-разрядных кодов цветовых сигналов R, G, В /9-й разряд служебный, появляется при сжатии цифровой информации/, четвертый и пятый твердотельные носители синхронно производят накопление 17-разрядных кодов первого и второго звуковых сигналов /17-й разряд служебный, появляется при сжатии информации/. Максимальная скорость поступления кодов видеосигналов на 1, 2, 3 входы накопителя 72 цифровой информации составляет 108 Мбит/с /12 Мбайт/с/, максимальная скорость поступления кодов звуковых сигналов на 4 и 5 входа блока 72 /фиг.1/ составляет 1,53 Мбит/с. За час работы видеокамеры при отсутствия сжатия информации объем информации каждого цветового сигнала составит 43,2 Гбайт /12 Мбайт/с × 3600 с/. Объем звуковой информации одного канала составит 5,5 Гбит/час. В заявляемой видеокамере производится сжатие цифровых потоков каждого с плавающим коэффициентом от 2 до 255, поэтому регистрируемый объем цифровой информации будет меньше в 50-100 раз. Видеоискатель 71 представляется ЖК-дисплеем на основе жидкокристаллической TFT матрица размером 4×5 см. Видеоискаталем 71 используются коды о АЦП 45, 46, 47 /фиг.1/, воспроизводимый кадр 600 строк с 400 отсчетами в каждой, частота кадров 25 Гц, управляющие сигналы импульсы частоты отрок 30 кГц и импульсы частоты кадров 50 Гц.

Частота дискретизации видеосигналов в видеокамере:

fД = 600строк × 50 Гц × 400отсч = 12 МГц,

где: 400 - число отсчетов, кодируемых в строке.

fстр = 600×50 Гц = 30 кГц

где: 50 Гц - частота кадров: 25 правых + 25 левых.

Тактовая частота следования разрядов кодов видеосигналов в накопитель 72 цифровой информации:

fТ = 12 МГц × 9 разр = 108 МГц

9 - число разрядов в коде, 9-й разряд служебный.

fт3В = 90 кГц × 17р = 1,53 МГц

90 кГц - частота дискретизации звуковых сигналов.

17 - число разрядов в коде звука после сжатия информации.

Фотоэлектрический преобразователь 3 /фиг.1/ является датчиком правого и левого изображения одного и того же пространства, формирует три аналоговых видеосигнала правого изображения RП, GП, ВП, которые с предварительных усилителей 27, 28, 29 поступают в АЦП 45, 46, 47, и три аналоговых видеосигнала левого изображения RЛ, GЛ, BЛ, которые поступают с предварительных усилителей 38, 39, 40 в АЦП 48, 49, 50. АЦП 45-50 преобразуют аналоговые видеосигналы в 8-разрядные коды. Поочередная выдача кодов видеосигналов сначала с АЦП 45-47 и затем с АЦП 48-50 выполняется триггером 55 и ключами 56, 57. Импульсы частоты кадров 50 Гц с восьмого выхода синтезатора частот 53 через открытый первый ключ 54 поступают на вход триггера 55. Сигнал с первого выхода триггера 55 открывает ключ 56, пропускающий UТ в период 20 мс первого /нечетного/ кадра импульсы 12 МГц дискретизации на тактовые входы АЦП 45-47, коды с которых в параллельном виде поступают с частотой 12 МГц /Мбайт/с/ в кодеры 58, 59, 60. АЦП 48-50 в это время коды не выдают, в них не поступают UТ импульсы. С приходом второго импульса 50 Гц в триггер 55 ключ 56 закрывается, открывается ключ 57, пропускающий тактовые импульсы на управляющие входы АЦП 48-50, коды с которых в период 20 мс в параллельном виде поступают на входы кодеров 61, 62, 63. На вход триггера 55 импульсы 50 Гц поступают с выхода первого ключа 54, который открывается импульсом частоты стереопар 25 Гц с выхода элемента И 42 в блоке 41 кадровой развертки. Этим определяется формирование кодов видеосигналов всегда с первого кадра стереопары. При нечетном кадре пьезодефлектор 12 производит развертку кадра вниз /фиг.3/: правые кадры в стереопаре первые, левые кадры - вторые. АЦП 45-47 кодируют видеосигналы только правых кадров, АЦП 48-50 кодируют видеосигналы левых /четных/ кадров. Синтезатор 53 частот выдает: с первого выхода импульсы 12 МГц частоты дискретизации видеосигналов на входы ключей 56, 57 и на входы блоков 64-66 элементов И, со второго выхода импульсы частоты 50 Гц кадров на вход первого ключа 54, с третьего выхода импульсы 90 кГц частоты дискретизации сигнала звука на управляющие входы АЦП 51, 52, с четвертого выхода импульсы 1,53 МГц на управляющие входы блоков 69, 70 элементов И и на первый управляющий вход накопителя 72 цифровой информации, с пятого выхода импульсы 108 МГц на второй управляющий вход накопителя 72 цифровой информации, с шестого - импульсы 15 кГц в блок 8 строчной развертки, с седьмого - импульсы 30 кГц строчной частоты на первый вход элемента И 42 и на второй вход /управляющий/ видеоискателя 71, с восьмого выхода импульсы 25 Гц на второй вход элемента И 42. АЦП 51, 52 преобразуют сигналы звука в 16-разрядные коды, которые в параллельном виде поступают на входы кодеров 67, 68. Блок 8 строчной развертки состоит из задающего генератора 9 и выходного каскада 10. С блока 10 управляющее напряжение треугольной равнобедренной формы /фиг.4/ усиливается усилителями 5 и 15 и приводит пьезодефлекторы 4 и 16 в колебательное движение с частотой 15 кГц. Развертка отрок при этом идет с частотой 30 кГц и без обратных ходов /фиг.3/. Сигнал с усилителя 5 /15/ поступает на внутренний электрод 128 /фиг.7/, к внешнему электроду 129 приложено напряжение с источника 6 /17/, к внешнему электроду 130 приложено напряжение с источника 7 /18/. С подачей управляющего напряжения на внутренний электрод 128 пьезодефлекторы 4 и 16 приходят в синхронное и синфазное колебания и выполняют развертку строк правого и левого кадров соответственно на первом и втором отражателях пьезодефлектора 12, который выполняет развертку изображения по вертикали. Процесс работы пьезодефлектора 11 тот же, что и пьезодефлектора 4, но колеблется он с частотой 25 Гц и формирует 50 кадров в секунду, кадровая развертка также без обратных ходов /фиг.3/. С выхода суммирующего усилителя 44 выдается линейно изменяющееся и ступенчатое управляющее напряжение, усиливаемое усилителем 11. При развертке правых /нечетных/ кадров первый отражатель пьезодефлектора 12 отклоняет развертку строк вниз, при развертке левых /четных/ кадров второй отражатель отклоняет развертку строк вверх. Суммирующий усилитель 44 производит суммирование треугольного управляющего напряжения с задающего генератора 43 с импульсами 30 кГц частоты строк, что и дает линейное и ступенчатое напряжение /фиг.4/ для усилителя 11. Каждый импульс строки перемещает следующую строку на шаг в одну отроку /в момент захода строки за край кадра/. В кадре развертывается 600 строк, развертка строк прогрессивная /построчная/. Назначение блоков 133-138 /фиг.8/ подавать на второй вход выходного усилителя 139 в нужное время отрицательные /положительные/ импульсы соответствующей амплитуды и длительности. Перед разверткой стереопары сигнал UО 25 Гц с элемента И 42 /фиг.1/ обнуляет счетчик 133 импульсов. Счетчик 133 10-разрядный и производит счет импульсов частоты строк 30 кГц, цикл счета 600 импульсов. В конце развертки нечетного /правого/ кадра с приходом 600 импульса счетчик 133 импульсов формирует двоичный код числа 600 /1001011000/, который дешифрируется дешифратором 134, импульс с выхода закрывает первый ключ 135, открывает второй ключ 136, пропускающий следующие 600 импульсов во второй формирователь 138 импульсов, выдающий положительные импульсы на второй вход выходного усилителя 139. Идет развертка левого кадра стереопары. Затем приходит на первый управляющий вход суммирующего усилителя 44 второй импульс 25 Гц, счетчик 133 обнуляется, повторяется процесс разверток правого и левого кадров стереопары. Ширина отражателей пьезодефлекторов 4 и 16 одинаковая, принята 0,02 мм, длина по 12 мм /0,02 ми × 600/. Ширина отражателей пьезодефлектора 12 по 0,02 мм, длина по 8 мм /0,02 мм × 400отсч/. Отраженные лучи от правого отражателя пьезодефлектора 12 поступают: красные лучи отражаются от первого дихроичного зеркала 19 и микрообъективом 21 собираются в фотоприемник 24, синие лучи проходят дихроичное зеркало 19, отражаются от второго 20 и микрообъективом собираются в фотоприемник 26, зеленые лучи проходят сквозь оба дихроичных зеркала 19, 20 и микрообъективом 22 собираются в фотоприемник 25. С фотоприемников аналоговые видеосигналы поступают в свои предварительные усилители 27, 28, 29. Идентичный процесс проходят лучи, отраженные от левого отражателя пьезодефлектора 12, аналоговые видеосигналы поступают в предварительные усилители 38, 39, 40. Шесть аналоговых видеосигналов поступают на входы АЦП 45-50, которые имеют один принцип преобразования, заключающийся /фиг.5/ в развертке луча от светодиода 106 отражателем пьезодефлектора 103 по плоскости входных окон линейки 109 многоэлементного фотоприемника. Световой импульс преобразуется фотоприемником линейки в электрический сигнал, возбуждающий соответствующую шину шифратора 110, который выдает код мгновенного значения входного видеосигнала. Частота дискретизации 12 МГц поступает на вход светодиода 106. Щелевая диафрагма 107 и микрообъектив 108 формируют луч с апертурой, равной размерам входного окна одного фотоприемника линейки 109. Источник излучения светодиод АЛ402A с временем срабатывания 25 нс, с запасом удовлетворяющий дискретизации 12 МГц /83 нс/, линейка 109 включает 255 фотоприемников для кодирования видеосигналов 8-разрядным кодом, 28. Фотоприемниками являются лавинные фотодиоды ЛФД с временем срабатывания 10 нс. Выход каждого фотоприемника подключен к соответствующему входу шифратора 110, который представлен микросхемой К155ИВ1 [4, с.231] с временем срабатывания 20 нс. Время преобразования составляет 30 нс /10+20/, что составляет 33·106 преоб/с. Шифратор 110 формирует коды с 00000001 по 11111111. Первому фотоприемнику соответствует код 00000001, второму - код 00000010, третьему - 00000011 и т.д., 255-у - код 11111111. Скорость создания информации каждым АЦП составляет: 12 МГц × 8 раз = 96 Мбит/с или 12 Мбайт/с.

АЦП 51 и 52 преобразуют два сигнала звука в 16-разрядные коды. Частота дискретизации 90 кГц. Линейка 121 /фиг.6/ многоэлементного фотоприемника включает 1024 фотоприемников и осуществляет преобразование звукового сигнала в 10-разрядные коды, 210. Разрешающая способность принимается 10 мкВ. Преобразование сигналов, превышающих 210, выполняют совместно дешифратор 122, второй дешифратор 124, делитель 111 напряжения и блок ключей 112. С их применением диапазон кодирования становится 0-0,65536 В, т.е. 216. С шифратора 123 16-разрядные коды поступают в регистр 125, из которого выдаются в параллельном виде сигналами 90 кГц в кодер 67 /68/. Коды видеосигналов с АЦП 45-47 поступают в кодеры 58-60, коды с АЦП 48-50 поступают в кодеры 61-63, коды с АЦП 51, 52 соответственно в кодеры 67, 68. Все кодеры работают одинаково и выполняют сжатие потока цифровой информации выполнением операций: сравнение значений кодов потока по величине для определения кодов, равных по величине и следующих друг за другом, подсчет числа кодов, равных по величине, и формирование двоичного кода этого числа, введение кода числа равных по величине кодов в поток вслед за первым кодом своей последовательности и введение в этот код маркера для его опознания.

Число равных по величине кодов, следующих друг за другом, будет меняться, поэтому будет меняться и коэффициент сжатия от 2 до 255. Чем больше подряд равных по величине кодов, тем и выше степень сжатия информации. Код числа равных по величине кодов при восстановлении потока информации должен себя обнаруживать, для этого в 8-разрядный код видеосигнала в кодере вводится сигнал опознания в 9-й разряд кода. Восемь разрядов являются информативными, сигнал 9-го разряда является служебным маркером для опознания кода числа равных кодов в потоке при восстановлении сжатой информации.

Работа кодера 58 /59-63/, фиг.10.

8-разрядный код с АЦП 45 поступает одновременно на 1-8 входы регистра 140, на первые входы схемы 141 сравнения и на входы блока 144 элементов задержек. Исходное состояние ключей в блоке 145 открытое. Код в блоке 144 задерживается на длительность 18 нс /время срабатывания схема 141 сравнения/ и поступает через открытые ключи блока 145 в 1-8 разряды выходного регистра 146. Схема 141 сравнения выполняет сравнение по величине каждого предыдущего и последующего кодов для определения их равенства или неравенства. Схема 141 сравнения представлена двумя микросхемами 530СП1 с временем срабатывания 18 нс [4, с.279]. При неравенстве кодов А>В появляется сигнал на выходе 2 /в микросхеме выход 5 [4, с.272 рис.2.190]/, при равенстве кодов A=B появляется сигнал с выхода 1 /в микросхеме выход 6/, при А<В сигнал на выходе 3 /в микросхеме выход 7/. В случае равенства кодов А=В сигнал с выхода 1 блока 141 закрывает ключи в блоке 145, поступает счетным импульсом Uсч на счетный вход счетчика 142 и на первый управляющий вход регистра 140 как сигнал Uвыд. Счетчик 142 импульсов производит счет импульсов пока в потоке идут коды, равные по величине.

В случае неравенства кодов со схемы 141 сравнения следует сигнал с выхода 2 или 3, которые объединены, и сигналы их используются в качестве управляющих для обнуления регистра 140 /вход 2/ и выдачи Uвыд кода из выходного регистра 146. При равенстве кодов счетчик 142 /из микросхем К531ИЕ17П с временем срабатывания 12 нс [4, с.156]/ производит счет числа Uсч равных по величине кодов. Счетчик 142 импульсов 8-разрядный, максимальный код в нем 11111111 /255/. При сравнении в схеме 141 неравных кодов появляется сигнал с выхода 2 или 3, который сначала выдает с выходного регистра 146 содержащийся в нем код, затем выдает сформированный счетчиком 142 код в 1-8 разряды выходного регистра 146 и одновременно в 9-й разряд регистра 146 заносит сигнал, являющийся признаком кода со счетчика 142 импульсов, открывает ключи в блоке 145 и обнуляет UО регистр 140 /вход 2/. Содержащийся до этого в выходном регистре 146 код /перед первым импульсом в счетчик 142/ является первым кодом в последовательности равных кодов. Коды, следующие за этим кодом, являются равные по величине коды, подсчитанные счетчиком 142 импульсов, исключаются из потока. Таким образом, за их счет и идет сжатие потока информации. За первым кодом последовательности равных кодов следует код со счетчика 142 импульсов, причем в 1-8 разряды выходного регистра 146 поступают информативные сигналы, в 9-й разряд выходного регистра 146 поступает сигнал опознания. При следовании подряд равных кодов более 255 штук дешифратор 143 при коде 11111111 выдает сигнал, который открывает ключи в блоке 145, обнуляет регистр 140 и выдает из счетчика 142 импульсов в 1-8 разряды выходного регистра 146 сосчитанный код, а в 9-й разряд выходного регистра 146 сигнал опознания. Пропускная способность кодера определяется временем срабатывания схемы 141 сравнения /18 нс/ плюс время срабатывание счетчика 142 импульсов /12 нс/ и составляет 30 нс, т.е. 30 Мбайт/с. Коды сигналов R, G, В стерепар в последовательном виде с блоков 64-66 поступают на 1, 2, 3 входы накопителя 72 цифровой информации, на 4 и 5 входы которого поступают коды первого и второго сигналов звука. На первый и второй управляющие входы накопителя 72 с 4-го и 5-го выходов синтезатора 53 частот поступают соответственно импульсы 1,63 МГц и 108 МГц. Устройство 73 воспроизведения предназначено для просмотра снятого материала. Для воспроизведения информации с накопителя 72 цифровой информации /фиг.2/ к его 3, 4, 5, 6, 7 управляющим входам подключаются соответственно 1, 2, 3, 4, 5 управляющие выходы устройства 73 воспроизведения. Синтезатор 74 частот выдает: с первого выхода импульсы 30 кГц частоты строк на первый вход элемента И 97 и первый управляющий вход монитора, с второго - импульсы частоты стерепар 25 Гц на второй вход элемента И 97, на управляющий вход ИК-передатчика 99 и на третий управляющий вход цифрового монитора, с третьего - тактовые импульсы 108 МГц на первые управляющие входы декодеров 75, 79, 83 и на сигнальный вход шестого ключа 98, с четвертого - импульсы дискретизации 12 МГц на вторые управляющие входы декодеров 75, 79, 83 и на первые управляющие входы блоков 76, 80, 84 обработки кодов, с пятого - импульсы 1,53 МГц на сигнальные входы ключей 91, 96 и на первые управляющие входы декодеров 87, 92, с шестого импульсы 90 кГц на вторые управляющие входы декодеров 87, 92 и первые управляющие входы блоков 88, 93, с седьмого - импульсы 50 Гц частоты кадров на второй управляющий вход цифрового монитора. После включения питания с 1 и 2 выходов блока 74 на входы элемента И 97 поступают импульса 30 кГц и импульс 25 Гц /означающий развертку первого кадра стереопары/. Сигнал с элемента И 97 открывает шестой ключ 98, который пропускает тактовые импульсы 108 МГц на сигнальные входы ключей 78, 82, 86. Тактовые импульсы 108 МГц с ключей 78, 82, 86 поступают соответственно на 3, 4, 5 управляющие входы накопителя 72 цифровой информации и синхронно выдают коды видеосигналов R, G, В на информационные входы декодеров 75, 79, 83, которые осуществляют восстановление сжатой информации выполнением операций: определение в сжатом потоке кода числа равных по величине кодов, дешифрирование его для формирования числа сигналов выдачи первого кода по количеству изъятых кодов при сжатии, выдача первого кода последовательности по числу изъятых кодов при сжатии.

Работа декодера 75 /79, 83/, фиг.11.

Коды сжатых данных поступают на информационный вход первого регистра 147. Исходное состояние ключей в блоке 148 открытое, в блоке 150 закрытое, ключа 153 - открытое, ключа 154 - закрытое. В 1-8 разряды первого регистра 147 поступают информативные сигналы, при наличии в 9-м разряде кода сигнала опознания он поступает в девятый разряд регистра 147. Для заполнения разрядов первого регистра 147 на его первый управляющий вход поступают тактовые импульсы 108 МГц /12 МГц×9/ с синтезатора 74 частот выход 3. С регистра 147 код выдается управляющим сигналом Uвыд 12 МГц, посыпающий с блока 74 на второй управляющий вход регистра 147. При выдаче с регистра 147 сигналы с 1-8 разрядов поступают на 1-8 входы блоков 148 и 150 ключей. Так как ключи в блоке 148 открыты код проходит их и поступает в 1-8 разряды второго регистра 149, а с него 8-разрядный код выдается сигналом Uвыд1 с ключа 153, который и обнуляет разряды регистра 149. Пока в регистр 147 поступают 8-разрядные коды такой процесс повторяется. С приходом в первый регистр 147 9-разрядного кода, т.е. кода числа равных кодов, сигнал с девятого разряда регистра 147 при выдаче кода одновременно закрывает ключи в блоке 148, открывает ключи в блоке 150, закрывает ключ 153, открывает ключ 154 и закрывает ключ 78 /фиг.2/, который прерывает поступление сигналов Uвыд /108 МГц/ на третий управляющий вход накопителя 72 информации, следующие коды с первого выхода накопителя 72 цифровой информации в регистр 147 декодера выдаваться не будут. Код числа равных кодов через открытые ключи блока 150 поступает в вычитающий счетчик 151 импульсов. Сигнал с ключа 154 поступает на счетный вход вычитающего счетчика 151 /микросхема 100ИЕ137 с временем срабатывания 10,5 нс [4, с.428]/ и одновременно поступает как сигнал Uвыд2 на второй управляющий вход второго регистра 149. Сигнал Uвыд2 выдает из регистра 149 поступивший в него до этого код и при выдаче не обнуляет разряды регистра 149. Поэтому пока идет работа счетчика 151 на вычитание /до появления в нем кода 00000000/ с второго регистра 149 выдается один и тот же код. Этот код и представляет коды, изъятые при сжатии данных в данном месте потока. С выхода декодеров идут восстановленные потоки данных. Дешифратор 152 при поступлении в него кода 00000000 выдает сигнал, который одновременно закрывает ключ 154, открывает ключ 153, закрывает ключи в блоке 150, открывает ключи в блоке 148, он же со второго управляющего выхода декодера поступает на первый управляющий вход ключа 78 и Uот открывает ключ 78, с накопителя 72 цифровой информации в декодер 75 вновь поступают коды R. Далее процессы соответственно наличию или отсутствию сигнала опознания в 9-м разряду кода, чередуясь, повторяются. Пропускная способность декодера определяется временем срабатывания счетчика 151 вычитания /10,5 нс/ плюс время срабатывания дешифратора /18 нс/. Максимально возможная скорость восстановления потока составляет 35 Мбайт/с, которая с запасом удовлетворяет работе кодера. Восстановленные потоки кодов поступают в блоки 76, 80, 84 обработки кодов, выполняющие удвоение числа отсчетов в строке. Удвоение отсчетов выполняется получением промежуточных /средних/ кодов между каждым прошедшим кодом и следующим за ним: выполняется сложение предыдущего кода и последующего и деление кода суммы пополам. Каждый код используется дважды: первый раз как последующий, второй раз как предыдущий, поэтому в блоках 76, 80, 84 применяются по четыре регистра.

Работа блока 76 /80, 84/, фиг.12.

С приходом в триггер 155 первого импульса 12 МГц с его первого выхода сигнал Uвыд1 одновременно выдает: из регистра 159 "код 0" /из одних нулей/ в сумматор 165, из регистра 160 "код 0" в шестой регистр 163 и через диоды на вторые входы сумматора 165, открывает Uот1 ключи в блоке 156 /ключей в блоке по числу разрядов 8/ и регистры 158, 159 заполняются кодом "код 1". Сумматор 165 производит сложение "код 0 + код 0". Регистры при выдачи обнуляются. Деление кода суммы на 2 выполняется сдвигом кода суммы на младший разряд так, что младший разряд отбрасывается /как и при делении десятичного числа на 10/. Сдвиг выполняется соответствующим подключением выходов сумматора 165 к входам блока 164 элементов задержек:

| выходы сумматора 165 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| ↓ | ↓ | ↓ | ↓ | ↓ | ↓ | ↓ | ↓ | ||

| входы сумматора 164 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

Разряд 0 означает перенос в него при сложении кодов. В качестве сумматора 165 применены микросхемы К555ИМ6 [4, с.258] с временем сложения 24 нс. При удвоении отсчетов с 400 до 800 период следования кодов составляет 41,5 нс //. Процесс сложения занимает 24 нс, следовательно, блок 164 должен задерживать коды с сумматора еще на 17,5 нс /41,5-24/. Первый код №1 идет на выход с блока 164 через 41,5 нс после прихода сигнала Uвыд1 в регистра 159, 160. С приходом второго импульса в триггер 155 с его второго выхода сигнал Uвыд2 одновременно выдает: с регистра 163 код №2 "код 0", с регистра 158 "код 1" в пятый регистр 162 для задержки кода на 83 нс и через диода в сумматор 165, из регистра 161 "код 0" на вторые входы сумматора 165, открывает ключи в блоке 157 /Uот2/ и регистры 160, 161 заполняются кодом /"код 2". Регистры 162 и 163 предназначены для задержки кодов на 83 нс, в них первая половина времени задержки /41,5 нс/ приходится на время процесса суммирования в сумматоре 165 и время задержки кодов в блоке 164 /24+17,5/, поэтому коды с регистров 162, 163 следуют за кодами с блока 164 через 41,5 нс /24 МГц/. С приходом в сумматор "код 1" и "код 0" идет сложение "код 0 + код 1", при выдаче кода суммы в блок 164 деление на 2, и код №3 идет на выход. С приходом третьего импульса 12 МГц на вход триггера 155 с его первого выхода сигнал Uвыд3 одновременно выдает: из регистра 162 код №4 "код 1", из регистр