Модуль синхронизации

Иллюстрации

Показать всеИзобретение относится к приемному тракту радиолокационных или аналогичных систем и предназначено для обеспечения синхронизации работы всех составляющих приемного тракта, а также приемных и передающих блоков радиолокационных систем. Технический результат предлагаемого изобретения направлен на расширение функциональных возможностей предлагаемого технического решения, а именно на формирование сигналов, синхронизирующих работу блоков, входящих в состав бортовой радиолокационной станции (БРЛС), и работу модулей, входящих в состав бортового вычислительного комплекса (БВК), а также формирование сигналов, синхронизирующих работу блоков, входящих в состав автоматизированного рабочего места бортовой радиолокационной станции (АРМ БРЛС). Эта задача решается за счет того, что предложенный модуль синхронизации содержит высокочастотное устройство синхронизации, низкочастотное устройство синхронизации, высокочастотное буферное устройство и низкочастотное буферное устройство. Первый вход высокочастотного устройства синхронизации является входом сигналов управления, второй вход высокочастотного устройства синхронизации является входом сигнала опорной частоты, третий вход высокочастотного устройства синхронизации соединен с первым выходом низкочастотного устройства синхронизации, первый выход высокочастотного устройства синхронизации соединен с входом низкочастотного синхронизатора и с входом высокочастотного буферного устройства, а второй выход низкочастотного устройства синхронизации является выходом импульсов начала отсчета, второй выход низкочастотного устройства синхронизации соединен с входом низкочастотного буферного устройства, а двунаправленный вывод низкочастотного устройства синхронизации соединен с последовательной линией связи, первый выход высокочастотного буферного устройства является выходом импульса управления фазовым манипулятором, второй выход высокочастотного буферного устройства является выходом импульса управления задающим генератором, третий выход высокочастотного буферного устройства является выходом импульса запуска первого передатчика, четвертый выход высокочастотного буферного устройства является выходом импульса бланкирования приемника, пятый выход высокочастотного буферного устройства является выходом импульса запуска второго передатчика, первый выход низкочастотного буферного устройства является выходом тактового импульса синхронизации блоков радиолокационной станции, второй выход низкочастотного буферного устройства является выходом тактового импульса синхронизации модулей вычислительного комплекса. 4 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к приемному тракту радиолокационных или аналогичных систем и предназначено для обеспечения синхронизации работы всех составляющих приемного тракта, а также приемных и передающих блоков радиолокационных систем.

Одной из основных задач в радиолокационных системах и в устройствах передачи информации является обеспечение синхронизации работы всех составных частей.

Известно устройство для передачи информации с защитой от ошибок (патент РФ №1490713, Н03М 13/00, 1989), в котором работой всех блоков управляет синхронизатор. Этот синхронизатор для формирования последовательности импульсов содержит стабильный генератор частоты и соответствующие делители частоты и формирователи нормализованных сигналов. Синхронизатор вырабатывает только четыре последовательности импульсов: счетные импульсы, поступающие на счетный вход аналого-цифрового преобразователя (АЦП), тактовые импульсы с частотой символов, тактовые импульсы с частотой слов и кадровые импульсы.

Известно устройство для синхронизации (патент РФ №2198469, Н04L 7/02, 2003), предназначенное для выдачи синхронизирующего сигнала на устройство разделения сигнала, причем синхронизирующий сигнал частотно согласован с синхронизирующим сигналом на кодирующем устройстве. Такое устройство обеспечивает только синхронизацию промежуточного уровня сигнала, такого как транспортный уровень или уровень уплотнения многоуровневого сжатого видеосигнала.

Наиболее близким по функциональному назначению является синхронизатор, который входит в радиолокационную станцию для вертолета (патент РФ №2206903, G01S 7/28, 2003). Все высокочастотные сигналы, необходимые для работы радиолокационной станции, формируются в синхронизаторе путем умножения частоты сигнала задающего генератора, а низкочастотные синхронизирующие формируются путем деления частоты сигнала задающего генератора. Такой синхронизатор вырабатывает следующие частоты сигналов на соответствующих выводах: частота излучения, частота повторения импульсов, частота гетеродина, частота промежуточная, частота дискретизации аналого-цифрового преобразователя, частота синхронизации цифрового процессора сигналов, частота синхронизации цифрового процессора данных.

Указанный синхронизатор по своей структуре соответствует синтезатору частот, необходимых для когерентного режима работы, а также частот, синхронизирующих работу блоков, поэтому он не обеспечивает управление с вычислительного комплекса при различных режимах работы радиолокационной станции (РЛС).

Техническая задача предлагаемого изобретения направлена на расширение функциональных возможностей предлагаемого технического решения, а именно на формирование сигналов, синхронизирующих работу блоков, входящих в состав бортовой радиолокационной станции (БРЛС), и работу модулей, входящих в состав бортового вычислительного комплекса (БВК), а также формирование сигналов, синхронизирующих работу блоков, входящих в состав автоматизированного рабочего места бортовой радиолокационной станции (АРМ БРЛС).

Эта задача решается тем, что предложенный модуль синхронизации содержит высокочастотное устройство синхронизации, низкочастоное устройство синхронизации, высокочастотное буферное устройство и низкочастотное буферего устройство. Первый вход высокочастотного устройства синхронизации является входом сигналов управления, второй вход высокочастотного устройства синхронизации является входом сигнала опорной частоты, третий вход высокочастотного устройства синхронизации соединен с первым выходом низкочастотного устройства синхронизации, первый выход высокочастотного устройства синхронизации соединен с входом низкочастотного синхронизатора и с входом высокочастотного буферного устройства, а второй выход низкочастотного устройства синхронизации является выходом импульсов начала отсчета, второй выход низкочастотного устройства синхронизации соединен с входом низкочастотного буферного устройства, а двунаправленный вывод низкочастотного устройства синхронизации соединен с последовательной линией связи, первый выход высокочастотного буферного устройства является выходом импульса управления фазовым манипулятором, второй выход высокочастотного буферного устройства является выходом импульса управления задающим генератором, третий выход высокочастотного буферного устройства является выходом импульса запуска первого передатчика, четвертый выход высокочастотного буферного устройства является выходом импульса бланкирования приемника, пятый выход высокочастотного буферного устройства является выходом импульса запуска второго передатчика, первый выход низкочастотного буферного устройства является выходом тактового импульса синхронизации блоков радиолокационной станции, второй выход низкочастотного буферного устройства является выходом тактового импульса синхронизации модулей вычислительного комплекса.

Низкочастотное устройство синхронизации может содержать первый буфер, схему контроля, первую схему совпадения, вторую схему совпадения, устройство связи, третью схему совпадения, буферный регистр адреса, буферный регистр данных, первую схему И, вторую схему И, регистр периода тактового импульса, первую схему ИЛИ, формирователь тактового импульса, кроме того, первый, второй, третий, четвертый и пятый входы схемы контроля являются входами сигналов в высокочастотное устройство синхронизации, шестой вход схемы контроля является входом сигнала опорной частоты, седьмой вход схемы контроля является входом сигнала блокировки, восьмой вход схемы контроля является входом сигнала готовности модуля АЦП, девятый вход схемы контроля соединен с выходом формирователя тактового импульса, который является выходом тактового импульса, выход схемы контроля соединен с первым входом второй схемы И, первый вход устройства связи является входом ключа, второй и третий входы устройства связи являются входами последовательной линии связи, четвертый вход устройства связи соединен с выходом первой схемы ИЛИ, первый выход устройства связи соединен с первым входом буферного регистра адреса, с первым входом третьей схемы совпадения, со вторым входом второй схемы совпадения, со вторым входом первой схемы совпадения и является выходом адреса регистров синхронизатора, второй выход устройства связи соединен со вторым входом буферного регистра адреса, со вторым входом буферного регистра данных, со вторым входом регистра периода тактового импульса и является выходом сигнала записи данных, третий выход устройства связи соединен с первым входом буферного регистра данных, с первым входом регистра периода тактового импульса и является выходом данных, четвертый выход устройства связи соединен с входом первого буфера, выход которого соединен с третьим входом устройства связи, первый вход первой схемы совпадения является входом адреса слова «исправность», а выход соединен с вторым входом второй схемы И, первый вход второй схемы совпадения является входом адреса периода тактового импульса, а выход соединен с третьим входом регистра периода тактового импульса, второй вход третьей схемы совпадения соединен с выходом буферного регистра адреса, а выход соединен с вторым входом первой схемы И, выход буферного регистра данных соединен с первым входом первой схемы И, выход которой соединен с первым входом первой схемы ИЛИ, выход второй схемы И соединен с вторым входом схемы ИЛИ, выход регистра периода тактового импульса соединен с первым входом формирователя тактового импульса, второй вход которого является входом опорной частоты, а третий вход является входом сигнала переднего фронта тактового импульса.

Высокочастотное устройство синхронизации может содержать блок буферных регистров, первый формирователь, первую схему задержки, первую схему длительности, вторую схему длительности, первый инвертор, схему формирования, второй формирователь, шестую схему И, седьмую схему И, третий формирователь, схему сравнения, третью схему ИЛИ, второй инвертор, третью схему И, четвертую схему И, седьмой формирователь, вторую схему ИЛИ, пятую схему И, четвертый формирователь, пятый формирователь, шестой формирователь и второй буфер, при этом первый вход блока буферных регистров является входом данных; второй вход блока буферных регистров является входом адреса регистров синхронизатора, третий вход блока буферных регистров является входом сигнала записи данных, первый выход блока буферных регистров соединен с первым входом четвертого формирователя, второй выход блока буферных регистров соединен с пятым входом пятого формирователя, третий выход блока буферных регистров соединен с первым входом второго формирователя, четвертый выход блока буферных регистров соединен с вторым входом второго формирователя, пятый выход блока буферных регистров соединен с первым входом пятой схемы И, шестой выход блока буферных регистров соединен с первым входом второй схемы ИЛИ, седьмой выход блока буферных регистров соединен с первым входом первого формирователя, восьмой выход блока буферных регистров соединен с вторым входом первой схемы длительности и со вторым входом второй схемы длительности, девятый выход блока буферных регистров соединен с первым входом первой схемы задержки, десятый выход блока буферных регистров соединен с третьим входом четвертого формирователя, одиннадцатый выход блока буферных регистров соединен с седьмым входом пятого формирователя, двенадцатый выход блока буферных регистров соединен с шестым входом шестого формирователя, тринадцатый выход блока буферных регистров соединен с седьмым входом шестого формирователя, четырнадцатый выход блока буферных регистров соединен с входом первого инвертора и первым входом седьмой схемы И, с первым входом четвертой схемы И, с входом второго инвертора, со вторым входом четвертого формирователя, с шестым входом пятого формирователя, с четвертым входом шестого формирователя, пятнадцатый выход блока буферных регистров соединен с пятым входом шестого формирователя, шестнадцатый выход блока буферных регистров является выходом команды перезагрузки модуля АЦП, второй вход первого формирователя, второй вход первой схемы задержки, третий вход первой схемы длительности, пятый вход второго формирователя, второй вход седьмого формирователя, первый вход второй схемы длительности, второй вход схемы формирования, четвертый вход третьего формирователя, седьмой вход четвертого формирователя сигнала, второй вход пятого формирователя и первый вход шестого формирователя соединены с входом сигнала опорной частоты, первый выход первого формирователя является выходом импульса начала отсчета, второй выход первого формирователя соединен с входом схемы сравнения, с четвертым входом четвертого формирователя, с восьмым входом пятого формирователя и с восьмым входом шестого формирователя, третий выход первого формирователя соединен с третьим входом второй схемы длительности и с первым входом третьего формирователя, выход схемы сравнения соединен с первым входом седьмого формирователя, выход которого является выходом сигнала переднего фронта тактового импульса, выход первой схемы задержки соединен с первым входом первой схемы длительности и с третьим входом второго формирователя, первый выход которого является выходом импульса цели, а второй выход соединен с первым входом третьей схемы ИЛИ, выход первой схемы длительности соединен с четвертым входом второго формирователя, выход второй схемы длительности соединен с первым входом шестой схемы И, с пятым входом четвертого формирователя, с четвертым входом пятого формирователя и с третьим входом шестого формирователя, выход первого инвертора соединен со вторым входом шестой схемы И, выход которой соединен с вторым входом третьего формирователя, выход схемы формирования соединен с шестым входом четвертого формирователя, с третьим входом пятого формирователя, со вторым входом шестого формирователя и с вторым входом седьмой схемы И, выход которой соединен с третьим входом третьего формирователя, выход третьего формирователя соединен со вторым входом третьей схемы ИЛИ, первый вход третьей схемы И соединен с выходом третьей схемы ИЛИ, второй вход третьей схемы И соединен с выходом второго инвертора, выход третьей схемы И соединен с вторым входом второй схемы ИЛИ, третий вход которой соединен с выходом четвертой схемы И, а выход второй схемы ИЛИ соединен со вторым входом пятой схемы И, выход пятой схемы И является выходом импульса управления задающим генератором, вход второго буфера является входом импульса управления фазовым манипулятором с модуля аналого-цифрового преобразователя, выход второго буфера является выходом импульса управления фазовым манипулятором, второй вход четвертой схемы И соединен с первым входом схемы формирования и является входом импульса запуска второго передатчика с модуля АЦП, восьмой вход четвертого формирователя и первый вход пятого формирователя являются входом сигнала блокировки, выход четвертого формирователя является выходом импульса запуска второго передатчика, выход пятого формирователя является выходом импульс запуска первого передатчика, выход шестого формирователя является выходом импульса бланкирования приемника.

Высокочастотное устройство синхронизации может иметь третий выход, который является выходом импульса контрольной цели, четвертый выход, который является выходом команды включения перезагрузки для модуля аналого-цифрового преобразователя, и четвертый вход, который является входом сигнала блокировки, а низкочастотное устройство синхронизации может иметь второй вход, который является входом сигнала готовности модуля аналого-цифрового преобразователя.

Высокочастотное буферное устройство может иметь шестой выход, который является выходом импульса управления блоками автоматизированного рабочего места радиолокационной станции, при этом низкочастотное буферное устройство содержит третий выход, который является выходом тактовых импульсов синхронизации блоков автоматизированного рабочего места радиолокационной станции.

Сущность изобретения поясняется чертежами.

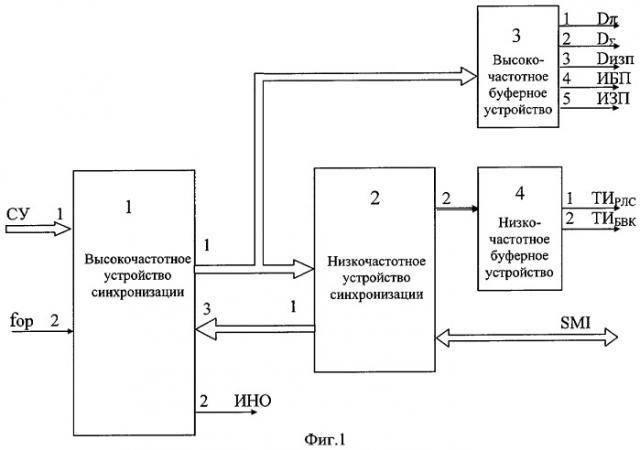

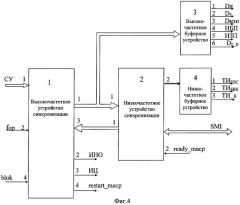

На фиг.1 показана функциональная схема модуля синхронизации, на фиг.2 - функциональная схема низкочастотного устройства синхронизации, на фиг.3 - функциональная схема высокочастотного устройства синхронизации, на фиг.4 - вариант функциональной схемы модуля синхронизации.

Модуль синхронизации содержит (фиг.1) низкочастотное устройство синхронизации 1, высокочастотное устройство синхронизации 2, высокочастотное буферное устройство 3 и низкочастотное буферное устройство 4.

Первый вход высокочастотного устройства синхронизации 1 является входом сигналов управления (СУ), второй вход - входом сигнала опорной частоты (fop), третий вход соединен с первым выходом низкочастотного устройства синхронизации 2.

Первый выход высокочастотного устройства синхронизации 1 соединен с входом низкочастотного устройства синхронизации 2 и с входом высокочастотного буферного устройства 3, а второй его выход является выходом импульсов начала отсчета (ИНО).

Второй выход низкочастотного устройства синхронизации 2 соединен с входом низкочастотного буферного устройства 4, а его двунаправленный вывод соединен с последовательной линией связи SMI (Serial Management Interface).

Первый выход высокочастотного буферного устройства 3 является выходом импульса управления фазовым манипулятором dπ, второй выход является выходом импульса управления задающим генератором DΣ, третий выход является выходом импульса запуска второго передатчика DИЗП, четвертый выход является выходом импульса бланкирования приемника (ИБП), пятый выход является выходом импульса запуска первого передатчика (ИЗП).

Первый выход низкочастотного буферного устройства 4 является выходом тактовых импульсов синхронизации блоков радиолокационной станции (ТИРЛС), второй выход является выходом тактовых импульсов синхронизации модулей вычислительного комплекса (ТИБВК).

А также на фиг.1 показаны следующие обозначения:

dπ, DΣ, ВИЗП, ИБП, ИЗП, ТИРЛС - сигналы, синхронизирующие работу блоков, входящие в состав бортовой радиолокационной станции;

ИНО, ТИБВК - сигналы, синхронизирующие работу модулей, входящие в состав бортовой вычислительного комплекса.

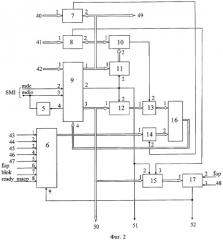

Низкочастотный синхронизатор 2 (фиг.2) содержит первый буфер 5, схему контроля 6, первую схему совпадения 7, вторую схему совпадения 8, устройство связи 9, третью схему совпадения 10, буферный регистр адреса 11, буферный регистр данных 12, первую схему И 13, вторую схему И 14, регистр периода тактового импульса 15, первую схему ИЛИ 16, формирователь тактового импульса 17. При таком построении первый, второй, третий, четвертый и пятый входы схемы контроля 6 являются входами сигналов (43, 44, 45, 46, 47) с высокочастотного устройства синхронизации 1, шестой вход схемы контроля 6 является входом опорной сигнала частоты (fop), седьмой вход схемы контроля 6 является входом сигнала блокировки (blok), восьмой вход схемы контроля 6 является входом сигнала готовности модуля АЦП (ready_macp), девятый вход схемы контроля 6 соединен с выходом формирователя тактового импульса 17, который и является выходом тактового импульса (ti) 52, выход схемы контроля 6 соединен с первым входом второй схемы И 14.

Первый вход устройства связи 9 является входом ключа 42, второй mdc и третий (mdio) входы устройства связи 9 являются входами последовательной линии связи SMI, четвертый вход устройства связи 9 соединен с выходом первой схемы ИЛИ 16. Первый выход устройства связи 9 соединен с первым входом буферного регистра адреса 11, с первым входом третьей схемы совпадения 10, со вторым входом второй схемы совпадения 8, со вторым входом первой схемы совпадения 7 и является выходом адреса регистров синхронизатора (a_syn) 49. Второй выход устройства связи 9 соединен со вторым входом буферного регистра адреса 11, со вторым входом буферного регистра данных 12, со вторым входом регистра периода тактового импульса 15 и является выходом сигнала записи данных zpd_syn 51. Третий выход устройства связи 9 соединен с первым входом буферного регистра данных 12, с первым входом регистра периода тактовых импульсов 15 и является выходом данных (d_syn 50). Четвертый выход устройства связи 9 соединен с входом первого буфера 5. Выход первого буфера 5 соединен с третьим входом устройства связи 9.

Первый вход первой схемы совпадения 7 является входом адреса слова «исправность» 40, а выход соединен со вторым входом второй схемы И 14. Первый вход второй схемы совпадения 8 является входом адреса периода тактового импульса (ti) 41, а выход соединен с третьим входом регистра периода тактового импульса 15. Второй вход третьей схемы совпадения 10 соединен с выходом буферного регистра адреса 11, а выход соединен с вторым входом первой схемы И 13. Выход буферного регистра данных 12 соединен с первым входом первой схемы И 13, выход которой соединен с первым входом схемы ИЛИ 16. Выход второй схемы И 14 соединен со вторым входом первой схемы ИЛИ 16. Выход регистра периода тактового импульса 15 соединен с первым входом формирователя тактового импульса 17, второй вход которого является входом сигнала опорной частоты (fop), a третий вход является входом сигнала переднего фронта тактового импульса (ipf_ti)48.

А также на фиг.2 показаны следующие обозначения:

43 - сигнал управления задающим генератором DΣi;

44 - сигнал управления фазовым манипулятором Dπi;

45 - сигнал управления импульсом запуска второго передатчика DИЗПi;

46 - импульс запуска первого передатчика ИЗПi;

47 - импульс бланкирования приемника ИБГПi.

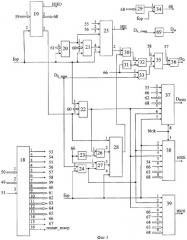

Высокочастотное устройство синхронизации 1 (фиг.3) содержит блок буферных регистров 18, первый формирователь 19, который является формирователем периода сигналов синхронизации, схему задержки 20, которая является схемой задержки импульса цели, первую схему длительности 21, которая является схемой длительности импульса цели, вторую схему длительности 22, которая является схемой длительности сигналов синхронизации, первый инвертор 23, схему формирования 24, которая является схемой формирования заднего фронта сигнала управления задающим генератором (DΣI), второй формирователь 25, который является формирователем импульса цели, шестую схему И 26, седьмую схему И 27, третий формирователь 28, который является формирователем сигнала управления задающим генератором (dΣI), схему сравнения 29, третью схему ИЛИ 30, второй инвертор 31, третью схему И 32, четвертую схему И 33, седьмой формирователь 34, который является формирователем сигнала переднего фронта тактового импульса (ipf_ti), вторую схему ИЛИ 35, пятую схему И 36, четвертый формирователь 37, который является формирователем импульса запуска второго передатчика (DИЗПi), пятый формирователь 38, который является формирователем импульса запуска первого передатчика (ИЗПi), шестой формирователь 39, который является формирователем импульса бланкирования приемника (ИБПi), и второй буфер 69.

Первый вход блока буферных регистров 18 является входом данных (d_syn 50), второй вход блока буферных регистров 18 является входом адреса регистров синхронизатора (a_syn 49), третий вход блока буферных регистров 18 является входом сигнала записи данных (zpd_syn) 51.

Первый выход блока буферных регистров 18 соединен с первым входом четвертого формирователя 37. Второй выход блока буферных регистров 18 соединен с пятым входом пятого формирователя 38. Третий выход блока буферных регистров 18 соединен с первым входом второго формирователя 25. Четвертый выход блока буферных регистров 18 соединен с вторым входом второго формирователя 25. Пятый выход блока буферных регистров 18 соединен с первым входом пятой схемы И 36. Шестой выход блока буферных регистров 18 соединен с первым входом второй схемы ИЛИ 35. Седьмой выход блока буферных регистров 18 соединен с первым входом первого формирователя 19. Восьмой выход блока буферных регистров 18 соединен с вторым входом первой схемы длительности 21 и со вторым входом второй схемы длительности 22. Девятый выход блока буферных регистров 18 соединен с первым входом схемы задержки 20. Десятый выход блока буферных регистров 18 соединен с третьим входом четвертого формирователя 37. Одиннадцатый выход блока буферных регистров 18 соединен с седьмым входом пятого формирователя 38. Двенадцатый выход блока буферных регистров 18 соединен с шестым входом шестого формирователя 39. Тринадцатый выход блока буферных регистров 18 соединен с седьмым входом шестого формирователя 39. Четырнадцатый выход блока буферных регистров 18 соединен с входом первого инвертора 23, с первым входом седьмой схемы И 27, с первым входом четвертой схемы И 33, с входом второго инвертора 31, с вторым входом четвертого формирователя 37, с шестым входом пятого формирователя 38 и с четвертым входом шестого формирователя 39.

Пятнадцатый выход блока буферных регистров 18 соединен с пятым входом шестого формирователя 39.

Шестнадцатый выход блока буферных регистров 18 является выходом команды включения перезагрузки модуля аналого-цифрового преобразователя (restart_macp).

Второй вход первого формирователя 19, второй вход первой схемы задержки 20, третий вход первой схемы длительности 21, пятый вход второго формирователя 25, второй вход седьмого формирователя 34, первый вход второй схемы длительности 22, второй вход схемы формирования 24, четвертый вход третьего формирователя 28, седьмой вход четвертого формирователя сигнала 37, второй вход пятого формирователя 38 и первый вход шестого формирователя 39 соединены с входом сигнала опорной частоты (fop).

Первый выход первого формирователя 19 является выходом импульса начала отсчета (ИНО). Второй выход первого формирователя 19 соединен с входом схемы сравнения 29, с четвертым входом четвертого формирователя 37, с восьмым входом пятого формирователя 38 и с восьмым входом шестого формирователя 39.

Третий выход первого формирователя 19 соединен с третьим входом второй схемы длительности 22 и с первым входом третьего формирователя 28. Выход схемы сравнения 29 соединен с первым входом седьмого формирователя 34, выход которого является выходом сигнала переднего фронта тактового импульса (ipf_ti).

Выход первой схемы задержки 20 соединен с первым входом первой схемы длительности 21 и с третьим входом второго формирователя 25. Первый выход второго формирователя 25 является выходом импульса контрольной цели (ИЦ), а второй выход соединен с первым входом третьей схемы ИЛИ 30. Выход первой схемы длительности 21 соединен с четвертым входом второго формирователя 25.

Выход второй схемы длительности 22 соединен с первым входом шестой схемы И 26, с пятым входом четвертого формирователя 37, с четвертым входом пятого формирователя 38 и с третьим входом шестого формирователя 39.

Выход первого инвертора 23 соединен со вторым входом шестой схемы И 26, выход которой соединен со вторым входом третьего формирователя 28. Выход схемы формирования 24 соединен с шестым входом четвертого формирователя 37, с третьим входом пятого формирователя 38, со вторым входом шестого формирователя 39 и со вторым входом седьмой схемы И 27, выход которой соединен с третьим входом третьего формирователя 28. Выход третьего формирователя 28 соединен со вторым входом третьей схемы ИЛИ 30. Первый вход третьей схемы И 32 соединен с выходом третьей схемы ИЛИ 30. Второй вход третьей схемы И 32 соединен с выходом второго инвертора 31. Выход третьей схемы И 32 соединен с вторым входом второй схемы ИЛИ 35, третий вход которой соединен с выходом четвертой схемы И 33. Выход второй схемы ИЛИ 35 соединен со вторым входом пятой схемы И 36. Выход пятой схемы И 36 является выходом импульса управления задающим генератором DΣi.

Вход второго буфера 69 является входом импульса управления фазовым манипулятором с модуля аналого-цифрового преобразователя (Dπmacp). Выход второго буфера 69 является выходом импульса управления фазовым манипулятором (Dπi).

Второй вход четвертой схемы И 33 соединен с первым входом схемы формирования 24 и является входом импульса запуска второго передатчика с модуля АЦП.

Восьмой вход четвертого формирователя 37 и первый вход пятого формирователя 38 являются входом сигнала блокировки (blok). Выход четвертого формирователя 37 является выходом импульса запуска второго передатчика (DИЗПi). Выход пятого формирователя 38 является выходом импульса запуска первого передатчика (ИЗПi). Выход шестого формирователя 39 является выходом импульса бланкирования приемника (ИБПi).

А также на фиг.3 показаны следующие обозначения:

53 - команда включения импульса запуска второго передатчика (vkl_dizp).

54 - команда включения импульса запуска первого передатчика (vkl_izp);

55 - команда включения автономного контроля (vkl_ak);

56 - команда включения сквозного контроля (vkl_skv);

57 - команда включения сигнала управления задающим генератором (vkl_dΣ);

58 - команда включения непрерывной генерации (vkl_ng);

59 - код периода повторения импульса запуска передатчика (tp);

60 - код длительности (dlit_glad);

61 - код задержки контрольной цели (zkc);

62 - код опережения переднего фронта импульса запуска второго передатчика относительно переднего фронта сигнала DΣi (pfdizp);

63 - код опережения переднего фронта импульса запуска первого передатчика относительно переднего фронта сигнала DΣi (pfizp);

64 - код опережения переднего фронта импульса бланкирования приемника относительно переднего фронта сигнала DΣi (pfibp);

65 - код задержки заднего фронта импульса бланкирования приемника DΣi (zfibp);

66 - команда включения фазово-кодовой манипуляции зондирующего сигнала (vkl_fkm);

67 - команда отключения импульса бланкирования приемника (otkl_ibp);

68 - выходной код формирователя периода сигналов синхронизации (st_tp).

Высокочастотное устройство синхронизации 1 (фиг.4) может содержать третий выход, который является выходом импульса контрольной цели (ИЦ), четвертый выход, который является выходом команды включения перезагрузки модуля АЦП (restart_macp), четвертый вход, который является входом сигнала блокировки модуля синхронизации (blok). Низкочастотное устройство синхронизации 2 может содержать второй вход, который является входом сигнала готовности модуля АЦП (ready_macp).

Высокочастотное буферное устройство 3 может содержать шестой выход, который является выходом импульса управления блоками автоматизированного рабочего места радиолокационной станции (DΣK), при этом низкочастотное буферное устройство 4 может содержать третий выход, который является выходом тактовых импульсов синхронизации блоков автоматизированного рабочего места радиолокационной станции ТИ_к.

ИЦ, ready_macp, restart_macp, blok - сигналы, синхронизирующие работу модулей, входящие в состав бортового вычислительного комплекса.

DΣK, ТИ_к - сигналы, синхронизирующие работу блоков, входящие в состав автоматизированного рабочего места БРЛС.

Как видно из описания схемы, в модуле синхронизации формируются сигналы управления передающим устройством БРЛС:

- импульс запуска первого передатчика ИЗП;

- импульс запуска второго передатчика DИЗП;

- импульс управления задающим генератором DΣ;

- сигнал управления фазовым манипулятором dπ,

- сигнал ИБП - импульс бланкирования СВЧ-приемника, а также:

- сигнал ИНО - импульс начала отсчета;

- сигнал ИЦ - импульс контрольной цели;

- сигнал ТИРЛС - тактовый импульс синхронизации блоков БРЛС;

- сигнал ТИБВК - тактовый импульс синхронизации модулей БВК;

- сигнал ТИ_к - тактовый импульс синхронизации блоков, входящих в состав автоматизированного рабочего места БРЛС;

- сигнал DΣК - сигнал для синхронизации блоков, входящих в состав автоматизированного рабочего места БРЛС;

- сигнал restart_macp - команда включения перезагрузки модуля АЦП;

- сигнал ready_macp - сигнал готовности модуля АЦП;

- сигнал blok - команда блокировки модуля синхронизации.

Работает модуль синхронизации следующим образом.

Сигналы управления (СУ) на фиг.1 поступают на первый вход высокочастотного устройства синхронизации 1 с модуля аналого-цифрового преобразователя (АЦП), не показанного на схеме. В качестве сигнала опорной частоты (fop) используется сигнал с частотой 56 МГц, поступающий с задающего генератора БРЛС на второй вход высокочастотного устройства синхронизации 1. Управление работой модуля синхронизации производится по магистрали SMI. Обмен информацией по интерфейсу SMI производится в соответствии с таблицей обмена по двунаправленному выводу низкочастотного устройства синхронизации 2.

С модуля АЦП поступают сигналы управления DΣ_macp и Dπ_macp (фиг.3), из которых в высокочастотном устройстве синхронизации 1 формируются: сигнал управления задающим генератором DΣ и сигнал управления фазовым манипулятором Dπ. В низкочастотном устройстве синхронизации 2 (фиг.2) формируются: адрес регистров синхронизатора (a_syn), данные (d_syn) и сигнал записи данных (zpd_syn), которые поступают с первого выхода на третий вход высокочастотного устройства синхронизации 1. Со второго выхода низкочастотного устройства синхронизации 2 тактовые импульсы поступают на вход низкочастотного буферного устройства 3, где формируются: тактовый импульс синхронизации блоков БРЛС - первый выход, тактовый импульс синхронизации модулей БВК - второй выход и тактовый импульс синхронизации блоков АРМ БРЛС - третий выход.

Высокочастотное устройство синхронизации 1 в соответствии с кодами адреса и данных, поступающими на третий вход, формирует: импульс начала отсчета, который поступает на второй выход, импульс цели - третий выход, команду перезагрузки модуля АЦП - четвертый выход и высокочастотные сигналы синхронизации - первый выход, которые поступают на первый вход низкочастотного устройства синхронизации 2 и на вход высокочастотного буферного устройства 3.

Высокочастотное буферное устройство 3 формирует: сигнал управления фазовым манипулятором - первый выход, сигнал управления задающим генератором - второй выход, импульс запуска второго передатчика - третий выход, импульс бланкирования приемника - четвертый выход, импульс запуска первого передатчика - пятый выход и сигнал синхронизации блоков АРМ БРЛС - шестой выход. При поступлении сигнала блокировки (blok) на третий вход высокочастотного устройства синхронизации 1 сигналы управления передатчиком не формируются. Сигналы, поступающие на первый вход низкочастотного устройства синхронизации 2, и сигнал готовности модуля АЦП - ready_macp, поступающий на второй вход низкочастотного устройства синхронизации, используются для организации встроенного контроля.

Низкочастотное устройство синхронизации (фиг.2) работает следующим образом.

На вход устройства связи 9 из модуля центрального процессора по шине SMI поступают управляющие коды и команды. Интерфейс SMI представляет собой последовательную синхронную трехпроводную шину (сигналы mdc, mdio и шина GND), обеспечивающую доступ по записи и чтению к 16-разрядным регистрам устройств. Информация по шине SMI передается 32-разрядными словами, содержащими служебные биты, определяющие направление передачи данных, 5-разрядный адрес ведомого устройства, 5-разрядный адрес регистра и 16-разрядные данные. В устройстве связи 9 производится преобразование входных последовательных кодов в параллельные и их дешифрация: определение направления передачи данных (запись данных в регистры модуля синхронизации или чтение данных из модуля) и сравнение принятого адреса ведомого устройства с ключевым кодом модуля (первый вход). В режиме записи данных из устройства связи 9 выдаются коды адресов регистров (первый выход), коды данных (третий выход) и сигнал записи данных (второй выход), который формируется только при совпадении принятого адреса ведомого устройства с ключевым кодом модуля. В режиме чтения данных из устройства связи 9 выдаются коды адресов регистров, затем производится преобразование параллельного кода, поступающего на четвертый вход устройства связи 9, в последовательный код и выдача его в шину SMI через буферный каскад с открытым коллектором (первый буфер 5). Все коды адреса и данных, поступающие из устройства связи 9, записываются в буферные регистры адреса 11 и данных 12. Благодаря этому, если после записи данных будет произведено чтение данных по этому же адресу, на выходе третьей схемы совпадения 10 сформируется сигнал, который откроет схему первую схему И 13 и на четвертый вход устройства связи 9 через первую схему ИЛИ 16 поступят последние записанные данные. Таким образом производится контроль исправности шины SMI.

При совпадении принятого кода адреса регистров синхронизатора с адресом слова исправности на выходе первой схемы совпадения 7 сформируется сигнал, который откроет вторую схему И 14, и на четвертый вход устройства связи 9 через первую схему ИЛИ 16 поступят данные из схемы контроля 6.

При совпадении принятого кода адреса регистров с адресом периода тактового импульса на выходе схемы совпадения 8 сформируется сигнал, который разрешит запись данных в регистр периода тактового импульса 15. Формирователь тактового импульса 17 представляет собой вычитающий счетчик.

Если принятый код периода равен нулю, на вход данных счетчика поступит фиксированный код, определяющий значение периода тактового импульса 10,24 мс, а на тактовый вход - сигнал fop. Если принятый код периода не равен нулю, на вход данных счетчика поступит код из регистра периода тактового импульса 15, а на тактовый вход - сигнал 48 (ipf_ti) из высокочастотного устройства синхронизации 1. В этом случае период повторения тактового импульса будет определяться периодом повторения зондирующих сигналов.

В схеме контроля 6 производится контроль наличия сигналов, формируемых модулем синхронизации. Схема контроля 6 контролирует наличие каждого из сигналов представляет собой D-триггер по каждому сигналу, который устанавливается в состояние логической единицы фронтом данного сигнала и сбрасывается тактовым импульсом, задержанным на два периода сигнала опорной частоты (fop). Сигналы с выходов триггеров записываются в соответствующие разряды выходного