Комбинационно-накапливающий сумматор

Иллюстрации

Показать всеИспользование: в цифровой вычислительной технике. Технический результат - расширение функциональных возможностей при минимальных затратах оборудования. Сумматор выполняет операции сложения, сдвига кода влево и вправо, инвертирования, сложения по модулю два, логического сложения, умножения. Каждый разряд сумматора содержит два RS-триггера, девять элементов И, пять элементов ИЛИ, пять элементов НЕ, восемь шин управления и информационный вход. Особенностью сумматора является построение каждого разряда только на основе двух RS-триггеров и новые схемы выполнения дополнительных операций. Суммарное число входов логических элементов одного разряда равно 36, в среднем на одну выполняемую операцию требуется около 5 входов (цена Квайна). 1 ил., 1 табл.

Реферат

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики. Известно суммирующее устройство, выполненное на основе логических элементов И, ИЛИ, НЕ, содержащее в каждом разряде три RS-триггера, девять элементов И, четыре элемента ИЛИ, один элемент НЕ и три шины управления (см. а.с. №1264165 A1, SU G06F 7/50). Недостатком этого объекта является наличие трех триггерных регистров, что определяет время выполнения операции сложения, объем оборудования, потребление электроэнергии и стоимость устройства в целом. Наиболее близким, принятым за прототип, является объект по а.с. 12624179 SU. Он устраняет ряд недостатков, присущих объекту по а.с. 1264165 SU, т.к. содержит только два RS-триггера в каждом разряде, семь элементов И, три элемента ИЛИ, два элемента НЕ и две шины управления. Однако и прототип имеет ряд недостатков, которые мешают его широкому применению. Основным недостатком является одна выполняемая арифметическая операция (сложение).

Задачей изобретения является расширение перечня выполняемых операций при минимальных затратах аппаратных средств. Для этого предложен объект, выполненный на основе элементов И, ИЛИ, НЕ, отличающийся тем, что содержит в каждом разряде информационный вход, восемь шин управления, девять элементов И, пять элементов ИЛИ, пять элементов НЕ, два RS-триггера, при этом информационный вход соединен с S-входом первого RS-триггера, единичный выход которого соединен с первыми входами четвертого и восьмого элементов И и четвертого элемента ИЛИ, первый вход третьего элемента И связан с нулевым выходом упомянутого триггера, второй вход третьего элемента И соединен с входом первого элемента НЕ, с первым входом пятого элемента ИЛИ и с входом переноса из младшего разряда, выход первого элемента НЕ подключен ко второму входу четвертого элемента И, выходы третьего и четвертого элементов И соединены с первым и вторым входами первого элемента ИЛИ, третий вход которого подключен к третьей шине управления, выход упомянутого элемента связан со вторыми входами пятого и шестого элементов И, первые входы этих элементов подключены к четвертой шине управления, третьи входы этих элементов И подключены к входу и выходу второго элемента НЕ соответственно, выход пятого элемента И соединен с входом третьего элемента НЕ и с первым входом третьего элемента ИЛИ, второй вход которого связан с единичным выходом второго RS-триггера, а выход этого элемента ИЛИ соединен с первым входом седьмого элемента И, выход третьего элемента НЕ соединен с R-входом второго RS-триггера, выход шестого элемента И через четвертый элемент НЕ связан с S-входом упомянутого триггера и со вторым входом седьмого элемента И, выход которого соединен со вторыми входами четвертого элемента ИЛИ, восьмого элемента И и с входом пятого элемента НЕ, выход пятого элемента НЕ соединен с первыми входами первого элемента И младшего разряда и второго элемента И старшего разряда, третий вход восьмого элемента И связан с седьмой шиной управления, а его выход подключен ко второму входу пятого элемента ИЛИ и к четвертому входу второго элемента ИЛИ, выход которого соединен с входом второго элемента НЕ, выходы четвертого и пятого элементов ИЛИ связаны с первым и вторым входами девятого элемента И, его третий вход связан с шестой шиной управления, а его выход соединен с первым входом второго элемента ИЛИ и является выходом переноса в старший разряд, вторые входы первого и второго элементов И соединены со второй и первой шинами управления, выходы упомянутых элементов И соединены со вторым и третьим входами второго элемента ИЛИ, кроме того, пятая и восьмая шины соединены с третьими входами четвертого и пятого элементов ИЛИ соответственно.

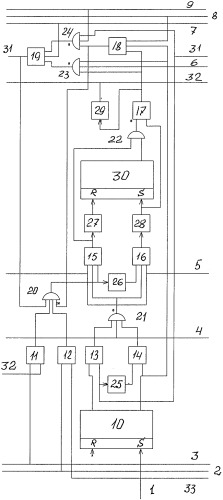

Предлагаемый объект позволяет выполнить семь операций (сложение, сдвиг влево, сдвиг вправо, инвертирование, сложение по модулю два, логическое сложение и логическое умножение) при минимальных затратах дополнительного оборудования. Для пояснения работы на чертеже приведена функциональная схема одного разряда объекта. Каждый разряд объекта содержит информационный вход 1, шину управления (ШУ) сдвигом влево - 2, ШУ сдвигом вправо - 3, ШУ операцией инвертирования - 4, шину исполнительных (тактирующих) импульсов - 5, ШУ логического умножения - 6, шину гашения переноса - 7, ШУ при сдвигах кодов - 8, вторую ШУ операцией инвертирования кода триггера - 9, RS-триггеры - 10, 30, элементы И - 11-19, элементы ИЛИ - 20-24, элементы НЕ - 25-29, вход переноса из младшего разряда - 31, вход управления (ВУ) элементом И 11 младшего разряда при сдвиге вправо - 32, ВУ элементом И 12 при сдвиге влево - 33.

Рассмотрим работу объекта при выполнении арифметических и логических операций. В исходном положении на всех шинах управления, кроме ШУ 7, 8, отсутствуют высокие потенциалы. С выходов элементов НЕ 25-29 на соответствующие элементы поступают высокие потенциалы. Будем считать, что до начала выполнения операции первое слагаемое хранится в триггерах 30, а второе слагаемое по первому временному такту (t1) принимается в триггеры 10.

1. Операция сложения. Одновременно с приемом второго слагаемого на ШУ 7 подается потенциал, разрешающий распространение переноса в старшие разряды. По второму временному такту (t2) производится формирование поразрядного и сквозного переносов во всех разрядах объекта в соответствии с следующими логическими соотношениями

Здесь Ai, Вi - значения первого и второго слагаемых i-ого разряда;

Рi - сигнал переноса, выработанный в i-ом разряде;

Рi-1 - сигнал переноса, выработанный в i-1-ом разряде;

Максимальная временная задержка сигнала в цепи переноса равняется 2nτ (n - число разрядов объекта, τ - временная задержка сигнала на одном элементе И, ИЛИ). По истечении этого времени по t3 на ШУ 5 подается исполнительный импульс, который поступает на третьи входы И 15, 16 одновременно и заносит в триггер 30 результат суммирования двух чисел. Другими словами, вместо первого слагаемого будет занесена сумма двух слагаемых. Переключение (инвертирование) триггера 30 будет осуществляться в соответствии со следующим соотношением значений слагаемых, приведенных в таблице 1.

- знак операции сложения по модулю 2.

Варианты значения кодов исходных данных разряда и выработанных Рi и Si приведены в таблице 1.

| Таблица 1 | ||||||

| Ai | Bi | Pi-1 | Si (Ai) | Pi | Примечание | |

| 1 | 0 | 0 | 0 | 0 | 0 | Сохраняется значение Ai |

| 2 | 1 | 0 | 0 | 1 | 0 | Сохраняется значение Ai |

| 3 | 0 | 1 | 0 | 1 | 0 | Инвертируется Ai |

| 4 | 0 | 0 | 1 | 1 | 0 | Инвертируется Ai |

| 5 | 1 | 1 | 0 | 0 | 1 | Инвертируется Ai |

| 6 | 0 | 1 | 1 | 0 | 1 | Сохраняется значение Ai |

| 7 | 1 | 0 | 1 | 0 | 1 | Инвертируется Ai |

| 8 | 1 | 1 | 1 | 1 | 1 | Сохраняется значение Ai |

Отметим особенности работы объекта при выполнении операции сложения. При поступлении импульса на "единичный" вход триггера 30 этот же сигнал запрещает возможную выработку ложного сигнала переноса путем запрета И 17 по второму его входу. Разрешение формирования переноса будет возможно только после окончания исполнительного импульса, поступившего по цепи ШУ 5, И 16, НЕ 28. При поступлении счетного импульса на "нулевой" вход триггера 30 этот же сигнал "поддерживает" значение кода триггера, равного "единице", за счет прохождения импульса по цепи И 15, ИЛИ 22, И 17 до окончания этого импульса.

2. Операция инвертирования кода. Для выполнения этой операции на ШУ 4 и 9 подаются потенциалы, являющиеся признаками этой операции. Если в триггере i-ого разряда хранится код "единицы", то потенциал с ШУ 9, через ИЛИ 24, И 19 поступит на первый вход И 20 и далее на выходы И 15, НЕ 26. Потенциал ШУ 4, через ИЛИ 21 поступит на вторые входы И 15, 16. Исполнительный импульс t1 подается на ШУ 5, далее через И 15, НЕ 27 поступает на "нулевой" вход триггера 30. Если же в триггере хранится "нулевой" код, то исполнительный импульс по цепи ШУ 5, И 16, НЕ 28 поступает на "единичный" вход триггера 30. Т.о. код регистра первого слагаемого будет проинвертирован.

3. Операция сдвига кода вправо. Для выполнения операции с ШУ 8 и 7 снимаются, а на ШУ 3, 4 подаются управляющие потенциалы, которые является признаками этой операции и присутствуют на время выполнения всей операции. При этом, если в i-ом разряде хранится код "единицы", то низкий потенциал с выхода НЕ 29 поступит по входу 32 на вход И 11, i-1-го разряда. На выходе НЕ 26, входе И 16 будут высокие потенциалы. Исполнительный импульс, поступивший на ШУ 5, установит триггер 30 i-ого разряда в нуль, (если в i+1-ом хранился код нуля) и установит триггер i-1-го разряда в единицу. Последовательность импульсов, поступающих на ШУ 5, будет сдвигать код числа вправо. При этом значение потенциала с выхода И 17 не будет изменяться даже при переключении триггера в данном разряде, т.к. связи с И 15, ИЛИ 22, И 17 будут "поддерживать" значение сигнала с И 17 неизменным до окончания действия импульса сдвига.

4. Операция сдвига кода влево. Эта операция выполняется аналогично операции сдвига кода вправо. Отличие состоит в том, что управляющий потенциал поступает на ШУ 2 и в работе участвует И 12, вместо элемента ИИ. Операция выполняется за два временных такта при сдвиге кода на один разряд и требует дополнительно трех входов элементов И 11, ИЛИ 20 и ШУ 2.

5. Операция сложения по модулю два. Операция выполняется за один временной такт и требует в каждом разряде объекта одного входа ИЛИ 20, дополнительного оборудования. Для ее выполнения запрещается распространение потенциала переноса из разряда в разряд за счет снятия управляющего потенциала с ШУ 7.

6. Операция логического сложения. Для выполнения этой операции с ШУ 8 снимается высокий потенциал, что обеспечивает поступление с выхода НЕ 26 разрешающего потенциала на вход И 16. Исполнительный импульс по цепи ШУ 5, И 16, НЕ 8 поступит на S-вход триггера 30 и установит его в единицу, если в триггере 10 хранится код единицы и потенциал по цепи И 14, ИЛИ 21 поступает на второй вход И 16. Операция выполняется за один временной такт и требует только одного входа элемента И 8 и ШУ 8.

7. Операция логического умножения. Для выполнения этой операции на ШУ 6, 7 и 9 подаются высокие потенциалы, что формирует на выходе И 19 всех разрядов высокий потенциал, который через ИЛИ 20 поступает на первый вход И 15 и вход НЕ 26. Если код второго сомножителя i-ого разряда равен нулю, то высокий потенциал, поступивший по входу 31 из младшего разряда, по цепи И 13, ИЛИ 21 поступит на вторые входы И 15, 16. Исполнительный импульс по цепи ШУ 5, И 15, НЕ 27 поступит на R-вход триггера 30 и установит его в нуль. Если код второго сомножителя, хранящегося в триггере 10, равен единице, то состояние триггера 30 не меняется. Операция выполняется за один временной такт и требует дополнительно только одного входа элемента ИЛИ 23 и ШУ 6.

Таким образом, предложенный объект позволяет расширить перечень выполняемых операций с одной операции до семи (инвертирование, сдвиг влево, сдвиг вправо, сложение по модулю два, логическое сложение и логическое умножение) при минимальных затратах оборудования.

Комбинационно-накапливающий сумматор, выполненный на логических элементах И, ИЛИ, НЕ, отличающийся тем, что содержит в каждом разряде информационный вход, восемь шин управления, девять элементов И, пять элементов ИЛИ, пять элементов НЕ, два RS-тригтера, при этом информационный вход соединен с S-входом первого RS-триггера, единичный выход которого соединен с первыми входами четвертого и восьмого элементов И и четвертого элемента ИЛИ, первый вход третьего элемента И связан с нулевым выходом упомянутого триггера, второй вход третьего элемента И соединен с входом первого элемента НЕ, с первым входом пятого элемента ИЛИ и с входом переноса из младшего разряда, выход первого элемента НЕ подключен ко второму входу четвертого элемента И, выходы третьего и четвертого элементов И соединены с первым и вторым входами первого элемента ИЛИ, третий вход которого подключен к третьей шине управления, выход упомянутого элемента связан со вторыми входами пятого и шестого элементов И, первые входы этих элементов подключены к четвертой шине управления, третьи входы этих элементов И подключены к входу и выходу второго элемента НЕ соответственно, выход пятого элемента И соединен с входом третьего элемента НЕ и с первым входом третьего элемента ИЛИ, второй вход которого связан с единичным выходом второго RS-триггера, а выход этого элемента ИЛИ соединен с первым входом седьмого элемента И, выход третьего элемента НЕ соединен с R-входом второго RS-триггера, выход шестого элемента И через четвертый элемент НЕ связан с S-входом упомянутого триггера и со вторым входом седьмого элемента И, выход которого соединен со вторыми входами четвертого элемента ИЛИ, восьмого элемента И и с входом пятого элемента НЕ, выход пятого элемента НЕ соединен с первыми входами первого элемента И младшего разряда и второго элемента И старшего разряда, третий вход восьмого элемента И связан с седьмой шиной управления, а его выход подключен ко второму входу пятого элемента ИЛИ и к четвертому входу второго элемента ИЛИ, выход которого соединен с входом второго элемента НЕ, выходы четвертого и пятого элементов ИЛИ связаны с первым и вторым входами девятого элемента И, его третий вход связан с шестой шиной управления, а его выход соединен с первым входом второго элемента ИЛИ и является выходом переноса в старший разряд, вторые входы первого и второго элементов И соединены со второй и первой шинами управления, выходы упомянутых элементов И соединены со вторым и третьим входами второго элемента ИЛИ, кроме того, пятая и восьмая шины соединены с третьими входами четвертого и пятого элементов ИЛИ соответственно.