Дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для использования в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в расширении диапазона активной работы. Дифференциальный усилитель (ДУ) содержит входные транзисторы (Т) (1, 2), коллекторы которых объединены и подключены ко входу токового зеркала (ТЗ) (4), а эмиттеры соединены с эмиттерами выходных Т (7) и (8) противоположного типа проводимости через дополнительный Р (13) и вспомогательный Р (5), а также через дополнительный Р (14) и вспомогательный Р (5). Базы выходных Т (7, 8) подключены к выходу (9) ТЗ (4) и токостабилизирующему двухполюснику (10), а их коллекторы соединены с основными выходами (11, 12) ДУ. Базы входных Т (1, 2) подключены к соответствующим базам дополнительных Т (15, 16). Эмиттер Т (15) соединен с общей точкой Р (13) и Р (14), эмиттер Т (16) - с общей точкой Р (14) и Р (6), а коллекторы Т (15, 16) связаны с первым (17) и вторым (18) дополнительными выходами ДУ. 2 з.п. ф-лы, 10 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ) на n-p-n и р-n-р транзисторах с так называемой «архитектурой входного каскада операционного усилителя μА741» [1-30]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с типовым параллельно-балансным каскадом [29-30], стали основным усилительным элементом многих аналоговых интерфейсов. Предлагаемое изобретение относится к данному подклассу устройств.

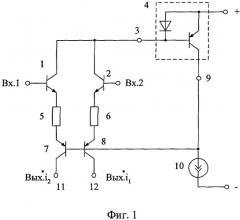

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №3.660.773, а также в [1-14], содержащий первый 1 и второй 2 входные транзисторы, коллекторы которых объединены и подключены ко входу 3 токового зеркала 4, а эмиттеры через первый 5 и второй 6 вспомогательные резисторы соединены с соответствующими эмиттерами первого 7 и второго 8 выходных транзисторов противоположного типа проводимости, причем базы первого 7 и второго 8 выходных транзисторов подключены к выходу 9 токового зеркала 4 и токостабилизирующему двухполюснику 10, а их коллекторы соединены с основными выходами 11 и 12 дифференциального усилителя.

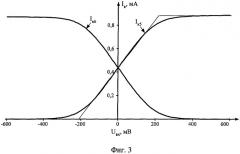

Существенный недостаток известного ДУ состоит в том, что он имеет узкий динамический диапазон линейного усиления сигналов (±Uгр≈100÷150 мВ, фиг.3).

Основная цель предлагаемого изобретения состоит в расширении диапазона активной работы.

Поставленная цель достигается тем, что в дифференциальный усилитель (фиг.1), содержащий первый 1 и второй 2 входные транзисторы, коллекторы которых объединены и подключены ко входу 3 токового зеркала 4, а эмиттеры через первый 5 и второй 6 вспомогательные резисторы соединены с соответствующими эмиттерами первого 7 и второго 8 выходных транзисторов противоположного типа проводимости, причем базы первого 7 и второго 8 выходных транзисторов подключены к выходу 9 токового зеркала 4 и токостабилизирующему двухполюснику 10, а их коллекторы соединены с основными выходами 11 и 12 дифференциального усилителя, вводятся новые элементы и связи - эмиттеры первого 1 и второго 2 входных транзисторов соединены с первым 5 и вторым 6 вспомогательными резисторами через соответствующие первый 13 и второй 14 дополнительные резисторы, причем базы первого 1 и второго 2 входных транзисторов подключены к соответствующим базам первого 15 и второго 16 дополнительных транзисторов, эмиттер первого дополнительного резистора 15 соединен с общей точкой первого вспомогательного 5 и первого дополнительного 13 резисторов, эмиттер второго 16 дополнительного транзистора связан с общей точкой второго вспомогательного 6 и второго дополнительного 14 резисторов, а коллекторы первого 15 и второго 16 дополнительных транзисторов связаны с первым 17 и вторым 18 дополнительными выходами дифференциального усилителя.

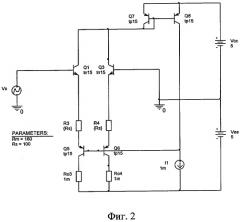

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в среде компьютерного моделирования PSpice. На фиг.3 показана проходная характеристика ДУ фиг.2.

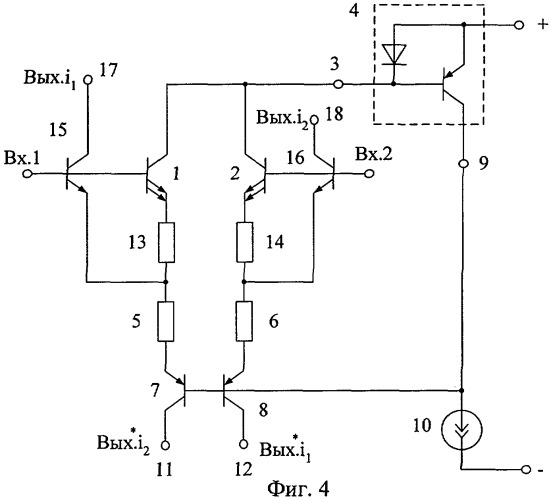

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.4.

На фиг.5 показаны токи и напряжения в заявляемом ДУ, а также его теоретическая проходная характеристика.

Частные варианты построения заявляемого устройства в соответствии с п.3 формулы изобретения изображены на фиг.6, 7.

Схема включения заявляемого устройства (фиг.3) в структуре быстродействующего операционного усилителя изображена на фиг.8.

На фиг.9 показана схема заявляемого устройства в среде компьютерного моделирования PSpice, а на фиг.10 - проходные характеристики ДУ фиг.9, где Iк1, Iк3, Iк5, Iк6 - коллекторные токи транзисторов Q1, Q3, Q5, Q6 схемы фиг.9 при R3=R4=100 Ом; коллекторные токи транзисторов Q1, Q3, Q5, Q6 схемы фиг.9 при R3=R4=200 Ом.

Дифференциальный усилитель (фиг.4) содержит первый 1 и второй 2 входные транзисторы, коллекторы которых объединены и подключены ко входу 3 токового зеркала 4, а эмиттеры через первый 5 и второй 6 вспомогательные резисторы соединены с соответствующими эмиттерами первого 7 и второго 8 выходных транзисторов противоположного типа проводимости, причем базы первого 7 и второго 8 выходных транзисторов подключены к выходу 9 токового зеркала 4 и токостабилизирующему двухполюснику 10, а их коллекторы соединены с основными выходами 11 и 12 дифференциального усилителя. Эмиттеры первого 1 и второго 2 входных транзисторов соединены с первым 5 и вторым 6 вспомогательными резисторами через соответствующие первый 13 и второй 14 дополнительные резисторы, причем базы первого 1 и второго 2 входных транзисторов подключены к соответствующим базам первого 15 и второго 16 дополнительных транзисторов, эмиттер первого дополнительного резистора 15 соединен с общей точкой первого вспомогательного 5 и первого дополнительного 13 резисторов, эмиттер второго 16 дополнительного транзистора связан с общей точкой второго вспомогательного 6 и второго дополнительного 14 резисторов, а коллекторы первого 15 и второго 16 дополнительных транзисторов связаны с первым 17 и вторым 18 дополнительными выходами дифференциального усилителя.

В дифференциальном усилителе (фиг.6, 7) в качестве первого 1 и второго 2 входных транзисторов применены полевые транзисторы, затворы которых соответствуют базам, стоки - коллекторам, истоки - эмиттерам первого 1 и второго 2 входных транзисторов.

Рассмотрим работу заявляемого ДУ (фиг.5). В статическом режиме коллекторные токи транзисторов

Iк1≈Iк15, Iк2≈Iк16, Iк1≈Iк2.

Такой режим обеспечивается за счет разницы в площадях эмиттерных переходов транзисторов 1 и 15, 2 и 16, а также соответствующего выбора резисторов R13=R14=80÷200 Ом.

За счет отрицательной обратной связи в схеме устанавливаются статические токи, зависящие от источника тока 10

Iк1+Iк2=Iк10, Iэ8=Iк2+Iк16, Iэ7=Iк15+Iк1.

Если на вход Вх.1 подать напряжение uвх, то коллекторные токи транзисторов 2 и 16 начнут уменьшаться, а транзисторов 1 и 15 - увеличиваться. Однако практически все приращение тока через резистор 5 будет передаваться в эмиттер транзистора 15, а отношение приращений Как следствие, отрицательная обратная связь "база транзисторов 7, 8 - вход 3 - выход 9" будет стабилизировать ток коллектора транзистора 2 и поэтому напряжение между базой транзистора 7 и общей шиной uδ7=Uconst≈const. Как следствие, практически все входное напряжение ДУ прикладывается к резистору R5. Это приводит к приращению тока эмиттера транзистора 15, пропорционального uвх

Таким образом коллекторный ток транзистора 15 изменяется пропорционально Uвх в широком диапазоне входных сигналов (фиг.5). Крутизна характеристики у21 зависит от резисторов 5 и 6. Значение у21 для «большого» и «малого» сигналов практически одинаково (фиг.10).

Результаты компьютерного моделирования ДУ (фиг.9), представленные на графиках фиг.10, подтверждают полученные выше теоретические выводы.

Предлагаемый ДУ может использоваться в структуре быстродействующих операционных усилителей различного функционального назначения (фиг.8).

Источники информации

1. Патент США №3.786.362.

2. Патент США №4.030.044.

3. Патент США №4.059.808, фиг.5.

4. Патент США №4.286.227.

5. Авт. свид. СССР №375754, H03f 3/38.

6. Авт. свид. СССР №843164, H03f 3/30.

7. Патент США №3.660.773.

8. Патент США №4.560.948.

9. Патент РФ №2930041, H03f 1/32.

10. Патент Японии №57-5364, H03f 3/343.

11. Патент ЧССР №134845, кл. 21a2 18/08.

12. Патент ЧССР №134849, кл. 21a2 18/08.

13. Патент ЧССР №135326, кл. 21а2 18/08.

14. Патент США №4.389.579.

15. Патент Англии №1543361, Н3Т.

16. Патент США №5.521.552 (фиг.3а).

17. Патент США №4.059.808.

18. Патент США №5.789.949.

19. Патент США №4.453.134.

20. Патент США №4.760.286.

21. Авт. свид. СССР №1283946.

22. Патент РФ №2019019.

23. Патент США №4.389.579.

24. Патент США №4.453.092.

25. Патент США №3.566.289.

26. Патент США №4.059.808 (фиг.2).

27. Патент США №3.649.926.

28. Патент США №4.714.894 (фиг.1).

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

1. Дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, коллекторы которых объединены и подключены ко входу (3) токового зеркала (4), а эмиттеры через первый (5) и второй (6) вспомогательные резисторы соединены с соответствующими эмиттерами первого (7) и второго (8) выходных транзисторов противоположного типа проводимости, причем базы первого (7) и второго (8) выходных транзисторов подключены к выходу (9) токового зеркала (4) и токостабилизирующему двухполюснику (10), а их коллекторы соединены с основными выходами (11) и (12) дифференциального усилителя, отличающийся тем, что эмиттеры первого (1) и второго (2) входных транзисторов соединены с первым (5) и вторым (6) вспомогательными резисторами через соответствующие первый (13) и второй (14) дополнительные резисторы, причем базы первого (1) и второго (2) входных транзисторов подключены к соответствующим базам первого (15) и второго (16) дополнительных транзисторов, эмиттер первого дополнительного резистора (15) соединен с общей точкой первого вспомогательного (5) и первого дополнительного (13) резисторов, эмиттер второго (16) дополнительного транзистора связан с общей точкой второго вспомогательного (6) и второго дополнительного (14) резисторов, а коллекторы первого (15) и второго (16) дополнительных транзисторов связаны с первым (17) и вторым (18) дополнительными выходами дифференциального усилителя.

2. Устройство по п.1, отличающееся тем, что площади эмиттерных переходов первого (1) и второго (2) входных транзисторов в N-раз (N>1) превосходят площади эмиттерных переходов первого (15) и второго (16) дополнительных транзисторов.

3. Устройство по п.1, отличающееся тем, что в качестве первого (1) и второго (2) входных транзисторов применены полевые транзисторы, затворы которых соответствуют базам, стоки - коллекторам, истоки - эмиттерам первого (1) и второго (2) входных транзисторов.