Дифференциальный усилитель класса ав

Иллюстрации

Показать всеИзобретение относится к радиотехнике и связи для использования в структуре аналоговых микросхем. Технический результат заключается в расширении диапазона активной работы. Дифференциальный усилитель содержит первый входной дифференциальный каскад (ДК) (1) на n-p-n входных транзисторах (Т) (2, 3), первый инвертирующий сумматор синфазных сигналов (С) (4), входы которого (5) и (6) связаны с коллекторами входных n-p-n Т (2) и (3), а выход (7) подключен ко входу (8) первого повторителя напряжения (ПН) (9), синфазные выходы которого (10) и (11) соединены с эмиттерами входных Т (2) и (3). В схему введен второй ДК (12) на p-n-p входных Т (13) и (14), второй инвертирующий С (15), входы которого (16) и (17) связаны с коллекторами входных p-n-p Т(13) и (14), а выход (18) подключен ко входу (19) второго повторителя напряжения, синфазные выходы которого (20) и (21) соединены с эмиттерами входных p-n-p Т (13) и (14), причем между выходом (7) первого (4) и выходом (18) второго (15) инвертирующих С включен дополнительный резистор (22), а входы второго входного ДК (12) соединены со входами первого входного ДК (1), выход (7) первого инвертирующего С (4) связан со входом (8) первого ПН (9) через первый двухполюсник цепи смещения (23), а выход (18) второго инвертирующего С (15) соединен с входом (19) второго ПН через второй двухполюсник цепи смещения (24). 9 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ), компенсационных стабилизаторах напряжения и т.д.).

Известны схемы дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах с так называемой «архитектурой входного каскада операционного усилителя μА741» [1-30]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, в том числе их параллельное соединение (патент США №5521533, фиг.3а), наряду с типовым параллельно-балансным каскадом [29-30], стали основным усилительным элементом многих аналоговых интерфейсов. Это связано с тем, что в таких ДУ входная емкость оказывается минимальной из-за отсутствия эффекта Миллера. Предлагаемое изобретение относится к данному подклассу устройств.

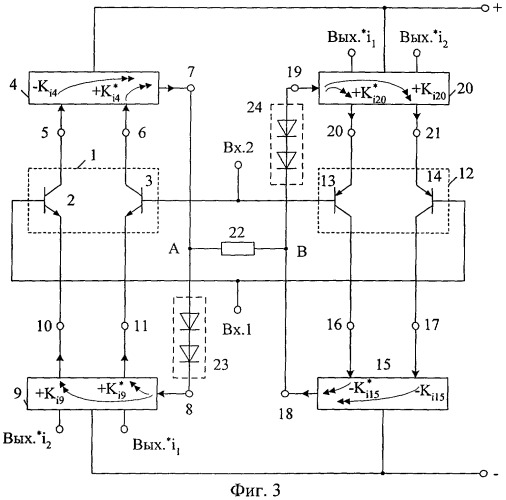

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №3660773, содержащий первый входной дифференциальный каскад 1 на n-p-n входных транзисторах 2, 3, первый инвертирующий сумматор синфазных сигналов 4, входы которого 5 и 6 связаны с коллекторами входных n-p-n транзисторов 2 и 3, а выход 7 подключен ко входу 8 первого повторителя напряжения 9, синфазные выходы которого 10 и 11 соединены с эмиттерами входных транзисторов 2 и 3.

Существенный недостаток известного ДУ состоит в том, что он имеет узкий динамический диапазон линейного усиления дифференциальных сигналов относительно основных токовых выходов (|uвх|<Uгр≈100-150 мВ) и не обеспечивает формирование выходных токов, пропорциональных модулю входного дифференциального напряжения.

Основная цель предлагаемого изобретения состоит в расширении диапазона активной работы, в пределах которого обеспечивается пропорциональное входному напряжению изменение выходных токов ДУ.

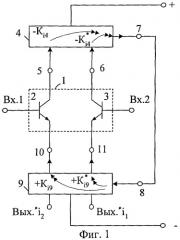

Поставленная цель достигается тем, что в дифференциальный усилитель (фиг.1), содержащий первый входной дифференциальный каскад 1 на n-p-n входных транзисторах 2, 3, первый инвертирующий сумматор синфазных сигналов 4, входы 5 и 6 которого связаны с коллекторами входных n-p-n транзисторов 2 и 3, а выход 7 подключен ко входу 8 первого повторителя напряжения 9, синфазные выходы 10 и 11 которого соединены с эмиттерами входных транзисторов 2 и 3, вводятся новые элементы и связи - в схему введен второй дифференциальный каскад 12 на p-n-p входных транзисторах 13 и 14, второй инвертирующий сумматор синфазных сигналов 15, входы 16 и 17 которого связаны с коллекторами входных p-n-p транзисторов 13 и 14, а выход 18 подключен ко входу 19 второго повторителя напряжения 20, синфазные выходы 20 и 21 которого соединены с эмиттерами входных p-n-p транзисторов 13 и 14, причем между выходом 7 первого 4 и выходом 18 второго 15 инвертирующих сумматоров синфазного сигнала включен дополнительный резистор 22, а входы второго входного дифференциального каскада 12 соединены со входами первого входного дифференциального каскада 1, выход 7 первого инвертирующего сумматора синфазных сигналов 4 связан со входом 8 первого повторителя напряжения 9 через первый двухполюсник цепи смещения 23, а выход 18 второго инвертирующего сумматора синфазных сигналов 15 соединен с входом 19 второго повторителя напряжения 20 через второй двухполюсник цепи смещения 24.

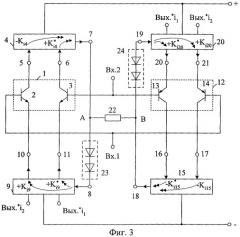

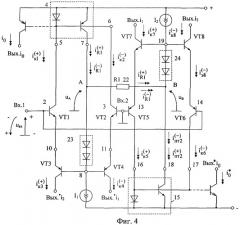

Схема усилителя-прототипа представлена на чертеже фиг.1. На чертеже фиг.2 показана схема прототипа при конкретном выполнении его функциональных узлов. На чертеже фиг.3 представлена схема заявляемого устройства. На чертеже фиг.4 показаны токи и напряжения в заявляемом ДУ фиг.3 при работе с дифференциальным сигналом. На чертеже фиг.5 представлен заявляемый ДУ фиг.4 в среде компьютерного моделирования PSpice на моделях транзисторов ФГУП НПП "Пульсар" (г. Москва). Графики, показанные на чертеже фиг.6, иллюстрируют работу заявляемого устройства фиг.5, где обозначено:

IRm - ток резистора Rm (22);

IR9, IR10 - токи выходов Вых.i1, Вых.i2, Вых.*i2, Вых.i2 (фиг.4). Причем IR9=IR3, IR10=IR4, IRm≈i0≈I* 0.

График фиг.7 соответствует графику фиг.6, но в более укрупненном масштабе по оси токов.

На чертеже фиг.8 показана обобщенная функциональная схема заявляемого устройства (фиг.3-фиг.4), а на чертеже фиг.9 - ее статические проходные характеристики для каждого из имеющихся выходов 6, которые могут использоваться для организации многоканальной передачи входных сигналов на выход той или иной быстродействующей аналоговой микросхемы.

Дифференциальный усилитель фиг.3 содержит первый входной дифференциальный каскад 1 на n-p-n входных транзисторах 2, 3, первый инвертирующий сумматор синфазных сигналов 4, входы 5 и 6 которого связаны с коллекторами входных n-p-n транзисторов 2 и 3, а выход 7 подключен ко входу 8 первого повторителя напряжения 9, синфазные выходы 10 и 11 которого соединены с эмиттерами входных транзисторов 2 и 3. В схему введен второй дифференциальный каскад 12 на p-n-p входных транзисторах 13 и 14, второй инвертирующий сумматор синфазных сигналов 15, входы 16 и 17 которого связаны с коллекторами входных p-n-p транзисторов 13 и 14, а выход 18 подключен ко входу 19 второго повторителя напряжения 20, синфазные выходы 20 и 21 которого соединены с эмиттерами входных p-n-p транзисторов 13 и 14, причем между выходом 7 первого 4 и выходом 18 второго 15 инвертирующих сумматоров синфазного сигнала включен дополнительный резистор 22, а входы второго входного дифференциального каскада 12 соединены со входами первого входного дифференциального каскада 1, выход 7 первого инвертирующего сумматора синфазных сигналов 4 связан со входом 8 первого повторителя напряжения 9 через первый двухполюсник цепи смещения 23, а выход 18 второго инвертирующего сумматора синфазных сигналов 15 соединен с входом 19 второго повторителя напряжения 20 через второй двухполюсник цепи смещения 24.

В случае, если в качестве активных элементов повторителя напряжения 9 или входных транзисторов (2, 3) применяются полевые транзисторы, то двухполюсники цепей смещения 23, 24 могут быть исключены из рассмотрения (закорочены).

Рассмотрим работу заявляемого ДУ фиг.5. В статическом режиме коллекторные токи транзисторов 2 (VT1, VT3), 3 (VT4), 13 (VT7), 14 (VT8) одинаковы. За счет отрицательной обратной связи по синфазному сигналу:

где I1, I2 - токи источников опорного тока I1 и I2.

За счет введения цепей смещения 23 и 24 статический потенциал узла "А" приблизительно равен статическому потенциалу узла "В". Поэтому статический ток через резистор 22 (R1, фиг.4) близок к нулю. Если этот ток не равен нулю, то изменением параметров цепей смещения необходимо выровнять потенциалы UA=UB.

Если на вход Вх.1 ДУ фиг.4 подать положительное напряжение uвх, то коллекторные токи транзисторов VT2 и VT4, VT6 (14), VT8 начнут уменьшаться, а транзисторов VT1 (12), VT3, VT5 (13), VT7 увеличиваться за счет перераспределения суммы этих токов I1 (I2) между данными транзисторами. При этом, начиная с uвх≥80÷120 мВ транзисторы VT2 (3), VT4 и VT8, VT6 (14) войдут в режим, близкий к режиму отсечки - их коллекторные токи достигнут достаточно малых значений (в сравнении со статическими токами). Поэтому потенциал узла "В" перестанет изменяться, а узла "А" будет "повторять" входное напряжение:

Это приведет к появлению разницы:

и, следовательно, тока через резистор R1 (22):

Численные значения этого тока будут равны приращению выходного тока токовых зеркал 15 и 4 и, следовательно, токам коллекторов VT1 и VT3, VT5, VT7. Поэтому выходные токи дифференциального усилителя фиг.4 будут также увеличиваться пропорционально uвх:

Данная пропорциональность будет сохраняться до тех пор, пока эти токи не

достигнут величины Imax=β3·I1 (или Imax=β7·I2), где β3, β7 - коэффициенты усиления по току базы транзисторов 3, 7.

Из приведенного анализа следует, что диапазон изменения выходных токов в заявляемом устройстве значительно превышает их статические уровни, что характерно для усилителей класса "АВ". Данные выводы подтверждаются графиками, приведенными на чертежах фиг.6, фиг.7, из которых следует, что при изменении входного сигнала uвх в диапазоне 0÷3 В выходные токи ДУ изменяются от 180 мкА до 10 мА, т.е. более чем в 50 раз.

При этом во столько же раз пропорционально напряжению uвх изменяются и выходные токи iвых.0, , численно равные токам эмиттера транзисторов VT16 и VТ20 (фиг.5).

По существу заявляемое устройство является мультивыходным преобразователем "напряжение-ток" (фиг.8) с широким диапазоном активной работы. Причем токи его выходов "Вых.i0", "Вых.*i0" пропорциональны модулю |uвх|. Данное положительное качество позволяет реализовывать на основе заявляемого устройства быстродействующие ОУ с нелинейной коррекцией в выходных и промежуточных каскадах (по аналогии с патентами США №6.710.655, 6.710.654).

Результаты компьютерного моделирования ДУ фиг.5, представленные на графиках фиг.6, 7, подтверждают полученные выше теоретические выводы.

Библиографический список

1. Патент США №3786362.

2. Патент США №4030044.

3. Патент США №4059808, фиг.5.

4. Патент США №4286227.

5. Авт. свид. СССР №375754, H03f 3/38.

6. Авт. свид. СССР №843164, H03f 3/30.

7. Патент США №3660773.

8. Патент США №4560948.

9. Патент РФ №2930041, H03f 1/32.

10. Патент Японии №57-5364, H03f 3/343.

11. Патент ЧССР №134845, кл. 21a2 18/08.

12. Патент ЧССР №134849, кл. 21a2 18/08.

13. Патент ЧССР №135326, кл. 21а2 18/08.

14. Патент США №4389579.

15. Патент Англии №1543361, Н3Т.

16. Патент США №5521552 (фиг.3а).

17. Патент США №4059808.

18. Патент США №5789949.

19. Патент США №4453134.

20. Патент США №4760286.

21. Авт. свид. СССР №1283946.

22. Патент РФ №2019019.

23. Патент США №4389579.

24. Патент США №4453092.

25. Патент США №3566289.

26. Патент США №4059808 (фиг.2).

27. Патент США №3649926.

28. Патент США №4714894 (фиг.1).

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

Дифференциальный усилитель класса АВ, содержащий первый входной дифференциальный каскад (1) на n-p-n входных транзисторах (2), (3), первый инвертирующий сумматор синфазных сигналов (4), входы которого (5) и (6) связаны с коллекторами входных n-p-n транзисторов (2) и (3), а выход (7) подключен ко входу (8) первого повторителя напряжения (9), синфазные выходы которого (10) и (11) соединены с эмиттерами входных транзисторов (2) и (3), отличающийся тем, что в схему введен второй дифференциальный каскад (12) на p-n-p входных транзисторах (13) и (14), второй инвертирующий сумматор синфазных сигналов (15), входы которого (16) и (17) связаны с коллекторами входных p-n-p транзисторов (13) и (14), а выход (18) подключен ко входу (19) второго повторителя напряжения, синфазные выходы которого (20) и (21) соединены с эмиттерами входных p-n-p транзисторов (13) и (14), причем между выходом (7) первого (4) и выходом (18) второго (15) инвертирующих сумматоров синфазного сигнала включен дополнительный резистор (22), а входы второго входного дифференциального каскада (12) соединены со входами первого входного дифференциального каскада (1), выход (7) первого инвертирующего сумматора синфазных сигналов (4) связан со входом (8) первого повторителя напряжения (9) через первый двухполюсник цепи смещения (23), а выход (18) второго инвертирующего сумматора синфазных сигналов (15) соединен с входом (19) второго повторителя напряжения через второй двухполюсник цепи смещения (24).