Дифференциальный усилитель с повышенным ослаблением синфазного сигнала

Иллюстрации

Показать всеИзобретение относится к радиотехнике для использования в структуре аналоговых микросхем. Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов. Дифференциальный усилитель содержит входной дифференциальный каскад (ДК) (1), общая эмиттерная цепь (2) которого соединена с коллекторным выходом (3) токового зеркала (4). Первый выход (5) входного ДК (1) соединен с первым токовым входом (7) сумматора тока (8), второй вход (9) которого подключен к эмиттерному выходу (10) токового зеркала (4). Если обеспечить коэффициент усиления по току сумматора тока (8) от его входа (9) на его же выход (12) равным половине коэффициента усиления по току от его входа (7) на выход (12), то выходной ток, обусловленный синфазным сигналом, будет равен нулю. 3 з.п. ф-лы, 14 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы классических дифференциальных усилителей (ДУ) с токовым зеркалом в общей эмиттерной цепи, которое обеспечивает стабилизацию статического режима биполярных и полевых транзисторов ДУ [1-11]. Дифференциальные усилители данного класса стали основным усилительным элементом многих аналоговых устройств. На их модификации выдано более 500 патентов различным микроэлектронным фирмам.

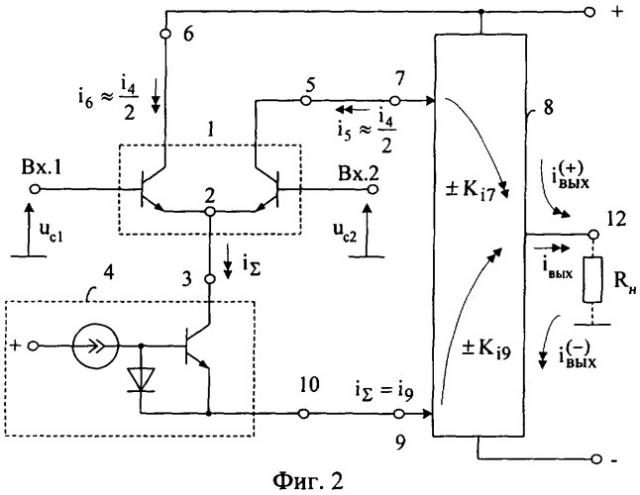

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №4122402 (фиг.4), содержащий входной дифференциальный каскад 1, общая эмиттерная цепь которого 2 соединена с коллекторным выходом 3 токового зеркала 4.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ДУ.

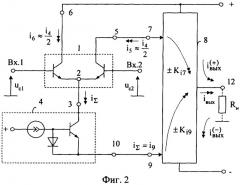

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий входной дифференциальный каскад 1, общая эмиттерная цепь которого 2 соединена с коллекторным выходом 3 токового зеркала 4, вводятся новые элементы и связи - первый выход 5 входного дифференциального каскада 1 связан с первым токовым входом 7 дополнительного сумматора токов 8, а второй токовый вход 9 дополнительного сумматора токов 8 подключен к эмиттерному выходу 10 токового зеркала 4.

Схема усилителя-прототипа представлена на чертеже фиг.1.

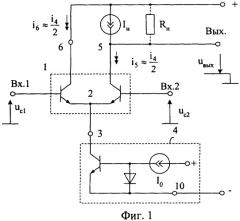

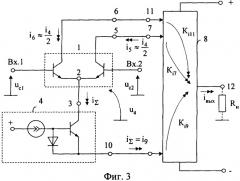

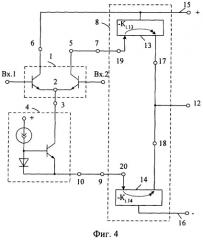

На фиг.2 показан усилитель в соответствии с п.1 и п.3 формулы изобретения. Схема фиг.3 соответствует п.2 формулы изобретения. На фиг.4 показан частный случай построения ДУ фиг.2. Варианты построения токовых зеркал 13 и 14 ДУ фиг.4 показаны на фиг.5, фиг.6.

На фиг.7 показан вариант построения заявляемого ДУ для случая, когда дополнительный сумматор токов 8 выполнен на основе "перегнутого каскода" с использованием элементов 27-39.

Другой вариант построения заявляемого ДУ с дополнительным сумматором токов 8 на элементах 40-47 представлен на фиг.8.

На фиг.9 показана схема ДУ фиг.3, у которого сумматор токов 8 реализован на элементах 48-59.

На фиг.10 показана схема ДУ-прототипа в среде моделирования PSpice с использованием моделей интегральных транзисторов ФГУП НПП "Пульсар".

На фиг.11 показана схема заявляемого ДУ, соответствующего фиг.4 для случая, когда в качестве токовых зеркал 13 и 14 применяются идеальные токовые зеркала F2 и F1, а на фиг.12 - реальные токовые зеркала. Это позволяет оценить влияние на ослабление синфазных сигналов предлагаемых архитектурных решений (независимо от качества транзисторов).

На фиг.13-14 приведены результаты компьютерного моделирования заявляемого (фиг.11) и известного (фиг.10) ДУ в среде PSpice на моделях транзисторов ФГУП "Пульсар", где Kсф=uвых/uc.

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1, общая эмиттерная цепь которого 2 соединена с коллекторным выходом 3 токового зеркала 4. Первый выход 5 входного дифференциального каскада 1 связан с первым токовым входом 7 дополнительного сумматора токов 8, а второй токовый вход 9 дополнительного сумматора токов 8 подключен к эмиттерному выходу 10 токового зеркала 4.

Рассмотрим работу заявляемого ДУ фиг.3.

Входной синфазный сигнал uс=uc1=uc2 практически с единичным коэффициентом передачи поступает на выход 3 токового зеркала 4:

Это приводит к изменению тока общей эмиттерной цепи 2 ДУ i∑ и входного тока i9 дополнительного сумматора токов 8:

где у4 - выходная проводимость токового зеркала 4.

Приращение i∑ передается на выход 5 ДУ и поступает на вход 7 дополнительного сумматора токов 8:

Как следствие выходной ток iвых=i12 дополнительного сумматора тока 8 имеет две противоположно направленные составляющие

где Ki7 - коэффициент усиления по току от входа 7 на выход 12;

Кi9 - коэффициент усиления по току от входа 9 на выход 12.

Следовательно выходной ток ДУ iвых, обусловленный наличием на входах Вх.1 и Вх.2 синфазного сигнала uc:

если обеспечить , то выходной ток, обусловленный синфазным сигналом, будет равен нулю. Это означает, что в заявляемой схеме существенно ослабляется "прохождение" синфазной помехи со входов Вх.1 и Вх.2 на выход 12, обусловленной влиянием выходной проводимости токового зеркала 4.

Учитывая, что дифференциальный коэффициент усиления Ку схем фиг.1 - фиг.2 одинаков, можно сделать вывод о том, что коэффициент ослабления синфазного сигнала в схеме фиг.2 существенно возрастает.

Полученные выше теоретические выводы подтверждаются результатами (фиг.13, фиг.14) компьютерного моделирования ДУ фиг.10 - фиг.12. Из графиков фиг.13, фиг.14 следует, что коэффициент передачи входного синфазного сигнала Kсф в заявляемом ДУ более чем на порядок - 30 дБ меньше Kсф ДУ-прототипа (фиг.1).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Справочник: операционные усилители и компараторы (Авербух В.Д. и др.). - М.: Изд-во "Додэка-XXI", 2001, С.122 (НА2539).

2. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989, стр. 103, рис.6.11 (ОУ НА5190).

3. Ежков Ю.С. Справочник по схемотехнике усилителей. - М., Радиософт, 2002, с.87, рис.5.21.

4. Патент США №3982197.

5. Патент США №5220289.

6. Патент США №5642062.

7. Патент США №5132640.

8. Патент США №4047119.

9. Патент США №4122402.

10. Патент США №3614645.

11. Патентная заявка US 2005/0128000 A1.

1. Дифференциальный усилитель, содержащий входной дифференциальный каскад (1), общая эмиттерная цепь (2) которого соединена с коллекторным выходом (3) токового зеркала (4), отличающийся тем, что первый выход (5) входного дифференциального каскада (1) связан с первым токовым входом (7) дополнительного сумматора тока (8), а второй токовый вход (9) дополнительного сумматора тока (8) подключен к эмиттерному выходу (10) токового зеркала (4).

2. Устройство по п.1, отличающееся тем, что второй выход (6) входного дифференциального каскада (1) связан с третьим (11) токовым входом дополнительного сумматора тока (8), противофазным первому токовому входу (7).

3. Устройство по п.1, отличающееся тем, что коэффициент передачи по току со второго токового входа (9) на выход дополнительного сумматора (8) в два раза меньше, чем коэффициент передачи по току от первого токового входа (7) на выход (12) дополнительного сумматора тока (8).

4. Устройство по п.1 или 3, отличающееся тем, что дополнительный сумматор тока (8) выполнен на основе вспомогательных токовых зеркал (13) и (14), согласованных с шинами положительного (15) и отрицательного (16) источников питания, выходы которых (17) и (18) связаны с выходом дифференциального усилителя (12), а входы (19) и (20) соединены соответственно с первым выходом (5) входного дифференциального каскада (1) и эмиттерным выходом (10) токового зеркала (4) в общей эмиттерной цепи (2) входного дифференциального каскада (1).