Устройство и способ для формирования и декодирования кодов с прямым исправлением ошибок, имеющих переменную скорость передачи в высокоскоростной беспроводной системе передачи данных

Иллюстрации

Показать всеИзобретение относится к устройство и способу для генерации кодов, имеющих переменную скорость передачи, с прямым исправлением ошибок в беспроводной системе передачи данных. Устройство для формирования квазикомплементарных сдвоенных двоичных турбокодов (QC-DBTC) включает в себя QC-DBTC кодер, который принимает поток информационных символов и формирует множество потоков систематических символов и множество потоков символов четности в соответствии с заданной скоростью кодирования. Устройство дополнительно включает в себя квадро-символьный преобразователь, который выполняет квадро-символьное преобразование потоков систематических символов в один поток символов, канальный перемежитель, который независимо перемежает квадро-преобразованный поток систематических символов и потоки символов четности, выполняет обратное квадро-преобразование квадро-преобразованного потока систематических символов, чередует символы в потоках символов четности и последовательно конкатенирует обратно квадро-преобразованный поток систематических символов с чередованными потоками символов четности, а также генератор сдвоенного двоичного турбокода для повторения последовательно конкатенированного потока символов и выбора заранее определенного количества символов из повторного потока символов согласно скорости кодирования и информации выбора, таким образом формируя QC-DBTC коды. Технический результат - обеспечение различной избыточности простым QC-DBTC кодером с максимальным коэффициентом передачи системы. 9 н. и 10 з.п. ф-лы, 9 ил., 2 табл.

Реферат

Область техники

Изобретение в целом относится к устройству и способу для генерации кодов с прямым исправлением ошибок (FEC) в беспроводной системе передачи данных. Более конкретно, настоящее изобретение относится к устройству и способу формирования FEC-кодов, имеющих переменную скорость передачи.

Описание предшествующего уровня техники

Обычно беспроводные системы передачи данных классифицируются как система мобильной связи (MCS), беспроводная локальная сеть (WLAN), глобальная сеть (WAN) или региональная сеть (MAN), которые все основаны на технологии мобильной связи. Для систем мобильной связи системы для высокоскоростной передачи данных также развиваются независимо, в соответствии с проектом-2 партнерства 3-го поколения (3GPP2), группой стандартизации для синхронных систем мобильной связи с множественным доступом с кодовым разделением каналов (МДКРК, CDMA) и проектом партнерства 3-го поколения (3GPP), группой стандартизации системы мобильной связи для асинхронной универсальной мобильной системы связи (UMTS). Также для WLAN, WAN и MAN были сделаны различные попытки передавать радиоданные с высокой скоростью в области стандартизации IEEE 802.11 - IEEE 802.16.

Описание ниже приведено для Адаптивной Модуляции и Кодирования (AMC), как это было предпринято в предшествующих стандартах связи. Также будет приведено описание системы IEEE 802.16a, системы CDMA2000 1x EV-DV (развитие для данных и речи), основанной на системе мобильной связи CDMA, и системы высокоскоростного мобильного Интернет (HPi), в настоящее время разрабатываемой в Южной Корее для высокоскоростной передачи данных в диапазоне 2.4 ГГц, которые все содержат наиболее существенно продвинутые системы в этой области техники.

Сначала описана система IEEE 802.16a. Система IEEE 802.16a является системой, использующей доступ на основе мультиплексирования с ортогональным частотным разделением сигналов (OFDMA).

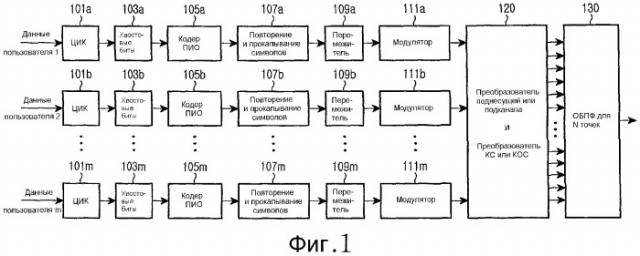

Фиг.1 изображает блок-схему, иллюстрирующую структуры физических каналов для передачи данных с высокой скоростью в системе IEEE 802.16a, использующей мультиплексирование с ортогональным частотным разделением сигналов (OFDM). Как показано на фиг.1, все физические каналы, передаваемые пользователям User1, User2, ..., Userm, имеют одинаковую структуру. Поэтому на фиг.1 одинаковым элементам назначены одинаковые ссылочные позиции, и различные символы типа a, b, ..., m добавлены к ссылочным позициям в качестве индикаторов для указания соответствующих пользователей и связанных с ними физических каналов. Параметры, используемые в физических каналах для пользователей User1, User2, ..., Userm, могут иметь или одинаковые значения или различные значения. Например, соответствующие физические каналы могут отличаться друг от друга по размеру входного пакета, скорости кодирования, степени модуляции и продолжительности передачи. Ниже, в качестве примера, приведено описание физического канала для первого пользователя User1.

В физическом канале данные User1_Data, подлежащие передаче к первому пользователю User1, вводят в сумматор 101a с проверкой циклическим избыточным кодом (CRC, ЦИК), и сумматор CRC 101a добавляет CRC к входным данным User1_Data пользователя так, чтобы сторона приема могла обнаружить ошибку, имеющую место вследствие шумов в процессе передачи канала. Данные пользователя с добавленным CRC вводят в сумматор 103a хвостовых битов, и сумматор 103a хвостовых битов добавляет хвостовые биты к данным пользователя с добавленным CRC. CRC является кодом коррекции ошибок, используемым для исправления ошибки, имеющей место из-за шумов в процессе передачи канала, и обычно используется для прямого исправления ошибок (FEC, ПИО). Обычно сверточные коды или турбокоды используются для FEC, используемого в системе радиосвязи. Эти коды используют хвостовые биты, которые являются битами завершения для завершения соответствующих кодов в состоянии '0' на решетчатой диаграмме. Поэтому данные с добавленными хвостовыми битами являются FEC-кодированными с помощью FEC-кодера 105a. Поскольку это подробно раскрыто в соответствующих документах, его подробное описание будет опущено.

Затем, чтобы согласовать количество выходных сигналов FEC-кодера 105a с количеством символов модуляции, назначенных каждому пользователю, часть 107a прокалывания (перфорирования, удаления) и повторения символов выполняет повторение символа и перфорирование в отношении FEC-кодированных данных. Символы, которые подверглись повторению и прокалыванию, подают на канальный перемежитель 109a для преобразования пакета ошибок, встречающегося в канале, в случайную ошибку, и канальный перемежитель 109a выполняет канальное перемежение входных символов. Символы с канальным перемежением подают на модулятор 111а, и модулятор 111а модулирует символы с канальным перемежением. Модулированные символы подают на преобразователь 120 поднесущей или подканала и преобразователь NOS или NOOS. Преобразователь 120 поднесущей или подканала и преобразователь NOS или NOOS выполняют отображение (преобразование) поднесущей или подканала, и отображение (преобразование) NOS (количество слотов, КС) или NOOS (количество OFDM символов, КОС) в модулированные символы в течение продолжительности передачи, распределенной каждому пользователю. Преобразователь 120 поднесущей или подканала и преобразователь NOS или NOOS одновременно обрабатывают данные для всех пользователей. Вывод символов из преобразователя 120 поднесущей или подканала и преобразователя NOS или NOOS подают на блок 130 обратного быстрого преобразования Фурье (IFFT, ОБПФ), и блок 130 IFFT выполняет обратное быстрое преобразование Фурье над входными символами. Таким образом, данные для каждого пользователя преобразуются в один несущий сигнал и подаются на радиочастотный (РЧ) модуль (не показан).

В предшествующем описании "NOS" или "NOOS" обозначают продолжительность передачи, распределенную каждому пользователю, и являются переменными в соответствии с размером данных пользователя. Поэтому увеличение NOS или NOOS вызывает увеличение во времени передачи распределенному одному пакету. Кроме того, "подканал" означает набор поднесущих, используемых при мультиплексировании с ортогональным частотным разделением сигналов (OFDM). Не является необходимым, чтобы поднесущие, составляющие один подканал, всегда были упорядочены в регулярной последовательности в частотной области, и обычно множество поднесущих составляют один подканал согласно конкретному шаблону (образцу). Например, когда заданная ширина полосы частот разделена на 2048 ортогональных частот, если имеются с 1-ой по 2048-ую поднесущих, один подканал может быть конфигурирован с 4 поднесущими из 1-ой, 8-ой, 16-ой, 32-ой и 64-ой поднесущими. Конфигурация подканала и количество поднесущих, составляющих подканал, могут изменяться согласно стандартам.

Фиг.2 изображает блок-схему, иллюстрирующую структуры физических каналов для передачи данных пользователю в современной системе HPi высокоскоростной передачи данных. Структура на фиг.2 по существу идентична таковой на фиг.1 за исключением того, что структура согласно фиг.2 не добавляет хвостовые биты и CRC. Это имеет место потому, что функция CRC может быть выполнена на уровне управления доступом к среде (MAC). Поэтому элементы 205, 207, 209, 211, 220 и 230 на фиг.2 соответствуют элементам 105, 107, 109, 111, 120 и 130 на фиг.1, соответственно. Когда структуры согласно обеим фиг.1 и 2 имеют множество модуляторов и множество скоростей кодирования с FEC, они требуют схемы для определения скорости кодирования и степени модуляции для гарантии обеспечения лучшей производительности каждому пользователю.

Как проиллюстрировано на фиг.1 и 2, в физическом канале необходим модулятор для службы передачи пакетных данных. Кроме того, FEC-коды используются для того, чтобы преодолеть ошибки в данных, вызванные шумами, имеющими место в канале радиосвязи. Однако в текущем физическом канале для службы передачи пакетных данных FEC-коды с фиксированной скоростью передачи обычно используются и, в частности, используются наилучшие коды для заданной скорости передачи. Это имеет место потому, что физический канал для службы передачи пакетных данных имеет характеристику стационарного канала, такую как канал с аддитивным белым гауссовым шумом (AWGN). Поэтому, имеется меньше необходимости принимать во внимание FEC-коды, используя адаптивную скорость передачи. Например, IEEE 802.16a, стандарт беспроводной высокоскоростной передачи данных не гарантирует мобильность мобильной станции и использует только 6 скоростей кодирования с FEC. Подробное описание стандарта раскрыто в стандарте IEEE 802.16a физического канала, полное содержание которого включено в настоящее описание по ссылке. В то время как система мобильной связи использует двоичные турбокоды, IEEE 802.16a использует сдвоенные двоичные турбокоды.

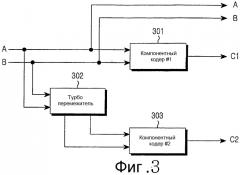

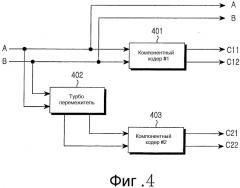

Сдвоенные двоичные турбокоды описаны ниже более подробно. Фиг.3 является блок-схемой, иллюстрирующей устройство для формирования сдвоенных двоичных турбокодов со скоростью кодирования R=1/2, и фиг.4 является блок-схемой, иллюстрирующей устройство для формирования сдвоенных двоичных турбокодов с R=1/3.

Как проиллюстрировано на фиг.3, сдвоенный двоичный турбокодер с R=1/2 принимает 2 информационных символа А и B параллельно. Эти 2 информационных символа А и B, принятых параллельно, подают вместе на первый компонентный кодер 301 и турбоперемежитель 302. Турбоперемежитель 302 выполняет перемежение 2 параллельных символов А и B входной информации и выдает перемеженные информационные символы на второй компонентный кодер 303. Упомянутые 2 параллельных символа А и B входной информации выводятся неизмененными в качестве систематических символов, и первый компонентный кодер 301 и второй компонентный кодер 303 генерируют символы C1 и C2 четности, соответственно, используя 2 символа А и B входной информации. В результате 2 символа входной информации выводятся неизменными в качестве систематических символов, и каждый компонентный кодер формирует один символ четности. Поэтому скорость кодирования кодера равна 1/2.

Сдвоенный двоичный турбокодер с R=1/3 согласно фиг.4 принимает 2 информационных символа А и B параллельно. Эти 2 параллельных символа А и B входной информации подают совместно на первый компонентный кодер 401 и турбоперемежитель 402. Турбоперемежитель 402 выполняет перемежение 2 параллельных символов А и B входной информации и выдает перемеженные информационные символы на второй компонентный кодер 403. 2 параллельных символа А и B входной информации выводятся неизменными в качестве систематических символов, и первый компонентный кодер 401 и второй компонентный кодер 403 формируют пару символов C11;C12 и C21;C22 четности, соответственно, используя 2 символа А и B входной информации. В результате 2 символа входной информации выводятся неизменными в качестве систематических символов, и каждый компонентный кодер формирует два символа четности. Поэтому скорость кодирования кодера равна 1/3.

Ниже приведено описание способа кодирования, выполненного в сдвоенных двоичных турбокодерах согласно фиг.3 и 4. Пусть размер информационного символа, который должен быть закодирован, равен N_EP, и пары информационных символов с N_EP/2, которые формируются посредством деления размера N_EP информационного символа на два, обозначены A_i и B_i (где i=0, 1, ..., N_EP/2), соответственно. В этом случае сдвоенный двоичный турбокодер кодирует пару символов A_i и B_i посредством первого компонентного кодера 301 (или 401) и выдает символ C1 четности (или пару символов C11;C12 четности) в качестве результата кодирования. Затем турбоперемежитель 302 (или 402) выполняет перемежение пары информационных символов A_i и B_i с N_EP/2 и выводит пару перемеженных информационных символов на второй компонентный кодер 303 (или 403). Второй компонентный кодер 303 (или 403) кодирует пары символов входной информации и выводит символ C2 четности (или пару символов C21;C22 четности) в качестве результата кодирования. В результате, для N_EP символов входной информации, сдвоенный двоичный турбокодер с R=1/2 выводит 2N_EP символов кодового слова, и сдвоенный двоичный турбокодер с R=1/3 выдает 3N_EP символов кодового слова.

Специалистам известно, что сдвоенные двоичные турбокоды немного превосходят двоичные турбокоды в эффективности при высокой скорости кодирования. При сравнении с двоичными турбокодами, чей размер информационного символа равен N_EP, сдвоенные двоичные турбокоды, чей размер информационного символа также равен N_EP, уменьшаются до 1/2 в длине решетки, то есть длине кадра, способствуя 1/2 сокращения в задержке декодирования. К сожалению, однако, сдвоенные двоичные турбокоды уступают двоичным турбокодам в эффективности при более низкой скорости кодирования. Кроме того, сдвоенные двоичные турбокоды в смысле сложности декодирования выше, чем двоичные турбокоды, потому что в решетчатой диаграмме используются 4 ветви для каждого состояния.

Однако CDMA2000 1x EV-DV (Развитие с Данными и Речью), стандарт синхронной мобильной связи, гарантирует мобильность мобильной станции. Чтобы гарантировать мобильность, системе нужно не только учитывать ошибки в данных, вызванные шумами, встречающимися в канале радиосвязи, но также необходимо учитывать и различные схемы преодоления ошибок в данных, вызванных замиранием. Например, чтобы передатчик мог активно справляться с динамическим изменением в отношении сигнал-шум (SNR), имеющим место в среде канала с замиранием, экстенсивно рассматриваются схема модуляции пакетной передачи одного и того же пакета передачи во все моменты времени и схема AMC изменения скорости кодирования FEC-кодов. Например, в CDMA2000 1x EV-DV используются квазикомплементарные турбокоды (QCTC, ККТК) для физического канала в качестве схемы для свободной поддержки переменной скорости кодирования. QCTC обозначает набор турбокодов с различными скоростями кодирования, выбранными селектором символов после того, как переставлены (переупорядочены) кодовые символы, закодированные из заданного родительского кода в соответствии со специфическим правилом, как показано на фиг.5.

Со ссылками на фиг.5 приводится описание работы QCTC, выбранного в качестве стандартного для системы CDMA2000 1x EV-DV. Когда информационный поток 500 подают на турбокодер 510, имеющий скорость кодирования R=1/5, турбокодер 510 выполняет турбокодирование над N_EP символами входной информации, используя родительский код. В результате турбокодер 510 генерирует 5xN_EP кодовых символов. Сформированные кодовые символы демультиплексируют в 5 субблоков с помощью блока 512 разделения кодовых символов. Разделенные кодовые символы обозначены ссылочной позицией 514. Кодовые символы 514 разделяют на группу систематических символов (или субблок X) и множество групп символов четности (или субблоки Y0, Y1, Y'0 и Y'1). Соответствующие группы символов подвергаются перемежению с частичным обратным порядком битов (PBRO, ЧОПБ). Здесь соответствующие субблоки подвергаются независимому перемежению. Это называется "перемежением субблоков". Ссылочные позиции 516a, 516b, 516c, 516d и 516e обозначают независимые устройства для выполнения перемежения PBRO.

Среди PBRO-перемеженных символов систематические символы выводятся неизменными, и PBRO-перемеженные символы четности являются переставленными чередующимся образом посредством блоков 518a и 518b чередования. Перестановка (переупорядочение) достигается таким образом, что два символа переставляются однажды. То есть, блок 518a чередования формирует новую группу, чередуя символы Y0 и Y'0 четности. Точно так же, блок 518b чередования чередующимся образом переставляет символы Y1 и Y'1 четности, сформированные в каждом субблоке, таким образом формируя новую группу. Поэтому каждая группа, сформированная чередованием, имеет размер 2xN_EP.

Затем субблок, состоящий из перемеженных систематических символов и 2 чередованные группы четности размещаются в регулярном порядке и затем конкатенируются, таким образом формируя одну новую последовательность. Здесь, эта операция обозначена как "QCTC-символы" и ссылочной позицией 520. Посредством последовательности процессов, описанных выше, перестановка символов для формирования QCTC-кодов выполняется. Затем селектор 522 QCTC символов формирует QCTC-коды, имеющие различные скорости кодирования, посредством выбора случайных символов из 5xN_EP символов. Обычные критерии построения двоичных кодов QCTC должны принимать во внимание улучшения эффективности принятого сигнала в канале с замиранием. Критерии построения QCTC характеризуются оптимизацией не только эффективности кода, но также и эффективностью канального перемежения. Канальное перемежение обычно достигается перемежением и чередованием субблоков.

Согласно современному стандарту HPi имеется приблизительно 120 возможных различных комбинаций схем модуляции и скоростей кодирования с FEC. Однако не имеется никакой предложенной схемы формирования и определения FEC-кодов, поддерживающих эти возможные комбинации, то есть турбокодов, имеющих различные скорости кодирования. В частности, система OFDM/OFDMA не имеет никакого предложенного способа для изменения скорости кодирования с FEC в соответствии с отношением между схемой модуляции и скоростью кодирования с FEC, соответствующей каждой скорости передачи данных. Кроме того, когда используется гибридный автоматический запрос повторения (HARQ), не имеется никакой предложенной схемы для формирования различных избыточностей.

Для двоичных турбокодов, используемых в системе мобильной связи, то есть двоичных турбокодов, определенных в стандарте CDMA2000 1x EV-DV, в предшествующих средах был предложен QCTC в качестве схемы обеспечения различных кодов. Однако QCTC в основном оптимизирован для двоичных турбокодов. Поэтому требуется отдельная оптимизация, когда в качестве родительских кодов используются недвоичные турбокоды, такие как сдвоенные двоичные турбокоды. В частности, использование сдвоенных двоичных турбокодов требует классификации и перемежения символов, в которых принимается во внимание характеристика систематических символов.

Соответственно, существует потребность в устройстве и способе для формирования требуемых кодов и декодирования требуемых кодов в беспроводной системе передачи и обработке данных с высокой скоростью передачи.

Сущность изобретения

Поэтому задачей настоящего изобретения является создание устройства и способа для формирования квазикомплементарных сдвоенных двоичных турбокодов (QC-DBTC, ККСДТК), и устройства и способа для декодирования QC-DBTC кодов в высокоскоростной беспроводной системе передачи данных, в которой используются различные размеры пакетов для передачи данных.

Другой задачей настоящего изобретения является создание устройства и способа для формирования сдвоенных двоичных турбокодов, имеющих различные скорости кодирования, и устройства и способа для декодирования сдвоенных двоичных турбокодов в OFDMA высокоскоростной беспроводной системе передачи пакетных данных, в которой используется HARQ.

Другой задачей настоящего изобретения является создание устройства и способа для формирования сдвоенных двоичных турбокодов, и устройства и способа для декодирования сдвоенных двоичных турбокодов в OFDMA высокоскоростной беспроводной системе передачи пакетных данных, в которой используются различные размеры пакета, и в которой одна из схем множественной модуляции и одна из множества схем FEC кодирования выбраны в соответствии с состоянием канала, состоянием буфера, количеством доступных подканалов (или поднесущих), количеством OFDM символов и продолжительностью передачи.

В соответствии с первым аспектом настоящего изобретения обеспечивается устройство для формирования подпакетов. Устройство содержит: кодер для кодирования информационных символов, причем информационные символы подают, альтернативно, на два входа кодера; устройство разделения символов для демультиплексирования всех кодированных символов на два субблока систематических символов и две пары субблоков символов четности; канальный перемежитель для отдельного перемежения субблоков; генератор групп символов для формирования первой посимвольной (символ за символом) мультиплексированной последовательности одной пары из перемеженных субблоков символов четности, второй посимвольной мультиплексированной последовательности другой пары из перемеженных субблоков символов четности и двух систематических последовательностей из двух перемеженных субблоков систематических символов; и селектор символов для выбора заранее определенного количества символов, из двух систематических последовательностей, первой посимвольной мультиплексированной последовательности и второй посимвольной мультиплексированной последовательности.

В соответствии со вторым аспектом настоящего изобретения обеспечивается способ для формирования подпакетов. Способ содержит этапы: кодирования информационных символов, причем информационные символы подают, альтернативно, на два входа кодера; демультиплексирования всех закодированных символов на два субблока систематических символов и две пары субблоков символов четности; отдельного перемежения этих субблоков; формирования первой посимвольной мультиплексированной последовательности одной пары перемеженных субблоков символов четности, второй посимвольной мультиплексированной последовательности другой пары из перемеженных субблоков символов четности и двух систематических последовательностей из двух перемеженных субблоков систематических символов; и выбора заранее определенного количества символов из двух систематических последовательностей, - первой посимвольной мультиплексированной последовательности и второй посимвольной мультиплексированной последовательности.

В соответствии с третьим аспектом настоящего изобретения обеспечивается устройство для формирования квазикомплементарных сдвоенных двоичных турбокодов (QC-DBTC). Устройство содержит: сдвоенный двоичный турбокодер, имеющий множество компонентных кодеров для приема потока информационных символов и для формирования множества потоков систематических символов и множества потоков символов четности согласно заданной скорости кодирования, причем потоки символов четности сформированы из компонентных кодеров, ассоциированных с ними, и потоки символов четности из одного из компонентных кодеров соответствуют потокам символов четности от другого из компонентных кодеров; квадро-символьный (четверичный) преобразователь для квадро-преобразования (четверичного) потоков систематических символов в один поток символов; канальный перемежитель для независимого перемежения квадро-преобразованного потока систематических символов и потоков символов четности от компонентных кодеров, обратного квадро-преобразования потока квадро-преобразованных систематических символов, чередования символов в этих потоках символов четности, соответствующих друг другу, из числа перемеженных потоков символов четности, и последовательной конкатенации обратно квадро-преобразованного потока систематических символов к перемеженным потокам символов четности; и генератор сдвоенного двоичного турбокода для повторения последовательно конкатенированного потока символов, и для выбора заранее определенного количества символов из упомянутого повторенного потока символов в соответствии со скоростью кодирования и информацией выбора, таким образом генерируя QC-DBTC коды.

В соответствии с четвертым аспектом настоящего изобретения обеспечивается способ для формирования квазикомплементарных сдвоенных двоичных турбокодов (QC-DBTC). Способ содержит этапы: приема потока информационных символов и формирования множества потоков систематических символов и множества потоков символов четности согласно заданной скорости кодирования; разделения сформированных потоков символов на потоки систематических символов и потоки символов четности; квадро-преобразования разделенных потоков систематических символов в один поток символов; независимого перемежения квадро-преобразованного потока символов и потоков символов четности; обратного квадро-преобразования перемеженного потока систематических символов; чередования потоков символов четности попарно; конкатенации перемеженных потоков символов четности к квадро-преобразованному потоку систематических символов; и выбора символов, которые должны быть переданы в соответствии с заданной скоростью кодирования, из конкатенированных символов.

В соответствии с пятым аспектом настоящего изобретения обеспечивается устройство для формирования кодовых символов посредством кодирования потока информационных символов в соответствии с заданной скоростью кодирования, используя кодер квазикомплементарного сдвоенного двоичного турбокода (QC-DBTC), и выбора всех или некоторых из кодовых символов, которые должны быть переданы, из числа сформированных кодовых символов. Устройство содержит: QC-DBTC кодер для приема потока информационных символов и формирования QC-DBTC символов согласно заранее определенной скорости кодирования; блок разделения для разделения выведенных из QC-DBTC кодера символов во множество потоков систематических символов и множество потоков символов четности, причем потоки систематических символов объединены в один поток символов; множество перемежителей для независимого перемежения потоков символов четности; перемежитель потока систематических символов для перемежения объединенного потока систематических символов; блок чередования для чередования потоков символов четности попарно; блок конкатенации для последовательной конкатенации выходного сигнала перемежителя потока систематических символов с выходным сигналом блока чередования; и селектор символов для выбора символов, которые должны быть переданы в соответствии с заданной скоростью кодирования, из конкатенированных символов.

В соответствии с шестым аспектом настоящего изобретения обеспечивается способ для формирования кодовых символов посредством кодирования потока информационных символов в соответствии с заданной скоростью кодирования, используя кодер квазикомплементарного сдвоенного двоичного турбокода (QC-DBTC), и выбора всех или некоторых из кодовых символов, которые должны быть переданы, из числа сформированных кодовых символов. Способ содержит этапы: приема потока информационных символов и формирования QC-DBTC символов согласно заранее определенной скорости кодирования; разделения выведенных символов из QC-DBTC кодера на множество потоков систематических символов и множество потоков символов четности, причем потоки систематических символов объединены в один поток символов; независимого перемежения потоков символов четности; перемежения объединенного потока систематических символов; чередования потоков символов четности попарно; последовательной конкатенации перемеженного потока систематических символов с перемеженными потоками символов четности; и выбора символов, которые должны быть переданы в соответствии с заданной скоростью передачи данных, из конкатенированных символов.

В соответствии с седьмым аспектом настоящего изобретения обеспечивается устройство для формирования кодовых символов посредством кодирования потока информационных символов в соответствии с заданной скоростью кодирования, используя кодер квазикомплементарного сдвоенного двоичного турбокода (QC-DBTC), и выбора всех или некоторых из кодовых символов, которые должны быть переданы, из числа сформированных кодовых символов. Устройство содержит: QC-DBTC кодер, имеющий множество компонентных кодеров для приема потока информационных символов и для формирования множества потоков систематических символов и множества потоков символов четности в соответствии с заданной скоростью кодирования, причем потоки символов четности сформированы от компонентных кодеров, ассоциированных с ними, и потоки символов четности из одного из компонентных кодеров соответствуют потокам символов четности от другого одного из компонентных кодеров; блок разделения для разделения выходного сигнала QC-DBTC кодера на потоки систематических символов и потоки символов четности; множество перемежителей для независимого перемежения потоков систематических символов и потоков символов четности; блок чередования для чередования попарно, причем пары символов четности сформированы от различных компонентных кодеров; блок конкатенации для последовательной конкатенации перемеженных потоков систематических символов к перемеженным потокам символов четности; и селектор символов для выбора символов, которые должны быть переданы в соответствии с заданной скоростью передачи данных, из конкатенированных символов.

В соответствии с восьмым аспектом настоящего изобретения обеспечивается способ для формирования кодовых символов посредством кодирования потока информационных символов в соответствии с заданной скоростью кодирования, используя кодер квазикомплементарного сдвоенного двоичного турбокода (QC-DBTC), и выбора всех или некоторых из кодовых символов, которые должны быть переданы, из числа сформированных кодовых символов. Способ содержит этапы: приема QC-DBTC кодером потока информационных символов и формирования множества потоков систематических символов и множества потоков символов четности в соответствии с заданной скоростью кодирования, причем потоки символов четности сформированы из компонентных кодеров, ассоциированных с ним, и потоки символов четности от одного из компонентных кодеров соответствуют потокам символов четности от другого из компонентных кодеров; разделения выходного сигнала QC-DBTC кодера на потоки систематических символов и потоки символов четности; независимого перемежения потоков систематических символов и потоков символов четности; перемежения пар символов четности попарно; конкатенации перемеженных потоков систематических символов к перемеженным потокам символов четности; и выбора символов, которые должны быть переданы в соответствии с заданной скоростью передачи данных, из конкатенированных символов.

В соответствии с девятым аспектом настоящего изобретения обеспечивается устройство для декодирования всех или некоторых из принятых кодовых символов, сформированных посредством кодирования потока информационных символов в соответствии с заданной скоростью кодирования, используя кодер квазикомплементарного сдвоенного двоичного турбокода (QC-DBTC). Устройство содержит: селектор для вставки заранее определенного кодового символа в позицию, соответствующую проколотому (удаленному, перфорированному) символу среди принятых символов; блок обратного чередования для обратного чередования символов четности из символов, сформированных селектором; квадро-символьный преобразователь для квадро-преобразования систематических символов из символов, сформированных селектором; множество обращенных перемежителей для независимого обращенного перемежения квадро-преобразованных потоков систематических символов и "обратно чередованных" потоков символов четности; квадро-символьный обращенный преобразователь для обратного квадро-преобразования обращенно-перемеженного потока систематических символов; блок конкатенации кодовых символов для конкатенации выходных сигналов обратного квадро-символьного преобразователя с обращенно-перемеженными потоками символов четности; и QC-DBTC декодер для QC-DBTC декодирования конкатенированных потоков символов.

Краткое описание чертежей

Вышеупомянутые и другие задачи, признаки и преимущества настоящего изобретения станут более понятны из нижеследующего подробного описания со ссылками на сопроводительные чертежи, на которых:

фиг.1 изображает блок-схему, иллюстрирующую структуры физических каналов для передачи пользователю высокоскоростных данных в системе IEEE 802.16a, используя доступ на основе мультиплексирования с ортогональным частотным разделением сигналов (OFDM);

фиг.2 изображает блок-схему, иллюстрирующую структуры физических каналов для передачи данных пользователю в современной HPi системе передачи и обработки высокоскоростных данных;

фиг.3 изображает блок-схему, иллюстрирующую устройство для формирования сдвоенных двоичных турбокодов со скоростью кодирования R=1/2;

фиг.4 изображает блок-схему, иллюстрирующую устройство для формирования сдвоенных двоичных турбокодов с R=1/3;

фиг.5 изображает блок-схему, иллюстрирующую генератор QCTC символов в системе CDMA2000 1x EV-DV;

фиг.6 изображает блок-схему, иллюстрирующую структуру QC-DBTC кодера, имеющего скорость кодирования R=1/3 и использующего сдвоенные двоичные турбокоды согласно варианту осуществления настоящего изобретения;

фиг.7 изображает блок-схему, иллюстрирующую структуру приемника в QC-DBTC системе согласно варианту осуществления настоящего изобретения;

фиг.8 изображает блок-схему, иллюстрирующую структуру передатчика в QC-DBTC системе согласно другому варианту осуществления настоящего изобретения; и

фиг.9 изображает блок-схему, иллюстрирующую структуру передатчика в QC-DBTC системе согласно еще одному варианту осуществления настоящего изобретения.

На всех чертежах аналогичные ссылочные позиции относятся к аналогичным частям, компонентам и структурам.

Подробное описание примерных вариантов осуществления

Несколько примерных вариантов осуществления настоящего изобретения подробно описаны ниже, со ссылками на приложенные чертежи. В нижеследующем описании подробное описание известных функций и встроенных структур опущено для ясности.

Фиг.6 изображает блок-схему, иллюстрирующую структуру QC-DBTC кодера, имеющего скорость кодирования R=1/3 и использующего сдвоенные двоичные турбокоды согласно варианту осуществления настоящего изобретения. Со ссылками на фиг.6 приведено подробное описание структуры и работы QC-DBTC кодера, имеющего скорость кодирования R=1/3 и использующего сдвоенные двоичные турбокоды согласно варианту осуществления настоящего изобретения. На фиг.6 структура турбокодера 610 по существу идентична структуре турбокодера, описанного со ссылками на фиг.4. Фиг.4 изображает блок-схему, иллюстрирующую устройство для формирования сдвоенных двоичных турбокодов с R=1/3. Поэтому внутренняя структура турбокодера 610 описана со ссылками на фиг.4.

QC-DBTC кодер, проиллюстрированный на фиг.6, подобен по структуре обычному QCTC кодеру, использующему двоичные турбокоды, за исключением процесса обработки систематических символов. Эта особенность требуется, потому что в случае сдвоенных двоичных турбокодов, как показано на фиг.3 и 4, N_EP систематических символов разделяют на потоки А и B систематических символов, каждый состоящий из N_EP/2 систематических символов. Соответствующие символы A_i и B_i кодируются попарно посредством первого компонентного кодера 401 или кодируются попарно посредством второго компонентного кодера 403 после того, как были подвержены турбоперемежению посредством турбоперемежителя 402. То есть, каждая из пар А и В информационного потока определяется как пара информационных потоков, определяемая одним процессом перехода на решетчатой диаграмме каждого компонентного кодера, и размер потоков символов определен как N_EP/2. Поэтому QC-DBTC кодер, принимающий пары информационных потоков, выполняет классификацию символов на основании пар A_i и B_i символов, как проиллюстрировано на фиг.6. То есть A_i и B_i отображаются на квадро-символы перед тем, как будет осуществлено блочное перемежение.

Процесс кодирования подробно описан ниже. Для удобства описание приводится в отношении скорости R=1/3 сдвоенных двоичных турбокодов. Однако процесс кодирования может также применяться к сдвоенным двоичным турбокодам, имеющим скорость кодирования 1/2 или другие скорости кодирования, без изменения структуры или схемы кодирования сдвоенных двоичных турбокодов. Изменение скорости кодирования просто увеличивает количество групп символов четности, так что скорость кодирования уменьшается.

Процесс кодирования

Этап 1. Классификация выходных символов сдвоенных двоичных турбокодов

Как показано на фиг.6, турбокодер 610, использующий сдвоенные двоичные турбокоды с R=1/3 в качестве родительских (материнских) кодов, выполняет турбокодирование в отношении N_EP символов входной информации. Процесс турбокодирования по существу идентичен обычному процессу сдвоенного двоичного турбокодирования. Поэтому, сдвое