Устройство и способ кодирования/декодирования канала с использованием параллельного каскадного кода проверки на четность с низкой плотностью

Иллюстрации

Показать всеИзобретение относится к устройству и способу кодирования/декодирования канала с использованием параллельного каскадного кода проверки на четность с низкой плотностью (LDPC). Достигаемый технический результат - улучшение рабочих характеристик параллельного каскадного кода LDPC и поддержание переменной кодовой скорости. В устройстве кодирования первый кодер LDPC генерирует первый компонентный код LDPC в соответствии с принятыми информационными битами, перемежитель перемежает информационные биты в соответствии с заданным правилом перемежения, второй кодер LDPC генерирует второй компонентный код LDPC в соответствии с перемеженными информационными битами, контроллер выполняет операцию управления так, что информационные биты, первый компонентный код LDPC, который представляет собой первые биты проверки на четность, соответствующие информационным битам, и второй компонентный код LDPC, который представляет собой вторые биты проверки на четность, соответствующие информационным битам, комбинируют в соответствии с заданной кодовой скоростью. 4 н. и 36 з.п. ф-лы, 8 ил.

Реферат

Настоящее изобретение, в общем, относится к устройству и способу кодирования/декодирования канала и, в частности, к устройству и способу кодирования/декодирования канала, в котором используются параллельные каскадные коды проверки на четность с низкой плотностью.

Описание предшествующего уровня техники

С учетом быстрого прогресса немобильных средств систем связи, технология передачи большого объема данных и вплоть до уровня пропускной способности, имеющего место в настоящее время в кабельных сетях, должна быть усовершенствована для ее применения в беспроводных сетях. Поскольку существует потребность в высокоскоростных системах связи с высокой пропускной способностью, которые позволяли бы обрабатывать и передавать различную информацию, такую как данные изображения и данные радиосвязи, а также данные простой голосовой услуги, необходимо повысить эффективность передачи данных в системе, с использованием соответствующей схемы кодирования канала, для улучшения рабочих характеристик системы. Однако в мобильных системах связи неизбежно возникают проблемы, связанные с ошибками, появляющимися в результате шумов, взаимных помех и замирания, в соответствии с условиями в канале во время передачи данных. Возникновение ошибок приводит к потере информационных данных.

Для уменьшения потерь информационных данных в результате возникновения ошибок можно улучшить надежность мобильных систем связи за счет использования различных схем контроля ошибок. В наиболее широко используемой схеме контроля ошибок используется код с исправлением ошибок. Ниже приведено описание турбокода и кода проверки на четность с низкой плотностью (LDPC), которые представляют собой типичные коды с исправлением ошибок.

A. Турбокод

Известно, что турбокод позволяет существенно улучшить рабочие характеристики по сравнению со сверточным кодом, обычно используемым для исправления ошибок при высокоскоростной передаче данных. Турбокод является предпочтительным в том, что позволяет эффективно исправлять ошибку, вызванную шумами, генерируемыми в канале передачи, повышая, таким образом, надежность передачи данных.

B. Код LDPC

Код LDPC может быть декодирован с использованием алгоритма итерационного декодирования на основе алгоритма суммирования-произведения на факторном графе. Поскольку в декодере для кода LDPC используется итерационный алгоритм декодирования на основе алгоритма суммирования-произведения, он имеет меньшую сложность, чем декодер для турбокода. Кроме того, декодер для кода LDPC легче выполнить с использованием декодера параллельной обработки, по сравнению с декодером для турбокода.

Теорема кодирования канала Шеннона показывает, что надежная связь возможна только со скоростью передачи данных, не превышающей пропускную способность канала. Однако теорема кодирования канала Шеннона не предложила детального метода кодирования/декодирования канала для поддержания скорости передачи данных вплоть до максимального предела пропускной способности канала. Обычно, хотя случайный код, имеющий очень большой размер блока, проявляет рабочие характеристики, приближающиеся к пределу пропускной способности канала в соответствии с теоремой кодирования канала Шеннона, в случае, когда используется схема декодирования MAP (максимума апостериорной вероятности) или ML (максимального правдоподобия), такую схему декодирования невозможно выполнить на практике из-за связанной с ней высокой вычислительной нагрузки.

Турбокод был предложен Берро (Berrou), Главье (Glavieux) и Титимаджима (Thitimajshima) в 1993 г. и обладает исключительными характеристиками, приближающимися к предельной пропускной способности канала, в соответствии с теоремой кодирования канала Шеннона. Предложение турбокода дало толчок активным исследованиям итерационного декодирования и графического выражения кодов, и в настоящее время в центре внимания находятся коды LDPC, предложенные Gallager в 1962 г. В факторном графе турбокода и кода LDPC существуют циклы, и хорошо известно, что итерационное декодирование на факторном графе кода LDPC, в котором существуют циклы, является субоптимальным. Кроме того, экспериментально было доказано, что код LDPC обладает исключительными характеристиками, благодаря итерационному декодированию. Известно, что код LDPC обладает наивысшими характеристиками, и иногда его рабочие характеристики отличаются только приблизительно на 0,04 [дБ] от предела пропускной способности канала в соответствии с теоремой кодирования канала Шеннона при частоте ошибочных битов (BER) 10-5, при использовании блока размером 107. Кроме того, хотя код LDPC, определенный полем Галуа (Galois) (GF) при q>2, то есть GF(q) увеличивается по сложности в процессе его декодирования, его характеристики намного превышают двоичный код. Однако не было предложено удовлетворительное теоретическое описание успешного декодирования с использованием алгоритма итерационного декодирования для кода LDPC, определенного в GF(q).

Код LDPC, предложенный Галлахером (Gallager), определен матрицей проверки на четность, в которой основные элементы имеют величину 0, и меньшинство элементов, за исключением элементов, имеющих величину 0, имеют величину, не равную 0, например, 1. Например, код (N, j, k) LDPC представляет собой код линейного блока, имеющий длину N блока и определенный разреженной матрицей проверки на четность, в которой каждый столбец имеет j элементов, имеющих величину 1, каждая строка имеет k элементов, имеющих величину 1, и все элементы, за исключением элементов, имеющих величину 1, имеют величину 0.

Код LDPC, в котором вес каждого столбца в матрице проверки на четность фиксирован значением "j" и вес каждой строки в матрице проверки на четность фиксирован значением "k", как указано выше, называется "регулярным кодом LDPC". Здесь "вес" обозначает количество элементов, имеющих ненулевую величину среди элементов, составляющих генерирующую матрицу и матрицу проверки на четность. В отличие от регулярного кода LDPC код LDPC, в котором не фиксирован вес каждого столбца в матрице проверки на четность или вес каждой строки в матрице проверки на четность, называется "нерегулярным кодом LDPC". Общеизвестно, что нерегулярный код LDPC обладает более высокими характеристиками по сравнению с регулярным кодом LDPC. Однако, в случае нерегулярного кода LDPC, поскольку вес каждого столбца или вес каждой строки в матрице проверки на четность не фиксирован, то есть является нерегулярным, вес каждого столбца в матрице проверки на четность или вес каждой строки в матрице проверки на четность должны быть соответствующим образом отрегулированы для того, чтобы гарантировать высокие рабочие характеристики.

Далее, со ссылкой на фиг. 1, приведено описание матрицы проверки на четность кода (8, 2, 4) LDPC, в качестве примера кода (N, j, k) LDPC.

На фиг. 1 показана схема, иллюстрирующая матрицу проверки на четность общего кода (8, 2, 4) LDPC. Как показано на фиг. 1, матрица H проверки на четность кода (8, 2, 4) LDPC состоит из 8 столбцов и 4 строк, в которой вес каждого столбца является фиксированным, равным 2, и вес каждой строки является фиксированным, равным 4. Поскольку вес каждого столбца и вес каждой строки в матрице проверки на четность является регулярным, как указано выше, код (8, 2, 4) LDPC, представленный на фиг. 1, становится регулярным кодом LDPC.

На фиг. 2 показана схема, иллюстрирующая факторный граф кода (8, 2, 4) LDPC по фиг. 1. Как показано на фиг. 2, факторный граф кода (8, 2, 4) LDPC состоит из 8 переменных узлов x1 211,x2 213,x3 215,x4 217,x5 219,x6 221,x7 223 иx8 225 и 4 проверочных узлов 227, 229, 231 и 233. Когда элемент, имеющий величину 1, то есть ненулевую величину, существует в точке, где i-я строка и j-й столбец матрицы проверки на четность кода (8, 2, 4) LDPC пересекаются друг с другом, создается ответвление между переменным узлом xi и j-м проверочным узлом.

Поскольку матрица проверки на четность кода LDPC имеет очень малый вес, как описано выше, возможно выполнить декодирование, используя итерационное декодирование даже в блочном коде, имеющем относительно большую длину, который проявляет рабочие характеристики, приближающиеся к пределу пропускной способности канала Шеннона, такого, как турбокод, при постоянном увеличении длины блока блочного кода. МакКей (MacKay) и Нил (Neal) доказали, что процесс итерационного декодирования кода LDPC с использованием схемы передачи потока приближается к процессу итерационного декодирования турбокода по своим рабочим характеристикам.

Для генерирования кода LDPC с высокими рабочими характеристиками должны удовлетворяться следующие условия.

(1) Следует учитывать циклы на факторном графе кода LDPC. Термин "цикл" относится к петле, формируемой ребрами, соединяющими переменные узлы с проверочными узлами на факторном графе кода LDPC, и длина цикла определяется, как количество ребер, составляющих петлю. Цикл с большой длиной означает, что количество ребер, соединяющих переменные узлы с проверочными узлами, составляющими петлю в факторном графе кода LDPC, велико. В отличие от этого цикл с малой длиной означает, что количество ребер, соединяющих переменные узлы с проверочными узлами, составляющими петлю в факторном графе кода LDPC, мало.

По мере того как циклы в факторном графе кода LDPC становятся более длинными, эффективность рабочей характеристики кода LDPC увеличивается по следующим причинам. Так, когда длинные циклы генерируются в факторном графе кода LDPC, становится возможным предотвратить ухудшение рабочих характеристик, например, минимального уровня ошибок, возникающего, когда слишком много циклов с короткой длиной существуют в факторном графе кода LDPC.

(2) Следует учитывать эффективное кодирование кода LDPC.

При использовании кода LDPC более трудно выполнить кодирование в режиме реального времени по сравнению со сверточным кодом или турбокодом из-за его высокой сложности кодирования. Для уменьшения сложности кодирования кода LDPC был предложен код повторного накопления (RA). Однако код RA также обладает ограничением в отношении уменьшения сложности кодирования кода LDPC, поэтому необходимо учитывать эффективное кодирование кода LDPC.

(3) Следует учитывать распределение степени на факторном графе кода LDPC.

Обычно нерегулярный код LDPC обладает более высокими характеристиками по сравнению с регулярным кодом LDPC, поскольку факторный граф нерегулярного кода LDPC имеет различные степени. Термин "степень" относится к количеству ребер, соединенных с переменными узлами и проверочными узлами на факторном графе кода LDPC. Кроме того, фраза "степень распределения" на факторном графе кода LDPC относится к отношению количества узлов, имеющих конкретную степень, к общему количеству узлов. Ричардсон (Richardson) доказал, что код LDPC, имеющий конкретную степень распределения, обладает исключительными рабочими характеристиками.

Как описано выше, хорошо известно, что код LDPC, так же как и турбокод, позволяет существенно улучшить рабочие характеристики при высокоскоростной передаче данных, и код LDPC является предпочтительным в том, что он позволяет эффективно исправлять ошибки, создаваемые шумами, генерируемыми в канале передачи, повышая, таким образом, надежность передачи данных. Однако код LDPC обладает худшими характеристиками с учетом кодовой скорости. То есть, поскольку код LDPC имеет относительно высокую кодовую скорость, он не является свободным с точки зрения кодовой скорости.

В случае используемых в настоящее время кодов LDPC большинство из них имеют кодовую скорость 1/2 и только некоторые имеют кодовую скорость 1/3. Ограничение кодовой скорости оказывает фатальное влияние на высокоскоростную передачу данных с высокой пропускной способностью. Конечно, хотя распределение степени, представляющее наилучшие рабочие характеристики, можно рассчитать с использованием метода эволюции плотности для реализации относительно низкой кодовой скорости для кода LDPC, трудно реализовать код LDPC, имеющий распределение степени, представляющее наилучшую рабочую характеристику, из-за различных ограничений, таких как структура цикла на факторном графе и реализация аппаратных средств.

По мере развития мобильных систем связи нашли применение различные схемы передачи данных, такие как схема гибридного автоматического запроса на повторную передачу данных (HARQ) и схема адаптивной модуляции и кодирования (AMC) для повышения эффективности ресурсов. Ниже приведено описание схемы HARQ и схемы AMC.

Система связи, в которой используется схема HARQ, должна создавать коды, имеющие различные кодовые скорости, с использованием однокомпонентного кода. То есть схема HARQ повышает свою эффективность при использовании схемы мягкого комбинирования. Схема мягкого комбинирования классифицирована на схему комбинирования с отслеживанием (CC) и схему инкрементной избыточности (IR). В схеме CC на стороне передачи используются одни и те же данные как для исходной передачи, так и для повторной передачи. То есть в схеме CC, если m символов передавались как один кодированный блок при исходной передаче, те же m символов передаются как один кодированный блок, даже при повторной передаче. Термин "кодированный блок" относится к пользовательским данным, передаваемым за один интервал времени передачи (TTI). То есть в схеме CC одна и та же кодовая скорость используется как для исходной передачи, так и для повторной передачи. Затем на стороне приема выполняется мягкое комбинирование первоначально переданного кодированного блока с повторно переданным кодированным блоком, и выполняется операция контроля с помощью циклического избыточного кода (CRC) в мягко комбинированном кодированном блоке для определения, имеется ли ошибка в мягко комбинированном кодированном блоке.

Однако в схеме IR на стороне передачи используются данные с разными форматами для исходной передачи и повторной передачи. Например, если пользовательские данные размером n битов кодируются в канале с получением m символов, сторона передачи передает только некоторые из m символов при исходной передаче и последовательно передает остальные символы при повторной передаче. То есть в схеме IR используются разные кодовые скорости для исходной передачи и повторной передачи. Затем на стороне приема формируются кодированные блоки, имеющие высокую кодовую скорость передачи, путем каскадного объединения повторно переданных кодированных блоков до конца первоначально переданных кодированных блоков, и затем выполняется исправление ошибок. В схеме IR кодированный блок, переданный в исходной передаче, и кодированные блоки, переданные при повторной передаче, идентифицируют по их номерам версии. Например, кодированному блоку, повторно передаваемому при исходной передаче, присваивается № 1 версии, кодированному блоку, передаваемому при первой передаче, присваивается № 2 версии и кодированному блоку, передаваемому при второй повторной передаче, присваивается № 3 версии, и сторона приема может выполнить мягкое комбинирование первоначально переданного кодированного блока с повторно переданным кодированным блоком с использованием номеров версий.

Схема AMC адаптивно выбирает схему модуляции и схему кодирования, используемые для каждого канала в соответствии с характеристикой отклика канала для каждого канала. Термин "схема кодирования" относится к схеме, предназначенной для выбора, например, кодовой скорости. Схема AMC имеет множество схем модуляции и множество схем кодирования и модулирует и кодирует сигнал путем комбинирования схем модуляции и схем кодирования. Обычно комбинации схем модуляции и схем кодирования называют "схемой модуляции и кодирования (MCS)" и в ней может быть определено множество MCS с уровнем от № 1 до № N. То есть схема AMC адаптивно выбирает уровень MCS в соответствии с характеристикой отклика канала между стороной передачи или базовой станцией (BS) и стороной приема или абонентской станцией (SS), повышая, таким образом, эффективность системы.

Как описано выше, когда используются схемы HARQ и AMC, необходимо поддерживать разные кодовые скорости. Однако, поскольку код LDPC имеет ограничения в отношении кодовой скорости, как описано выше, трудно использовать схемы HARQ и AMC для кода LDPC. Таким образом, требуется схема кодирования/декодирования канала, позволяющая поддерживать различные кодовые скорости с использованием кода LDPC.

Сущность изобретения

Таким образом, целью настоящего изобретения является создание устройства и способа кодирования/декодирования канала с использованием параллельного каскадного кода LDPC.

Другой целью настоящего изобретения является создание устройства и способа кодирования/декодирования канала с использованием параллельного каскадного кода LDPC, который позволяет поддерживать переменную кодовую скорость.

Кроме того, другой целью настоящего изобретения является разработка устройства и способа перемежения для устройства кодирования канала, для улучшения рабочих характеристик параллельного каскадного кода LDPC.

В соответствии с первым аспектом настоящего изобретения предложено устройство кодирования канала, в котором используется параллельный каскадный код проверки на четность с низкой плотностью (LDPC). Устройство кодирования канала содержит первый кодер LDPC для генерирования первого компонентного кода LDPC в соответствии с принятыми информационными битами, перемежитель для перемежения информационных битов в соответствии с заданным правилом перемежения, второй кодер LDPC для генерирования второго компонентного кода LDPC в соответствии с перемеженными информационными битами и контроллер для выполнения операции управления так, что информационные биты, первый компонентный код LDPC и второй компонентный код LDPC комбинируются вместе в соответствии с заданной кодовой скоростью.

В соответствии со вторым аспектом настоящего изобретения предложен способ кодирования канала, в котором используется параллельный каскадный код проверки на четность с низкой плотностью (LDPC). Способ кодирования канала содержит этапы генерирования первого компонентного кода LDPC в соответствии с принятыми информационными битами, перемежения информационных битов в соответствии с определенным правилом перемежения, генерирования второго компонентного кода LDPC в соответствии с перемеженными информационными битами и выполнения операции управления таким образом, чтобы информационные биты, первый компонентный код LDPC и второй компонентный код LDPC были скомбинированы и переданы в соответствии с заранее определенной кодовой скоростью.

В соответствии с третьим аспектом настоящего изобретения предложено устройство декодирования канала, в котором используется параллельный каскадный код проверки на четность с низкой плотностью (LDPC), имеющий информационные биты и первый и второй биты проверки на четность, соответствующие информационным битам. Устройство декодирования канала содержит первый декодер LDPC для генерирования первого компонентного кода LDPC после приема сигнала путем декодирования информации, обновленной во время предыдущего декодирования, выводимой из второго декодера LDPC, и информационных битов и первых битов проверки на четность в принятом сигнале, первый оператор "исключающее ИЛИ" (XOR), предназначенный для вычитания обновленной информации из сигнала, выводимого из первого декодера LDPC, перемежитель для перемежения сигнала с выхода первого оператора "исключающее ИЛИ", в соответствии с заданным правилом перемежения, второй декодер LDPC для генерирования второго компонентного кода LDPC путем декодирования сигнала с выхода перемежителя, второй оператор "исключающее ИЛИ" для вычитания сигнала с выхода перемежителя из сигнала с выхода второго декодера LDPC, обращенный перемежитель для обращенного перемежения сигнала с выхода второго оператора "исключающее ИЛИ" в соответствии с правилом обращенного перемежения, соответствующего правилу перемежения, и вывода сигнала после обращенного перемежения в первый декодер LDPC и первый оператор "исключающее ИЛИ", контроллер для управления правилом перемежения и правилом обращенного перемежения и контроллер кодовой скорости для выполнения управления операцией таким образом, что выходной результат первого декодера LDPC или второго декодера LDPC выводится в качестве окончательно декодированных битов в соответствии с заданной кодовой скоростью.

В соответствии с четвертым аспектом настоящего изобретения предложен способ декодирования канала, в котором используется параллельный каскадный код проверки на четность с низкой плотностью (LDPC), имеющий информационные биты и первый и второй биты проверки на четность, соответствующие информационным битам. Способ декодирования канала содержит этапы генерирования первого компонентного кода LDPC после приема сигнала путем декодирования информации, обновленной во время предыдущего декодирования, и информационных битов и первых битов проверки на четность в принятом сигнале, вычитания обновленной информации из первого компонентного кода LDPC, перемежения сигнала, полученного путем вычитания обновленной информации из первого компонентного кода LDPC в соответствии с заранее определенным правилом перемежения, генерирования второго компонентного кода LDPC путем декодирования перемежающегося сигнала, вычитания перемеженного сигнала из второго компонентного кода LDPC, обращенного перемежения сигнала, полученного путем вычитания перемеженного сигнала из второго компонентного кода LDPC в соответствии с правилом обращенного перемежения, соответствующим правилу перемежения, и вывода первого компонентного кода LDPC или второго компонентного кода LDPC в качестве окончательно декодированных битов в соответствии с заданной кодовойскоростью.

Краткое описание чертежей

Описанные выше и другие цели, признаки и преимущества настоящего изобретения поясняются в последующем подробном описании, иллюстрируемом чертежами, на которых показано следующее:

фиг. 1 - схема, представляющая матрицу проверки на четность общего кода (8, 2, 4) LDPC;

фиг. 2 - схема, представляющая факторный граф кода (8, 2, 4) LDPC по фиг. 1;

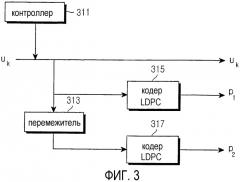

фиг. 3 - схема, иллюстрирующая внутреннюю структуру устройства кодирования канала, с использованием параллельного каскадного кода LDPC в соответствии с вариантом выполнения настоящего изобретения;

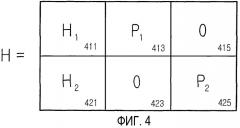

фиг. 4 - схема, иллюстрирующая матрицу проверки на четность, для случая, когда параллельный каскадный код LDPC по фиг. 3 рассматривается как один код LDPC;

фиг. 5 - схема, иллюстрирующая факторный граф параллельного каскадного кода LDPC, в котором используются те же коды LDPC, что и компонентные коды;

фиг. 6 - схема, иллюстрирующая внутреннюю структуру устройства для декодирования параллельного каскадного кода LDPC, в соответствии с вариантом выполнения настоящего изобретения;

фиг. 7 - схема, иллюстрирующая правило конструирования перемежителя на основе Правила 1, в соответствии с вариантом выполнения настоящего изобретение; и

фиг. 8 - схема, иллюстрирующая правило конструирования перемежителя на основе Правила 2 и Правила 3, в соответствии с вариантом выполнения настоящего изобретения.

Подробное описание предпочтительного варианта осуществления

Предпочтительный вариант осуществления настоящего изобретения подробно описан ниже со ссылкой на прилагаемые чертежи. В следующем описании подробное изложение известных функций и конфигураций исключено для краткости.

В настоящем изобретении предложены устройство и способ для кодирования/декодирования сигнала канала с использованием параллельного каскадного кода проверки на четность с низкой плотностью (LDPC), который позволяет поддерживать различные кодовые скорости. В различных схемах, предложенных для надежной передачи/приема большого объема данных с высокой скоростью, таких как схема гибридного автоматического запроса на повторную передачу данных (HARQ) и схема адаптивной модуляции и кодирования (AMC), должны поддерживаться различные кодовые скорости. Поэтому в настоящем изобретении предложены устройство и способ кодирования/декодирования канала с использованием параллельного каскадного кода LDPC, который позволяет поддерживать переменную кодовую скорость. Для обеспечения максимальных рабочих характеристик параллельного каскадного кода LDPC в настоящем изобретении предложено правило перемежения между компонентными кодами LDPC, составляющими параллельный каскадный код LDPC.

На фиг. 3 показана схема, иллюстрирующая внутреннюю структуру устройства кодирования канала с использованием параллельного каскадного кода LDPC, в соответствии с вариантом выполнения настоящего изобретения. Как показано на фиг. 3, устройство кодирования канала состоит из контроллера 311, перемежителя 313 и кодеров 315 и 317 LDPC. В устройстве кодирования канала, предложенном в настоящем изобретении, используется параллельная каскадная структура кода LDPC, аналогичная параллельной каскадной структуре турбокода, чтобы, таким образом, можно было изменять кодовую скорость. Обычно два основных фактора, определяющих рабочие характеристики турбокода, включают в себя выбор сверточного кода для использования в качестве компонентного кода и метод проектирования перемежителя, включенного между компонентными кодами. Перемежитель имеет функцию перестановки, то есть функцию определения информационного бита другого компонентного кода, на который должен быть отображен определенный информационный бит одного компонентного кода. В устройстве кодирования канала, в котором используется турбокод, если перемежитель спроектирован ненадлежащим образом, то может быть сформирован код, имеющий очень короткое свободное расстояние, что оказывает негативное влияние на рабочие характеристики кода. Обычно математически просто выполнить поиск компонентного кода, обладающего исключительными рабочими характеристиками. Однако математический подход к проектированию перемежителя является не простым, и если перемежитель спроектирован ненадлежащим образом, то турбокод, генерируемый с использованием перемежителя, может уступать по эффективности турбокоду, сформированному с использованием простого случайного перемежителя.

Эффективность параллельного каскадного кода LDPC так же, как и эффективность турбокода, в основном, зависит от схемы перемежителя 313. Кроме того, эффективность параллельного каскадного кода LDPC, аналогично эффективности турбокода, в основном, зависит от того, как сформирован код LDPC, используемый в качестве компонентного кода. Как показано на чертеже, входные информационные битыuk подаются в кодер 315 LDPC, перемежитель 313 и на выходной вывод. Кодер 315 LDPC генерирует первые биты p1 проверки на четность в соответствии со входными информационными битамиuk. Поскольку процесс генерирования первых битов p1 проверки на четность в соответствии со входными информационными битамиuk с помощью кодера 315 LDPC не имеет непосредственного отношения к настоящему изобретению, подробное его описание здесь не приводится. Перемежитель 313 выполняет перемежение входных информационных битовuk в соответствии с заданной функцией перестановки и выводит перемежающиеся информационные биты в кодер 317 LDPC. Кодер 317 LDPC генерирует вторые биты p2 проверки на четность с использованием перемежающегося сигнала, поступающего с выхода перемежителя 313. Поскольку процесс генерирования вторых битов p2 проверки на четность с использованием перемежающегося сигнала, поступающего с выхода перемежителя 313, с помощью кодера 317 LDPC не имеет непосредственного отношения к настоящему изобретению, подробное его описание здесь не приводится. Кроме того, ниже описаны операции перемежителя 313.

Контроллер 311 управляет выходом устройства кодирования канала в соответствии с условиями в канале. Например, когда условия в канале относительно хорошие, контроллер 311 выполняет операцию управления так, что передают только информационные битыuk и первые биты p1 проверки на четность. Когда условия в канале относительно плохие, контроллер 311 выполняет операцию управления так, что передают не только информационные битыuk и первые биты p1 проверки на четность, но также и вторые биты p2 проверки на четность. В результате управления количеством передаваемых битов таким способом контроллер 311 может управлять кодовой скоростью. Хотя изобретение описано со ссылкой на пример, в котором контроллер 311 управляет кодовой скоростью в соответствии с условиями в канале, изобретение также применимо в случае, когда контроллер 311 управляет кодовой скоростью в системе связи, в которой используется схема HARQ.

Параллельный каскадный код LDPC, описанный со ссылкой на фиг. 3, может рассматриваться как один код LDPC, имеющий матрицу проверки на четность. Со ссылкой на фиг. 4 ниже приведено описание матрицы проверки на четность для случая, когда параллельный каскадный код LDPC, описанный со ссылкой на фиг. 3, рассматривается как один код LDPC.

На фиг. 4 показана схема, иллюстрирующая матрицу проверки на четность для случая, когда параллельный каскадный код LDPC по фиг. 3 рассматривается как один каскадный код LDPC. Прежде чем будет приведено описание фиг. 4, следует отметить, что поскольку код LDPC, поступающий с выхода кодера 315 LDPC, и код LDPC, поступающий с выхода кодера 317 LDPC, рассматриваются как разные компонентные коды для параллельного каскадного кода LDPC, описанного со ссылкой на фиг. 3, и на стороне приема выполняется последовательное декодирование компонентных кодов, характеристики декодирования компонентных кодов отличаются от характеристики декодирования одного кода LDPC. Разница между операцией декодирования параллельного каскадного кода LDPC и операцией декодирования кода LDPC описана ниже.

Как показано на фиг. 4, код LDPC, поступающий с выхода кодера 315 LDPC по фиг. 3, который представляет собой первый компонентный код, может быть выражен как H1 411 и P1 413 матрицы H проверки на четность, представленной на фиг. 4, и в этом случае проверка на четность кода LDPC, поступающего с выхода кодера 317 LDPC, который представляет собой второй компонентный код, дополнена нулем (0) 415. Здесь код LDPC, поступающий с выхода кодера 315 LDPC, называется "первым компонентным кодом LDPC" и код LDPC, поступающий с выхода кодера 317 LDPC, называется "вторым компонентным кодом LDPC". H1 411 представляет частичную матрицу, соответствующую информационной части первого компонентного кода LDPC, и P1 413 и 0 415 представляют частичные матрицы, соответствующие части проверки на четность первого компонентного кода LDPC. В варианте выполнения настоящего изобретения только P1 413 соответствует части проверки на четность первого компонентного кода LDPC. Аналогично код LDPC с выхода кодера 317 LDPC, который представляет собой второй компонентный код, может быть выражен какH2 421 иP2 425 матрицы H проверки на четность, и в этом случае проверка на четность кода LDPC с выхода кодера 315 LDPC, который представляет собой первый компонентный код, дополнена нулем (0) 423.H2 421 представляет собой частичную матрицу, соответствующую информационной части второго компонентного кода LDPC, и 0 423 иP2 425 представляют частичные матрицы, соответствующие части проверки на четность второго компонентного кода LDPC. В варианте выполнения в соответствии с настоящим изобретением толькоP2 425 соответствует части проверки на четность второго компонентного кода LDPC.

Поскольку перемежитель 313 выполняет операцию перемежения в соответствии с заданной функцией перестановки, как описано выше, удовлетворяется соотношение H2=π1H1. Хотя необязательно, чтобы первый компонентный код LDPC был идентичным второму компонентному коду LDPC, предпочтительно, чтобы они были идентичными друг другу, когда учитывается сложность декодера канала на стороне приема. Поэтому на фиг. 4 предполагается, что P1 и P2 идентичны.

На фиг. 5 представлена схема, иллюстрирующая факторный граф параллельного каскадного кода LDPC, который использует те же коды LDPC, что и компонентные коды. Как показано на фиг. 5, ссылочной позицией 510 обозначены проверочные узлы первого компонентного кода LDPC, ссылочной позицией 520 обозначена функция π2 перестановки, представляющая конфигурацию факторного графа для первого компонентного кода LDPC, ссылочной позицией 530 обозначены информационные битыuk первого компонентного кода LDPC, и ссылочной позицией 540 обозначены первые биты p1 проверки на четность первого компонентного кода LDPC. Функция π2 перестановки (520), представляющая конфигурацию первого компонентного кода LDPC, представляет, как проверочные узлы соединены с переменными узлами, и как только функция π2 (520) перестановки будет определена, может быть сформирована матрица проверки на четность первого компонентного кода LDPC. Поскольку конфигурация цикла факторного графа для первого компонентного кода LDPC изменяется в соответствии с тем, как выбирается функция π2 (520) перестановки, проектирование функции π2 (520) перестановки действует как очень важный фактор в определении эффективности кода LDPC. Поскольку проектирование функции π2 (520) перестановки для создания кода LDPC, имеющего высокую эффективность, не относится непосредственно к настоящему изобретению, ее подробное описание не приводится.

Кроме того, ссылочной позицией 550 обозначена функция π1 перестановкиперемежителя 313 по фиг. 3, ссылочной позицией 560 обозначены вторые биты p2 проверки начетностьвторого компонентного кода LDPC, ссылочной позицией 570 обозначена функция π2 перестановки, представляющая конфигурацию факторного графа для второго компонентного кода LDPC, и ссылочной позицией 580 обозначены проверочные узлы второго компонентного кода LDPC. Поскольку на фиг. 3 предполагается, что кодер 315 LDPC идентичен коду 317 LDPC, функция π2 (570) перестановки, представляющая конфигурацию графа фактора второго компонентного кода LDPC, также идентична функции π2 (520) перестановки, представляющей конфигурацию факторного графа первого компонентного кода LDPC.

Как описано со ссылкой на фиг. 5, факторный граф параллельного каскадного кода LDPC имеет конфигурацию, в которой только два компонентных кода LDPC включены между информационными битами через перемежитель. Поэтому может быть выполнено итерационное декодирование в последовательной схеме декодирования так, что вначале будет декодироваться часть, соответствующая первому компонентному коду LDPC, и когда значение переменного узла, соответствующего информационной части первого компонентного кода LDPC, будет выдано через перемежитель, будет декодироваться часть, соответствующая второму компонентному коду LDPC.

Ниже приведено подробное описание схемы, в которой используется параллельный каскадный код LDPC в системе связи с использованием схем HARQ и AMC.

В беспроводной системе связи, поскольку ресурсы мощности базовой станции (BS) или абонентской станции (АС, SS) ограничены, невозможно передавать сигналы с максимальной мощностью передачи для исключения ошибок передачи данных. Схемы HARQ и AMC представляют собой схемы передачи, введенные для выполнения эффективной связи с использованием ограниченной мощности. Как описано выше, система связи, в которой используется схема HARQ, повторно передает искаженные данные в соответствии с условиями в канале, с использованием кодера канала, имеющего различные кодовые скорости для искаженных данных.

Как описано выше, кодовая скорость параллельного каскадного кода LDPC может изменяться в соответствии с тем, какой из компонентных кодов LDPC следует выбрать и какое количество компонентных кодов LDPC должно каскадно комбинироваться. Параллельный каскадный код LDPC, кодовая скорость которого изменяется, подходит для системы связи с использованием схемы HARQ. Как описано выше, эффективность параллельного каскадного кода LDPC, в основном, зависит от того, как спроектирован перемежитель, включенный между кодерами LDPC, генерирующими компонентные коды LDPC, а также как выбирается компонентный код LDPC и какое количество компонентных кодов LDPC компонента будет каскадироваться. Поэтому в