Выходной каскад операционного усилителя

Иллюстрации

Показать всеИспользование: в структуре аналоговых микросхем различного функционального назначения. Технический результат заключается в обеспечении защиты по току нагрузки. Выходной каскад операционного усилителя, содержащий входные p-n-p (1) и n-p-n (2) транзисторы, базы которых связаны друг с другом, эмиттеры соединены с первым (3) и вторым (4) источниками тока и базами выходных n-p-n (5) и p-n-p (6) транзисторов, причем эмиттеры выходных (5) и (6) транзисторов связаны с нагрузкой (7), отличается тем, что в схему введены первое (8) на p-n-p транзисторах и второе (9) на n-p-n транзисторах токовые зеркала, коллектор выходного транзистора (5) соединен с коллекторным выходом первого токового зеркала (8), коллектор выходного транзистора (6) соединен с коллекторным выходом второго токового зеркала (9), причем вышеуказанные выходные транзисторы (5) и (6) соединены через соответствующие первое (8) и второе (9) токовые зеркала с шинами питания, вход (10) первого токового зеркала (8) соединен с выходом первого источника опорного тока (11), а вход (12) второго токового зеркала (9) соединен с выходом второго источника опорного тока (13). 9 з.п. ф-лы, 12 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного устройства для усиления аналоговых сигналов по мощности (буферного усилителя), в структуре аналоговых микросхем различного функционального назначения, операционных усилителях.

Известны схемы двухтактных выходных каскадов на n-p-n и p-n-p транзисторах [1], которые стали одним из базовых элементов многих аналоговых микросхем, широко используются в структуре различных УНЧ и операционных усилителях. Благодаря хорошим статическим и другим характеристикам такие выходные каскады получили специальное название «бриллиантовые» транзисторы. На их совершенствование выдано более 50 патентов в разных странах [1-50].

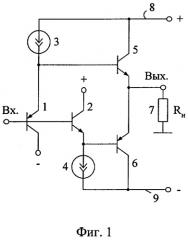

Ближайшим прототипом (фиг.1) заявляемого устройства является выходной каскад, описанный в патенте США №5323122, содержащий входные p-n-p 1 и n-p-n 2 транзисторы, базы которых связаны друг с другом, эмиттеры соединены с первым 3 и вторым 4 источниками тока и базами выходных n-p-n 5 и p-n-p 6 транзисторов, причем эмиттеры выходных n-p-n 5 и p-n-p 6 транзисторов связаны с нагрузкой 7.

Существенный недостаток известного устройства состоит в том, что оно не обеспечивает защиту по току нагрузки, что снижает надежность микросхем при коротких замыканиях на выходе.

Основная цель предлагаемого изобретения состоит в обеспечении ограничения выходного тока Iн при достижении им заданного значения Iогр, величина которого может устанавливаться путем изменения некоторого опорного тока, пропорционального, например, напряжению в нагрузке, температуре, напряжению источников питания и т.д.

Поставленная цель достигается тем, что в выходной каскад (ВК) фиг.1, содержащий входные p-n-p 1 и n-p-n 2 транзисторы, базы которых связаны друг с другом, эмиттеры соединены с первым 3 и вторым 4 источниками тока и базами выходных n-p-n 5 и p-n-p 6 транзисторов, причем эмиттеры выходных n-p-n 5 и p-n-p 6 транзисторов связаны с нагрузкой 7, предусмотрены новые элементы и связи - в схему введены первое (8) на p-n-p транзисторах и второе (9) на n-p-n транзисторах токовые зеркала, коллектор выходного n-p-n транзистора (5) соединен с коллекторным выходом первого токового зеркала (8), коллектор выходного p-n-p транзистора (6) соединен с коллекторным выходом второго токового зеркала (9), причем вышеуказанные выходные транзисторы (5) и (6) соединены через соответствующие первое (8) и второе (9) токовые зеркала с шинами питания, вход (10) первого токового зеркала (8) на p-n-p транзисторах соединен с выходом первого источника опорного тока (11), а вход (12) второго токового зеркала (9) на n-p-n транзисторах соединен с выходом второго источника опорного тока (13).

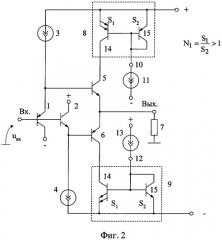

Схема заявляемого устройства в соответствии с п.1, п.2 формулы изобретения показана на фиг.2.

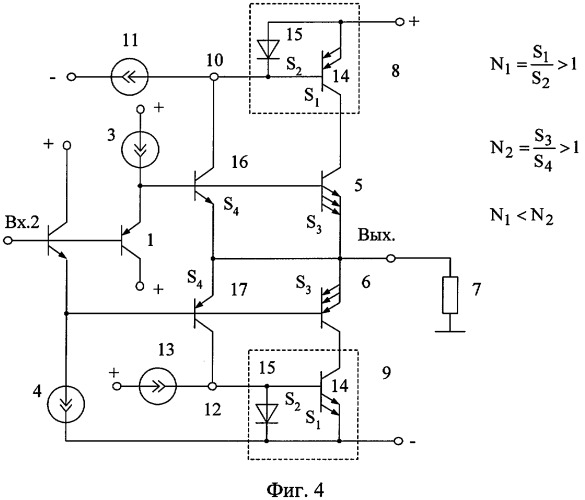

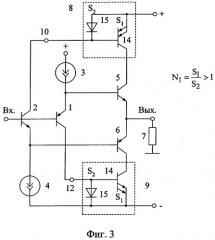

На фиг.3 показан заявляемый ВК в соответствии с п.3 формулы изобретения. На фиг.4 и 5 показаны варианты выполнения заявляемого устройства в соответствии с п.4, п.5, п.6, п.7 формулы изобретения. На фиг.6 представлен заявляемый ВК в соответствии с п.8 формулы изобретения.

Результаты компьютерного моделирования ВК по п.3, а также по п.5 формулы изобретения представлены на фиг.7, 8, 9. Амплитудно-частотная характеристика выходного каскада фиг.2 на моделях интегральных транзисторов ФГУП НПП «Пульсар» и статических режимах, показанных на фиг.8, представлена на фиг.10.

На фиг.11 изображена схема источников опорного тока в соответствии с п.9 формулы изобретения. На фиг.12 дана схема источников опорного тока в соответствии с п.10 формулы изобретения.

Выходной каскад фиг.2 содержит входные p-n-p 1 и n-p-n 2 транзисторы, базы которых связаны друг с другом, эмиттеры соединены с первым 3 и вторым 4 источниками тока и базами выходных n-p-n 5 и p-n-p 6 транзисторов, причем эмиттеры выходных n-p-n 5 и p-n-p 6 транзисторов связаны с нагрузкой 7. В схему введены первое (8) на p-n-p транзисторах и второе (9) на n-p-n транзисторах токовые зеркала, коллектор выходного n-p-n транзистора (5) соединен с коллекторным выходом первого токового зеркала (8), коллектор выходного p-n-p транзистора (6) соединен с коллекторным выходом второго токового зеркала (9), причем вышеуказанные выходные транзисторы (5) и (6) соединены через соответствующие первое (8) и второе (9) токовые зеркала с шинами питания, вход (10) первого токового зеркала (8) на p-n-p транзисторах соединен с выходом первого источника опорного тока (11), а вход (12) второго токового зеркала (9) на n-p-n транзисторах соединен с выходом второго источника опорного тока (13). Каждое из токовых зеркал 8 и 9 содержит выходной 14 и входной 15 транзисторы с объединенными эмиттерами, а также объединенными базами, коллектор входного 15 транзистора соединен с базой выходного 14 транзистора, причем коэффициенты передачи по току N1 каждого из токовых зеркал 8 и 9, зависящие от отношения площадей эмиттерных переходов выходного 14 (S1) и входного 15 (S2) транзисторов токовых зеркал, выбираются больше единицы (N1=S1/S2).

В выходном каскаде фиг.3 в качестве первого источника опорного тока 11 используется коллектор входного n-p-n 2 транзистора, а в качестве второго источника опорного тока 13 используется коллектор входного p-n-p 1 транзистора.

В соответствии с п.4 формулы изобретения (фиг.4) в схему введены первый n-p-n 16 и второй p-n-p 17 дополнительные транзисторы, причем база первого n-p-n 16 дополнительного транзистора соединена с базой выходного n-p-n 5 транзистора, его эмиттер соединен с эмиттером выходного n-p-n 5 транзистора, а коллектор - связан со входом 10 первого токового зеркала 8 на p-n-p транзисторах, причем база второго дополнительного p-n-p транзистора 17 соединена с базой выходного p-n-p транзистора 6, его эмиттер соединен с эмиттером выходного p-n-p 6 транзистора, а коллектор - подключен к входу 12 второго токового зеркала 9 на p-n-p транзисторах.

В выходном каскаде фиг.5 в качестве первого источника опорного тока 11 используется коллектор входного n-p-n 2 транзистора, а в качестве второго источника опорного тока 13 применяется коллектор входного p-n-p 1 транзистора.

В заявляемом устройстве фиг.4 - 5 отношение площадей эмиттерного перехода выходного n-p-n 5 (S3) и дополнительного n-p-n 16 (S4), а также выходного p-n-p 6 (S3) и дополнительного p-n-p 17 (S4) транзисторов удовлетворяют условию N2>N1 (N2=S3/S4).

В соответствии с п.7 формулы изобретения (фиг.4 и 5) отношение площадей N1 эмиттерных переходов выходного 14 (S1) и входного 15 (S2) транзисторов первого 8 и второго 9 токовых зеркал (N1=S1/S2) и отношение площадей N2 эмиттерных переходов выходных p-n-p 5 и n-p-n 6 (S3) транзисторов к площадям эмиттерных переходов дополнительных p-n-p 17 (S4) и n-p-n 16 транзисторов (N2=S3/S4) удовлетворяет условию N1<N2.

В выходном каскаде фиг.6 введены первый n-p-n 18 и второй p-n-p 19 вспомогательные транзисторы, причем база первого n-p-n 18 вспомогательного транзистора соединена с нагрузкой 7, его эмиттер соединен с общей шиной источников питания через первый дополнительный резистор 20, коллектор соединен с входом 10 первого токового зеркала 8 на p-n-p транзисторах, база второго вспомогательного p-n-p транзистора 19 соединена с нагрузкой 7, коллектор связан с входом 12 второго токового зеркала на n-p-n транзисторах, а его эмиттер соединен с общей шиной источников питания через второй дополнительный резистор 21.

Каждый из источников опорного тока 11 и 13 в выходном каскаде фиг.11 выполнен на дополнительном транзисторе 22, коллектор которого является выходом 10 (12) источника опорного тока 11 (13), база соединена с источником напряжения смещения, а эмиттер через первый 23 и второй 24 двухполюсники подключен к шинам источника питания.

В выходном каскаде фиг.12 предусмотрена температурная зависимость выходных координат источников тока 11 и 13, что позволяет уменьшать ток ограничения Iогр с увеличением температуры микросхемы. При этом каждый из источников опорного тока 11 и 13 выполнен на дополнительном транзисторе 22, коллектор которого является выходом 10 (12) источника опорного тока 11 (13), база соединена с источником напряжения смещения, а эмиттер связан с первым токостабилизирующим двухполюсником 23 и коллектором транзистора датчика температуры 25, эмиттер транзистора датчика температуры 25 соединен с базой дополнительного транзистора 22 и источником напряжения смещения, база - с цепью установления статического режима на основе резистора 26 и дополнительного источника опорного тока 27.

Компьютерное моделирование в среде PSpice выходного каскада, соответствующего фиг.5, проводилось при статических токах и параметрах элементов, указанных на фиг.7. При этом отношение площадей эмиттерных переходов транзисторов VT5 и VT4 (VT7 и VT8) соответствовало N1=6, а токи выбирались на уровне I3=I4=I0=0,1÷1 мА.

График зависимости тока нагрузки ВК Iн от входного напряжения Uвх при разных значениях токов источников опорного тока I0=I2=I4=Var также показан на фиг.8.

Компьютерное моделирование в среде PSpice проходной характеристики выходного каскада, соответствующего фиг.4, проводилось при статических токах и параметрах элементов, указанных на фиг.8 при I2=I4=0. При этом отношение площадей эмиттерных переходов транзисторов Q6 и Q8 (Q3 и Q4) N2=S3/S4=10, а отношение N1 изменялось в пределах

График зависимости тока нагрузки ВК Iн от входного напряжения Uвх при разных значениях N1 показан на фиг.9. Из этого графика следует, что за счет изменения отношения площадей эмиттерных переходов транзисторов токовых зеркал 8 и 9 (N1=S1/S2) можно изменять в широких пределах ток ограничения Iогр (6÷80 мА).

Амплитудно-частотная характеристика коэффициента усиления по напряжению Ку≈1 входного каскада фиг.3 при параметрах статического режима, указанных в схеме фиг.7, приведена на фиг.10. Из нее следует, что верхняя граничная частота заявляемого устройства (по уровню -3 дБ) на транзисторах ФГУ НПП «Пульсар» превышает 7 ГГц.

Рассмотрим работу заявляемого ВК на примере анализа входного каскада фиг.2.

В статическом режиме выходные транзисторы 14 токовых зеркал 8 и 9 находятся в насыщении - их напряжение коллектор-эмиттер близко к нулю (Uкэ.min=50÷100 мВ). Такое состояние транзисторов обеспечивается соответствующим выбором токов источников токов 11 и 13:

где S1, S2 - площади эмиттерных p-n переходов транзисторов 14 и 15;

Iэ5, Iэ6 - статический ток эмиттеров транзисторов 5 и 6,

I3=I4 - токи источников тока 3 и 4.

Таким образом, при нулевом сигнале на входе ВК коллекторы его транзисторов 5 и 6 соединены через небольшие сопротивления насыщенных транзисторов 14 токовых зеркал 8, 9 (единицы - десятки Ом) с шинами питания. Следовательно, при увеличении uвх положительной полярности ток нагрузки 7 (Iн) и ток эмиттера транзистора 5 увеличиваются как обычно:

На фиг.7 это соответствует начальному участку проходной характеристики iн=f(uвх).

Как только величина тока эмиттера транзистора 14 достигнет значения

этот транзистор выходит из насыщения и «отсоединяет» коллектор транзистора 5 от шины положительного источника питания. Поэтому транзистор 5 теряет свои усилительные свойства (превращается в одиночный прямосмещенный p-n переход), а ток нагрузки 7 ограничивается на заданном уровне Iогр, зависящем от параметров I11, S1, S2.

При отрицательном uвх выходной каскад работает аналогично, однако параметры ограничения тока нагрузки в этом случае определяются величинами I13, S1, S2.

Необходимо обратить внимание на следующие достоинства предлагаемой схемы выходного каскада.

1. Насыщенное состояние выходных транзисторов 14 токовых зеркал 8 и 9 не создает проблем с установлением статического режима выходных транзисторов 5 и 6 в широком температурном диапазоне.

2. Величина тока ограничения Iогр может изменяться путем изменения отношения площадей N1<N2 и установки заданных значений токов I11=I13. Эти токи в зависимости от поставленной задачи могут изменяться, например, пропорционально выходному напряжению ВК (фиг.6). Это позволяет более эффективно использовать выходные транзисторы 5 и 6 - иметь более высокие величины Iогр при более высоких значениях Uн (т.е. при меньших мощностях, выделяемых на коллекторном переходе транзистора 5).

В частных случаях возможны другие виды электронной регулировки порога ограничения тока нагрузки Iогр:

- в зависимости от сопротивления нагрузки 7 (Rн);

- в зависимости от напряжения источников питания;

- в зависимости от температуры кристалла микросхемы;

- в зависимости от задержек между временем включения положительного и отрицательного источников питания и т.д.

3. Новые элементы (токовые зеркала) 8 и 9 практически не ухудшают частотные характеристики входного каскада (см. фиг.10). Паразитные емкости транзисторов 14-15 (емкости коллектор-база, емкости на подложку) оказываются включенными в коллекторную цепь транзисторов 5 и 6 и не влияют на работу каскада. Как следствие, верхняя граничная частота f1 по уровню -3 дБ заявляемого ВК близка к 8 ГГц (при использовании транзисторов ФГУП НПП «Пульсар»). Это лучшие значения f1 на отечественных интегральных транзисторах.

4. Ограничение тока нагрузки в заявляемом ВК обеспечивается без ухудшения диапазона изменений напряжений на нагрузке. Это особенно важно для схем с низковольтным питанием (1,5-3 В). Действительно, в рабочем режиме, когда транзисторы 14 насыщены, диапазон изменения uн в заявляемой схеме такой же, как и в каскаде-прототипе, и во многом определяется остаточным напряжением на источниках тока 3 и 4.

5. Ограничение токов нагрузки заявляемого ВК осуществляется без введения в эмиттер или коллектор транзисторов 5 и 6 измерительных резисторов, которые необходимы в традиционных схемах защиты по току.

В схемах выходного каскада фиг.3 и фиг.5 введение новых связей обеспечивает снижение общего тока потребления за счет исключения двух токопотребляющих ветвей I11, I13. В этих схемах ток ограничения Iогр устанавливается токами источников 3 и 4, которые одновременно определяют и статический режим транзисторов 1 и 2.

В схеме фиг.6 порог ограничения тока нагрузки зависит от выходного напряжения ВК. Это объясняется тем, что общий входной ток токовых зеркал 8, 9 имеет две составляющие

Поэтому порог ограничения

а мощность, выделяемая на коллекторе транзистора 5

Введение транзисторов 18, 19 позволяет использовать энергетические возможности транзисторов 5 и 6 более эффективно.

Применение в качестве источников тока 11 и 13 подсхем фиг.11 позволяет изменять ток ограничения Iогр в зависимости от напряжения питания (Е1, Е2)

Чем больше Е1, тем меньше Iогр, что обеспечивает более эффективное использование энергетических возможностей транзисторов 5 и 6.

Если в качестве источников тока 11 и 13 применяется подсхема фиг.12, то ток ограничения Iогр будет уменьшаться при повышении температуры микросхемы, т.е. подсхемы фиг.12 будут выполнять роль тепловой защиты.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983.

2. Патент Японии JP 2003258529.

3. Патент Японии JP 2000183666.

4. Патент Японии JP 2000165156.

5. Патент Японии JP 10065457.

6. Патент Японии JP 11167368.

7. Патент Японии JP 10163763.

8. Патент Японии JP 8237044.

9. Патент Японии JP 2004260395.

10. Патент Японии JP 10270954.

11. Патент Японии JP 6204759.

12. Патент Японии JP 11251846.

13. Патент Японии JP 10022747.

14. Патент США №4477780.

15. Патент США №6160451.

16. Патент США №4412184.

17. Патент США №5170134.

18. Патент США №5907262.

19. Патент США №5049653.

20. Патент США №6420933.

21. Патент США №6166603.

22. Патент США №6262633.

23. Патент США №5510754.

24. Патент США №5512859.

25. Патент США №5357211.

26. Патент США №6181204.

27. Патент США №6278356.

28. Патент США №6542032.

29. Патент США №5352969.

30. Патент США №5399991.

31. Патент США №4160216.

32. Патент США №5623230.

33. Патент США №5568090.

34. Патент США №6459338.

35. Патент США №6466062.

36. Патент США №6552612.

37. Патент США №5003269.

38. Патент США №5786731.

39. Патент США №5455533.

40. Патент США №5955908.

41. Патент США №6535063.

42. Патент США №5351012.

43. Патент США №4893091.

44. Патент ЕР 1418668.

45. Патент ЕР 0786858 В1.

46. WO 03/043185 А1.

47. Patent А.Р. US 2002/0121934 А1.

48. А.св. СССР 1042156.

49. Патент RU 2168263.

50. А.св. СССР 1506512.

1. Выходной каскад операционного усилителя, содержащий входные p-n-p (1) и n-p-n (2) транзисторы, базы которых связаны друг с другом, эмиттеры соединены с первым (3) и вторым (4) источниками тока и базами выходных n-p-n (5) и p-n-p (6) транзисторов, причем эмиттеры выходных n-p-n (5) и p-n-p (6) транзисторов связаны с нагрузкой (7), отличающийся тем, что в схему введены первое (8) на p-n-p транзисторах и второе (9) на n-p-n транзисторах токовые зеркала, коллектор выходного n-p-n транзистора (5) соединен с коллекторным выходом первого токового зеркала (8), коллектор выходного p-n-p (6) транзистора соединен с коллекторным выходом второго токового зеркала (9), причем вышеуказанные выходные транзисторы (5) и (6) соединены через соответствующие первое (8) и второе (9) токовые зеркала с шинами питания, вход (10) первого токового зеркала (8) на p-n-p транзисторах соединен с выходом первого источника опорного тока (11), а вход (12) второго токового зеркала (9) на n-p-n транзисторах соединен с выходом второго источника опорного тока (13).

2. Устройство по п.1, отличающееся тем, что каждое из токовых зеркал (8) и (9) содержит выходной (14) и входной (15) транзисторы с объединенными эмиттерами, а также объединенными базами, коллектор входного (15) транзистора соединен с базой выходного (14) транзистора, причем коэффициенты передачи по току каждого из токовых зеркал (8) и (9) N1, зависящие от отношения площадей эмиттерных переходов выходного (14) (S1) и входного (15) (S2) транзисторов токовых зеркал, выбираются больше единицы.

3. Устройство по п.1, отличающееся тем, что в качестве первого источника опорного тока (11) используется коллектор входного n-p-n (2) транзистора, а в качестве второго источника опорного тока (13) используется коллектор входного p-n-p (1) транзистора.

4. Устройство по п.1, отличающееся тем, что в схему введены первый n-p-n (16) и второй p-n-p (17) дополнительные транзисторы, причем база первого n-p-n (16) дополнительного транзистора соединена с базой выходного n-p-n (5) транзистора, его эмиттер соединен с эмиттером выходного n-p-n (5) транзистора, а коллектор связан со входом (10) первого токового зеркала (8) на p-n-p транзисторах, причем база второго дополнительного p-n-p транзистора (17) соединена с базой выходного p-n-p транзистора (6), его эмиттер соединен с эмиттером выходного p-n-p (6) транзистора, а коллектор - подключен ко входу (12) второго токового зеркала (9) на p-n-p транзисторах.

5. Устройство по п.4, отличающееся тем, что в качестве первого источника опорного тока (11) используется коллектор входного n-p-n (2) транзистора, а в качестве второго источника опорного тока (13) используется коллектор входного p-n-p (1) транзистора.

6. Устройство по любому пп.4 и 5, отличающееся тем, что отношение площадей эмиттерного перехода выходного n-p-n (5) (S3) и дополнительного n-p-n (16) (S4), а также выходного p-n-p (6) (S3) и дополнительного p-n-p (17) (S4) транзисторов удовлетворяют условию N2=S3/S4>1.

7. Устройство по п.6, отличающееся тем, что отношение площадей N1 эмиттерных переходов входного (14) (S1) и выходного (15) (S2) транзисторов первого (8) и второго (9) токовых зеркал (N1=S1/S2) и отношение площадей N2 эмиттерных переходов выходных p-n-p (5) и n-p-n (6) (S3) транзисторов к площадям эмиттерных переходов дополнительных p-n-p (17) и n-p-n (16) транзисторов (S4) (N2=S3/S4) удовлетворяет условию N1<N2.

8. Устройство по п.3, отличающееся тем, что в схему введены первый n-p-n (18) и второй p-n-p (19) вспомогательные транзисторы, причем база первого n-p-n (18) вспомогательного транзистора соединена с нагрузкой (7), его эмиттер соединен с общей шиной источников питания через первый дополнительный резистор (20), коллектор соединен со входом (10) первого токового зеркала (8) на p-n-p транзисторах, база второго вспомогательного p-n-p транзистора (19) соединена с нагрузкой (7), коллектор связан со входом (12) второго токового зеркала на n-p-n транзисторах, а его эмиттер соединен с общей шиной источников питания через второй дополнительный резистор (21).

9. Устройство по п.1, отличающееся тем, что каждый из источников опорного тока (11) и (13) выполнен на дополнительном транзисторе (22), коллектор которого является выходом (10) (12) источника опорного тока (11) (13), база соединена с источником напряжения смещения, а эмиттер через первый (23) и второй (24) двухполюсники подключен к шинам источника питания.

10. Устройство по п.1, отличающееся тем, что каждый из источников опорного тока (11) и (13) выполнен на дополнительном транзисторе (22), коллектор которого является выходом (10) (12) источника опорного тока (11) (13), база соединена с источником напряжения смещения, а эмиттер связан с первым токостабилизирующим двухполюсником (23) и коллектором транзистора датчика температуры (25), эмиттер транзистора датчика температуры (25) соединен с базой дополнительного транзистора (22) и источником напряжения смещения, база - с цепью установления статического режима на основе резистора (26) и дополнительного источника опорного тока (27).