Составной быстродействующий аналого-цифровой преобразователь

Иллюстрации

Показать всеИзобретение относится к области цифровой техники и может быть использовано в устройствах преобразования аналогового напряжения в цифровой код. Техническим результатом является упрощение устройства и повышение точности аналого-цифрового преобразования. Устройство содержит m-разрядный параллельный аналого-цифровой преобразователь грубой шкалы, n-разрядный параллельный аналого-цифровой преобразователь усилитель разности, три схемы выборки-хранения, три регистра памяти, цифроаналоговый преобразователь, блок определения знака и инвертирования отрицательных напряжений, блок синхронизации. 4 ил.

Реферат

Область техники, к которой относится изобретение

Изобретение относится к области цифровой техники, в частности к составным быстродействующим аналого-цифровым преобразователям, и может быть использовано в устройствах преобразования аналогового напряжения в цифровой код.

Уровень техники

Известно устройство быстродействующего аналого-цифрового преобразователя (АЦП), содержащее три амплитудных анализатора, две группы дифференциальных переключателей на транзисторах и источниками опорного тока по числу квантов грубого отсчета, условно принятого равным четырем, хотя это число может быть любым другим, и два суммирующих резистора. На базы правых по схеме транзисторов поданы опорные напряжения U1, U1+ΔU, U2, U2+ΔU. На базы левых по схеме транзисторов и первые входы всех трех амплитудных анализаторов подан входной аналоговый сигнал, вторые входы второго и третьего амплитудных анализаторов соединены с соответствующими суммирующими резисторами. Выходы амплитудных анализаторов образуют выход устройства. (Авторское свидетельство СССР №750722 от 24.04.78 г.).

Недостатком указанного устройства является то, что на его основе практически невозможно реализовать точный (многоразрядный) и одновременно быстродействующий АЦП.

Известны конвейерные (pipeline) АЦП, содержащие несколько последовательно соединенных каскадов, причем последний каскад нагружен на точный АЦП. Каждый каскад содержит АЦП, кодовый выход которого подается на логическую схему коррекции, представляющую собой полный сумматор, и на цифроаналоговый преобразователь (ЦАП) повышенной точности с разрядностью, равной разрядности АЦП в целом, преобразующий этот код в аналоговый сигнал, который вычитается из входного аналогового сигнала, а остаток поступает на усилитель с фиксированным усилением, выход которого соединен со входом следующего каскада (Авербух В. Принципы построения быстрых АЦП, журнал Компоненты и технологии, 2000, №1, Online версия www.compitech.ru/html.cgi/arhiv/00_01/stat_34.htm).

Подобная структура используется компанией Burr-Brown во всех сериях высокоскоростных АЦП: 12-разрядных ADS80X, 10-разрядных ADS82X и ADS90X, 8-разрядных ADS83X и ADS93X (1999 CD-ROM Catalog, Burr-Brown Corporation).

Недостатком этого типа АЦП является сложность, обусловленная повышенными требованиями к используемым в схеме устройства ЦАП и АЦП, так как в каскадах устройства обрабатывается двухполярный сигнал.

Наиболее близким по технической сущности и достигаемому положительному эффекту и принятый авторами за прототип является составной быстродействующий АЦП, содержащий m-разрядный параллельный АЦП грубой шкалы, два источника постоянного напряжения, арифметико-логический блок, два блока оцифровки точной шкалы; каждый из блоков содержит усилитель разности, компаратор зашкаливания, n-разрядный параллельный АЦП и группу из k идентичных переключателей тока (где значение k определяется соотношением k=2m-l-1), каждый из которых состоит из дифференциального каскада на транзисторах и генератора тока (Патент РФ №2110887 от 29.05.96 г.).

Недостатком этого АЦП является сложность конструкции, а также низкая точность аналого-цифрового преобразования быстропротекающих процессов, сопровождающаяся занижением быстродействия относительно уровня, потенциально возможного для параллельных структур.

Заниженное быстродействие и низкая точность аналого-цифрового преобразования быстропротекающих процессов обусловлены возможным изменением уровня напряжения входного сигнала в ходе преобразования быстропротекающих процессов, а также динамическим режимом работы блоков оцифровки точной шкалы при отсутствии каких-либо синхронизирующих устройств и устройств выборки и хранения уровня напряжения входного сигнала, что неизбежно приводит к непрерывной смене кодов на выходе компаратора зашкаливания, а значит к вынужденному увеличению времени формирования кода на выходе арифметико-логического блока и в целом к ошибкам преобразования.

Раскрытие изобретения

Технический результат, который может быть достигнут с помощью предлагаемого изобретения, сводится к упрощению схемы устройства и повышению точности аналого-цифрового преобразования быстропротекающих процессов при одновременном приведении быстродействия к уровню потенциально возможному для параллельных структур.

Технический результат достигается тем, что в составной быстродействующий аналого-цифровой преобразователь, содержащий m-разрядный параллельный аналого-цифровой преобразователь грубой шкалы, n-разрядный параллельный аналого-цифровой преобразователь, усилитель разности, введены три схемы выборки-хранения, три регистра памяти, цифроаналоговый преобразователь, блок определения знака и инвертирования отрицательных напряжений, блок синхронизации, вход управления, причем информационный вход преобразователя соединен с первым входом первой схемы выборки-хранения; вход управления преобразователя соединен с входом блока синхронизации и со вторым входом первой схемы выборки-хранения, выход которой соединен со входом блока определения знака и инвертирования отрицательных напряжений, второй выход которого подключен ко входу первого регистра памяти, а первый выход параллельно подключен к входам второй и третьей схем выборки-хранения, входы управления которых соединены с первым выходом блока синхронизации; выход второй схемы выборки-хранения подключен к неинвертирующему входу усилителя разности, а выход третьей схемы выборки-хранения через параллельный аналого-цифровой преобразователь грубой шкалы, второй регистр памяти и цифроаналоговый преобразователь подключен к инвертирующему входу усилителя разности, выход которого через параллельный аналого-цифровой преобразователь подключен к третьему регистру памяти; входы управления записью регистров памяти являются соответственно вторым, третьим и четвертым выходами блока синхронизации, пятый выход которого подключен к входам управления сбросом регистров памяти; выходы первого, второго и третьего регистров памяти являются соответственно выходами знакового, старших и младших разрядов преобразователя.

Блок определения знака и инвертирования отрицательных напряжений содержит два аналоговых ключа, инвертирующий усилитель постоянного тока, компаратор, инвертор; вход блока определения знака и инвертирования отрицательных напряжений соединен с входами второго аналогового ключа, инвертирующего усилителя постоянного тока и неинвертирующим входом компаратора, инвертирующий вход компаратора соединен с нулевой шиной, выход компаратора подключен к входу инвертора, входу управления второго аналогового ключа и второму выходу блока определения знака и инвертирования отрицательных напряжений; выход инвертирующего усилителя постоянного тока соединен со входом первого аналогового ключа, выход которого, вместе с выходом второго аналогового ключа образуют первый выход блока определения знака и инвертирования отрицательных напряжений.

Блок синхронизации содержит две дифференцирующие цепи, четыре элемента задержки. Вход блока синхронизации подключен ко входам первого элемента задержки и второй дифференцирующей цепи; выход последней через четвертый элемент задержки подключен к пятому выходу блока синхронизации; выход первого элемента задержки подключен к первому выходу блока синхронизации и через последовательно соединенные первую дифференцирующую цепь, второй элемент задержки и третий элемент задержки подключен к четвертому выходу блока синхронизации; выход первой дифференцирующей цепи служит вторым выходом блока синхронизации, а выход второго элемента задержки служит третьим выходом блока синхронизации.

Краткое описание чертежей

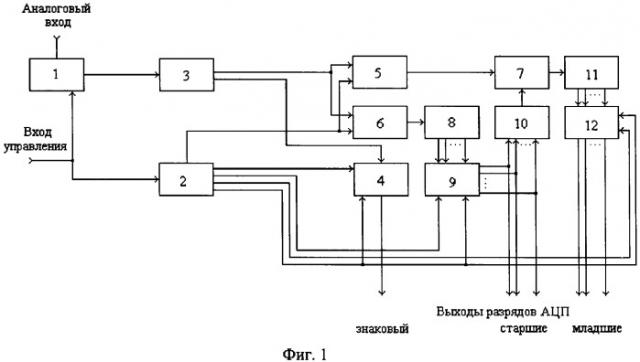

На фиг.1 приведена структурная схема составного быстродействующего аналого-цифрового преобразователя.

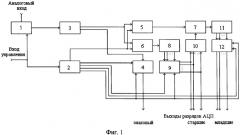

На фиг.2 приведена структурная схема блока определения знака и инвертирования отрицательных напряжений.

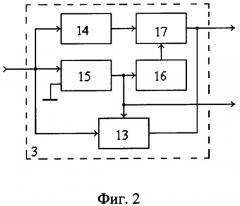

На фиг.3 приведена структурная схема блока синхронизации.

На фиг.4 приведены временные диаграммы, поясняющие работу устройства.

Осуществление изобретения

Составной быстродействующий аналого-цифровой преобразователь состоит из первой схемы выборки-хранения (СВХ) 1, первый вход которой соединен с информационным (аналоговым) входом преобразователя; вход управления преобразователя соединен с входом блока синхронизации (БС) 2 и со вторым входом первой СВХ 1, выход которой соединен со входом блока определения знака и инвертирования отрицательных напряжений (БОЗ и ИОН) 3, второй выход БОЗ и ИОН 3 подключен ко входу первого регистра памяти (РП) 4, а первый выход параллельно подключен ко входам второй и третьей СВХ 5 и 6, входы управления которых соединены с первым выходом БС 2; выход второй СВХ 5 подключен к неинвертирующему входу усилителя разности (УР) 7 с коэффициентом усиления К=2n, а выход третьей СВХ 6 через параллельный m-разрядный аналого-цифровой преобразователь (АЦП) грубой шкалы 8, второй РП 9 и m-разрядный цифроаналоговый преобразователь (ЦАП) 10 подключен к инвертирующему входу УР 7, выход которого через параллельный n-разрядный АЦП 11 подключен к третьему РП 12; входы управления записью РП 4, 9 и 12 соответственно на n-, один и m-разрядов, являются вторым, третьим и четвертым выходами БС 2, пятый выход которого подключен к входам управления сбросом РП 4, 9 и 12; выходы первого, второго и третьего РП 4, 9 и 12 являются соответственно выходами знакового, старших и младших разрядов преобразователя.

Структурная схема блока определения знака и инвертирования отрицательных напряжений 3 приведена на фиг.2.

Вход БОЗ и ИОН 3 соединен с входами второго аналогового ключа (АК) 13, инвертирующего усилителя постоянного тока (ИУПТ) 14 и неинвертирующим входом компаратора (Ком) 15, инвертирующий вход компаратора соединен с нулевой шиной, выход компаратора подключен к входу инвертора (Инв) 16, входу управления второго аналогового ключа АК 13 и второму выходу БОЗ и ИОН 3; выход ИУПТ 14 соединен со входом первого аналогового ключа АК 17, выход которого вместе с выходом второго АК 13 образуют первый выход БОЗ И ИОН 3.

Структурная схема блока синхронизации 2 приведена на фиг.3.

Вход БС 2 подключен ко входам первого элемент задержки (ЭЗ) 18 и второй дифференцирующей цепи (ДЦ) 19; выход последней через четвертый ЭЗ 20 подключен к пятому выходу БС 2; выход первого ЭЗ 18 подключен к первому выходу блока синхронизации и через последовательно соединенные первую ДЦ 21, второй ЭЗ 22 и третий ЭЗ 23 подключен к четвертому выходу БС 2; выход первой ДЦ 21 служит вторым выходом БС 2, а выход второго ЭЗ 22 служит третьим выходом БС 2.

Работа устройства поясняется временными диаграммами, приведенными на фиг.4.

Блок определения знака и инвертирования отрицательных напряжений 3 призван определить знак (полярность) уровня напряжения входного сигнала и ретранслировать сигнал далее с единичным коэффициентом передачи, а в случае отрицательной полярности подвергнуть транслируемый сигнал инверсии.

Блок определения знака и инвертирования отрицательных напряжений 3 работает следующим образом.

Ком 15, в зависимости от полярности входного сигнала, формирует положительный или отрицательный порог, играющий роль знакового разряда (логической единицы или нуля, поступающих на второй выход БОЗ и ИОН 3 и записываемых впоследствии в первый РП 4), а также управляющего воздействия, поступающего на АК 17 через Инв 16 и АК 13 непосредственно, то есть состояния АК 17 и АК 13 взаимообратны.

В случае поступления на вход БОЗ и ИОН 3 сигнала положительной полярности:

- Ком 15 формирует положительный потенциал; на второй выход БОЗ и ИОН 3 поступает логическая единица; АК 13 переводится в открытое состояние, АК 17 - закрытое;

- входной сигнал поступает на первый выход БОЗ и ИОН 3.

В случае поступления на вход БОЗ и ИОН 3 сигнала отрицательной полярности:

- Ком 15 формирует отрицательный потенциал;

- на второй выход БОЗ и ИОН 3 поступает логический ноль;

- АК 13 переводится в закрытое состояние, АК 17 - открытое;

- входной сигнал, инвертированный ИУПТ 14, поступает на первый выход БОЗ и ИОН 3.

Таким образом, БОЗ и ИОН 3 фактически формирует знак и модуль транслируемого сигнала.

Блок синхронизации 2 синхронизирует работу блоков устройства, переводя их на интервалах работы фактически в статический режим по входному сигналу, тем самым максимально повышая помехоустойчивость, точность и достоверность аналого-цифрового преобразования в целом при максимально сниженных временных задержках, создаваемых в процессе функционирования блоков устройства. Кроме того, БС 2 позволяет ввести в работу блоков устройства процесс цикличности, что в целом способствует достижению одной из целей заявки - приведению быстродействия устройства к уровню потенциально возможном для параллельных структур.

Блок синхронизации 2 работает следующим образом.

Сигнал (импульс) по входу управления длительностью t1÷t2, фиг.4,а:

- путем дифференцирования, осуществляемого ДЦ 19, преобразуется в короткий импульс - момент t1 (фиг.4,б) и задерживается ЭЗ 20 до момента t2 (фиг.4,в), ЭЗ 20 формирует сигнал сброса регистров памяти 4, 9, 12, поступающий на пятый выход БС 2;

- задерживается ЭЗ 18 до моментов t4÷t5 (фиг.4,г), ЭЗ 18 формирует управляющий сигнал для СВХ 5, 6, поступающий на первый выход БС 2.

Выходной сигнал ЭЗ 18 путем дифференцирования, осуществляемого ДЦ 21, преобразуется в короткий импульс - момент t4 (фиг.4,д), ДЦ 21 формирует сигнал управления записью РП 4, поступающий на второй выход БС2.

Выходной сигнал ДЦ 21 задерживается ЭЗ 22 до момента t6 (фиг.4,е), ЭЗ 22 формирует сигнал управления записью РП 9, поступающий на третий выход БС 2.

Выходной сигнал ЭЗ 22 задерживается ЭЗ 23 до момента t7 (фиг.4,ж), ЭЗ 23 формирует сигнал управления записью РП 12, поступающий на четвертый выход БС 2.

Составной быстродействующий аналого-цифровой преобразователь работает следующим образом.

Импульс, поступающий по входу управления устройства, в момент t1 (фиг.4,а) разрешает СВХ 1 произвести выборку и запоминание уровня напряжения входного сигнала. Одновременно с этим:

- БС 2 приступает к формированию импульса сброса и в момент времени t3 (фиг.4,в) осуществляет сброс РП 4, 9, 12 импульсом, поступающим с пятого выхода БС 2;

- БОЗ и ИОН 3 приступает к анализу уровня, запоминаемого СВХ 1.

К моменту времени tз (фиг.4,а) СВХ 1 завершает процесс запоминания. В общем случае интервал t1÷t2 (фиг.4,а) исчисляется единицами нс. (В АЦП AD9059 апертурное время составляет 2,7 нс. (http://www.gaw.ru/pdf7AD/adc/ ad9059.pdf), время выборки встроенной схемы выборки-хранения составляет 1 нс. (www.compitech.ru/html.cgi/arhiv/00_01/stat_34. htm)).

К моменту времени t4 (фиг.4,г) напряжение на первом выходе БОЗ и ИОН 3 стабилизируется, и по команде БС 2, поступающей с первого выхода БС 2 на входы управления СВХ 5 и 6, начинается процесс запоминания уровня напряжения в СВХ 5 и 6. В общем случае интервал t2÷t4 (фиг.4,г) исчисляется долями нс. Он определяется прежде всего задержкой, создаваемой ИУПТ 14 (причем именно временем дополнительного нарастания переходной характеристики ИУПТ 14 с момента t2 до момента t4), (например, сверхскоростной усилитель AD8009 характеризуется скоростью нарастания выходного сигнала 5500 В/мкс, THS3001 - 6500 В/мкс. (Г.Волович. Широкополосные интегральные усилители. http://www.PLATAN.ru/ shem/pdf/str27-1sx.pdf)), так как быстродействие современных компараторов сравнимо с быстродействием СВХ и к моменту времени t2 AK 17 и 13 уже находятся в заданном состоянии.

В момент времени t4 (фиг.4.д) БС 2 посредством импульса, поступающего со второго выхода БС 2 на вход управления записью РП 4, записывает в РП 4 информацию о полярности аналогового входного сигнала. Данная информация в виде логического нуля или логической единицы поступает со второго выхода БОЗ и ИОН 3 на вход РП 4.

К моменту времени t5 (фиг.4,г) СВХ 5 и 6 завершают процесс запоминания. В общем случае интервал t4÷t5 (фиг.4,г) может быть в полтора - два раза меньше интервала t1÷t2, так как на вход СВХ 5 и 6 поступают сигналы только одной полярности, а полярность входных сигналов СВХ 1 может чередоваться, что в наихудшем случае потребует полного перезаряда емкостного элемента СВХ 1 в отличие от дозаряда емкостных элементов СВХ 5 и 6.

По завершении установления напряжения на выходе СВХ 6 будет иметь место фактически статический режим работы АЦП по входному сигналу, в результате чего код на выходе параллельного АЦП 8 грубой шкалы стабилизируется и не будет наблюдаться дрожание кода младшего разряда, что позволит избежать случайных ошибок анализа.

Интервал t5÷t6 (фиг.4,е), соответствует времени анализа входного сигнала параллельным АЦП 8 грубой шкалы и является стандартизованным.

В момент времени t6 (фиг.4,е) БС 2 посредством импульса, поступающего с третьего выхода БС 2 на вход управления записью РП 9, записывает в РП 9 выходной код параллельного АЦП 8 грубой шкалы. Так как РП 9 типовой, задержка на воспроизведение кода на выходах РП 9 стандартизована.

Код, сформированный на выходе РП 9, преобразуется ЦАП 10 в напряжение, поступающее на инвертирующий вход УР 7. Так как разрядность параллельного АЦП 8 грубой шкалы - m, имеет место разбиение диапазона изменения входного напряжения, поступающего с СВХ 6, на 2m одинаковых зон напряжения, каждая из которых равна, например, величине Е. Ошибка квантования при этом не превысит значения величины Е. В свою очередь, напряжение на выходе УР 7 примет значение:

где n - разрядность параллельного АЦП 11.

Благодаря операции умножения, требования по чувствительности к АЦП 8 грубой шкалы и 11 одинаковые.

Так как предполагается, что параллельный АЦП 8 грубой шкалы работает с недовесом, напряжение на выходе ЦАП 10 будет всегда меньше напряжения, записанного в СВХ 6(5), а напряжение на выходе УР 7 будет положительной полярности. Последнее позволяет в качестве параллельного АЦП 11 использовать однополярный АЦП. Так как сигналы напряжений, поступающих на входы УР 7, фиксированы, будет иметь место фактически статический режим работы АЦП по входному сигналу, в результате чего код на выходе параллельного АЦП 11 стабилизируется и не будет наблюдаться дрожание кода младшего разряда, что позволит избежать случайных ошибок анализа, а также привести интервал t6÷t7 (фиг.4,ж) к минимальному значению, типовому для параллельных АЦП.

В момент времени t7 (фиг.4,ж) БС 2 посредством импульса, поступающего с четвертого выхода БС 2 на вход управления записью РП 12, записывает в РП 12 выходной код параллельного АЦП 11.

В случае некорректной работы параллельного АЦП 8 грубой шкалы или ЦАП10:

а) напряжение на выходе ЦАП 10 превышает напряжение на выходе СВХ 5

- напряжение на выходе УР 7 будет отрицательной полярности, что приведет к установлению на выходе параллельного АЦП 11, в силу его однополярности, кодов с нулевым весом (00...);

б) напряжение на выходе СВХ 5 превышает напряжение на выходе ЦАП 10 более чем на величину Е

- напряжение на выходе УР 7 превысит величину Е, что приведет к установлению на выходе параллельного АЦП 11 кодов с максимальным весом (11...1).

Как в том, так и в другом случае будет иметь место коррекция результата аналого-цифрового преобразования. В основе данного утверждения лежат следующие соображения:

1) существенной нелинейностью передаточной характеристики страдают, как правило, АЦП;

2) при исправном АЦП ошибка преобразования младшего разряда возникает в случае близких по уровню значений входного и опорного сигналов, причем ввиду высокой крутизны амплитудных характеристик компараторов АЦП, величина ошибки составляет доли процентов от шага квантования, в частности АЦП 8 грубой шкалы, тем самым можно утверждать, что она не превысит величину шага квантования АЦП 11;

3) в случае преобразования, выполненного АЦП 8 грубой шкалы с перевесом, добавление минимального кода от АЦП 11 принесет ошибку преобразования не более младшего разряда АЦП 11;

4) в случае преобразования, выполненного АЦП 8 грубой шкалы с недовесом, добавление максимального кода от АЦП 11 принесет ошибку преобразования не более младшего разряда АЦП 11.

Таким образом, в предлагаемом устройстве, в отличие от прототипа, нет необходимости использовать арифметико-логический блок, вносящий существенные временные задержки в процесс преобразования.

При работе предлагаемого устройства в циклическом режиме, ввиду периодичности работы блоков устройства, имеется возможность сокращения общего времени, отводимого на преобразование входного сигнала, так как выполняется соотношение временных интервалов (фиг.4,и):

то есть имеет место интервал сдвига tсдв.

В прототипе данной возможности нет.

Ввиду того, что в предлагаемом устройстве, в отличие от прототипа, удалось избежать методических погрешностей преобразования, влияющих на конечное время преобразования аналогового сигнала, то, несмотря даже на введение гарантированных временных защитных интервалов (задержек), можно однозначно утверждать, что предлагаемое устройство оценивается лучшими показателями в сравнении с прототипом по критерию быстродействия относительно потенциально возможного для параллельных структур.

Благодаря введению в состав устройства СВХ 1, 5, 6 и жесткой синхронизации режимов работы устройства, удалось избежать изменения уровня напряжения входного сигнала в ходе преобразования быстропротекающих процессов, а значит удалось достичь повышения точности аналого-цифрового преобразования быстропротекающих процессов.

Благодаря введению в состав устройства БОЗ И ИОН 3, входные сигналы параллельного АЦП 8 грубой шкалы всегда имеют положительную полярность с диапазоном входных напряжений, равным половине динамического диапазона входного сигнала. Это, в свою очередь, фактически равносильно увеличению разрядности параллельного АЦП 8 грубой шкалы на один разряд, что в случае использования 8-разрядного АЦП эквивалентно введению 127 компараторов. Другими словами, для обеспечения одинаковых требований к точности преобразования в прототипе и предлагаемом устройстве вместо m-разрядного параллельного АЦП грубой шкалы, используемого в прототипе, в предлагаемом устройстве требуется (m-1) -разрядный параллельный АЦП, в силу чего данный АЦП будет проще, а его схема будет иметь в 2 раза меньше компараторов.

Все вышесказанное будет справедливо и относительно параллельного АЦП 11. При этом следует учесть, что в прототипе используется два блока оцифровки точной шкалы, содержащих группу из k=2m-l-1 переключателей тока, усилитель разности, компаратор зашкаливания и n-разрядный параллельный АЦП. В силу этого можно утверждать, что для обеспечения одинаковых требований к точности преобразования в прототипе и предлагаемом устройстве функцию двух параллельных АЦП выполняет один, то есть имеет место упрощение схемы. Не следует забывать и о 2-k переключателях тока, используемых в прототипе и значительное число которых, даже без учета очень высоких требований к стабильности параметров, определяет высокую степень сложности прототипа.

Составной быстродействующий аналого-цифровой преобразователь, содержащий m-разрядный параллельный аналого-цифровой преобразователь грубой шкалы, n-разрядный параллельный аналого-цифровой преобразователь, усилитель разности, отличающийся тем, что в него введены три схемы выборки-хранения, три регистра памяти, цифроаналоговый преобразователь, блок определения знака и инвертирования отрицательных напряжений, блок синхронизации, вход управления, при этом информационный вход преобразователя соединен с первым входом первой схемы выборки-хранения; вход управления преобразователя соединен с входом блока синхронизации и со вторым входом первой схемы выборки-хранения, выход которой соединен с входом блока определения знака и инвертирования отрицательных напряжений, второй выход которого подключен к входу первого регистра памяти, а первый выход параллельно подключен к входам второй и третьей схемы выборки-хранения, входы управления которых соединены с первым выходом блока синхронизации; выход второй схемы выборки-хранения подключен к неинвертирующему входу усилителя разности, а выход третьей схемы выборки-хранения через параллельный аналого-цифровой преобразователь грубой шкалы, второй регистр памяти и цифроаналоговый преобразователь подключен к инвертирующему входу усилителя разности, выход которого через параллельный аналого-цифровой преобразователь подключен к третьему регистру памяти; входы управления записью регистров памяти являются соответственно вторым, третьим и четвертым выходами блока синхронизации, пятый выход которого подключен к входам управления сбросом регистров памяти; выходы первого, второго и третьего регистров памяти являются соответственно выходами знакового, старших и младших разрядов преобразователя, а блок определения знака и инвертирования отрицательных напряжений содержит два аналоговых ключа, инвертирующий усилитель постоянного тока, компаратор, инвертор, при этом вход блока определения знака и инвертирования отрицательных напряжений соединен с входами второго аналогового ключа, инвертирующего усилителя постоянного тока и неинвертирующим входом компаратора, инвертирующий вход компаратора соединен с нулевой шиной, выход компаратора подключен к входу инвертора, входу управления второго аналогового ключа и второму выходу блока определения знака и инвертирования отрицательных напряжений; выход инвертирующего усилителя постоянного тока соединен с входом первого аналогового ключа, выход которого вместе с выходом второго аналогового ключа образуют первый выход блока определения знака и инвертирования отрицательных напряжений; блок синхронизации содержит две дифференцирующие цепи, четыре элемента задержки, при этом вход блока синхронизации подключен к входам первого элемента задержки и второй дифференцирующей цепи, выход последней через четвертый элемент задержки подключен к пятому выходу блока синхронизации; выход первого элемента задержки подключен к первому выходу блока синхронизации и через последовательно соединенные первую дифференцирующую цепь, второй элемент задержки и третий элемент задержки подключен к четвертому выходу блока синхронизации; выход первой дифференцирующей цепи служит вторым выходом блока синхронизации, а выход второго элемента задержки служит третьим выходом блока синхронизации.