Устройство поиска широкополосных сигналов

Иллюстрации

Показать всеИзобретение относится к области радиотехники и может быть использовано при построении систем радиосвязи, радионавигации, управления, использующих широкополосные сигналы. Технический результат - повышение помехоустойчивости при одновременном воздействии структурных и идущих подряд импульсных помех. Для этого в известное устройство поиска широкополосных сигналов введены второй ключ, второй тактируемый RS-триггер, второй таймер и элемент «ИЛИ», в результате чего выход устройства отключается на время действия каждой импульсной помехи, что исключает ложную синхронизацию на структурную помеху и ошибку в поиске широкополосных сигналов. 4 ил.

Реферат

Изобретение относится к области радиотехники и может найти применение при построении систем радиосвязи, радионавигации, управления, использующих широкополосные сигналы.

Известны устройства поиска широкополосных сигналов (см. а.с. №1003372, Н04L 7/02, 1981 г.; №809619, Н04L 7/02, 1979 г.), которым присущ общий недостаток, заключающийся в низкой помехоустойчивости поиска широкополосных сигналов (ШПС) по задержке, а именно в большой вероятности синхронизации устройств поиска на структурные помехи.

Наиболее близким по технической сущности к предлагаемому является устройство, описанное в патенте №2268549, Н04В 1/10, Н04L 7/02, принятое за прототип.

На фиг.1 изображена блок-схема устройства-прототипа, где приведены следующие обозначения:

1 - ключ;

2 - линейная часть;

3 - согласованный фильтр;

3.1 - предварительный фильтр;

3.2 - линия задержки;

3.31 - 3.3n - первый,..., n-ый аттенюаторы;

3.41 - 3.4n - первый,..., n-ый фазовращатели;

3.5 и 3.6 - первый и второй сумматоры;

3.71 - 3.7n/2 - первый,..., n/2-й инверторы;

3.8 и 3.9 - первый и второй детекторы;

3.10. и 3.11 - первый и второй блоки сравнения с порогом;

3.12 - элемент «И»;

3.13 - элемент «НЕ»;

4 - третий блок сравнения с порогом;

5 - блок управления переключением каналов (БУПК);

6 - генератор тактовых импульсов;

7 - тактируемый RS-триггер;

8 - таймер;

9 - логический блок.

Устройство-прототип содержит последовательно соединенные ключ 1, линейную часть 2, согласованный фильтр 3, первый детектор 3.8, первый блок сравнения с порогом 3.10, элемент «И» 3.12 и логический блок 9, выход которого является выходом устройства, соединенным с управляющим входом блока управления переключением каналов 5, тактовый вход которого соединен с выходом генератора тактовых импульсов 6, а выход БУПК 5 соединен со вторым управляющим входом линейной части 2.

Первый вход ключа 1 является входом устройства, соединенным с входом третьего блока сравнения с порогом 4, выход которого соединен со вторым входом ключа 1, первым управляющим входом логического блока 9 и через последовательно соединенные тактируемый RS-триггер 7 и таймер 8 - со вторым управляющим входом электронного коммутатора 9. Кроме того, выход таймера 8 соединен со вторым входом тактируемого RS-триггера 7.

При этом согласованный фильтр 3 содержит последовательно соединенные предварительный фильтр 3.1, вход которого также является входом согласованного фильтра 3, и линию задержки 3.2, (n-1) выходов которой (где n - четное число) соединены соответственно с входами со второго по n-й аттенюаторов 3-32-3.3n, выходы которых соединены соответственно с входами со второго по n-й фазовращателей 3.42-3.4n, выходы которых соединены с второго по n-й входами первого сумматора 3.5 соответственно, а вход линии задержки 3.2 через последовательно соединенные первый аттенюатор 3.31 и первый фазовращатель 3.41 соединен с первым входом первого сумматора 3.5, выход которого является также и выходом согласованного фильтра 3.

Кроме того, выходы с первого по n/2-й фазовращателей 3.41 - 3.4n/2 через соответствующие с первого по n/2-й инверторы 3.71-3.7n/2 соединены с первой группой n/2 входов второго сумматора 3.6 соответственно, а выходы с (n/2+1)-го по n-й фазовращателей 3.4n/2+1-3.4n соединены соответственно со второй группой n/2 входов второго сумматора 3.6, выход которого через последовательно соединенные второй детектор 3.9, второй блок сравнения с порогом 3.11 и элемент «НЕ» 3.13 соединен со вторым входом элемента «И» 3.12.

Устройство-прототип работает следующим образом.

На вход устройства поступает входной сигнал, при отсутствии импульсной помехи он без изменения проходит через блок 1 и поступает на первый вход блока 2. С выхода блока 2 сигнал поступает на вход блока 3, где через блок 3.1 поступает на вход блока 3.2 и через последовательно соединенные блоки 3.31 и 3.41 - на первый вход блока 3.5. С (n-1) выходов блока 3.2 через соответствующие последовательно соединенные блоки 3.32-3.3n и 3.42-3.4n элементы сигнала поступают на соответствующие со второго по n-й входы блока 3.5. Параметры блока 3.2, блоков 3.31-3.3n и 3.41-3.4n выбираются таким образом, чтобы на выходе блока 3.5 элементы сигнала складывались в фазе и выражали значение функции автокорреляции полезного сигнала, тогда на выходе блока 3.6 получается значение огибающей функции автокорреляции (АКФ) полезного сигнала. Превышение порога в блоке 3.10 приводит к тому, что на второй вход блока 3.12 поступит логическая единица.

Одновременно с выходов блоков 3.41-3.4n/2 элементы сигнала через соответствующие блоки 3.71-3.7n/2 поступают на n/2 входов блока 3.6 соответственно. С выходов блоков 3.4n/2+1-3.4n элементы сигнала поступают на другие n/2 входов блока 3.6 соответственно.

Это приводит к тому, что в момент времени, когда на выходе блока 3.5 все n элементов сигнала сложатся синфазно, то на выходе блока 3.6 n/2 элементов сложатся синфазно, а n/2 остальных элементов сигнала сложатся с противоположной фазой, т.е. значение АКФ сигнала на выходе блока 3.6 будет близко к нулю. Соответственно, не будет превышен порог в блоке 3.11 и с выхода блока 3.13 на блок 3.12 поступит логическая единица. Следовательно, на выходе блока 3.12 сформируется логическая единица и, пройдя без изменения (если на входе нет импульсной помехи) через логический блок 9, поступит на управляющий вход блока 5, что приведет к фиксации данного канала, так как выход логической единицы с выхода блока 9 означает, что сигнал найден и поиск закончен.

Если на вход устройства поступит смесь полезного сигнала и структурной помехи, то, как и в случае только с полезным сигналом, превышение порога суммой огибающих функций автокорреляции сигнала и функции взаимной корреляции (ВКФ) помехи в блоке 3.10 приведет к поступлению на второй вход блока 3.12 логической единицы. Вероятность того, что в этот же момент значение функции ВКФ не превысит порог в блоке 3.11, достаточно мала. То есть с выхода блока 3.13 на первый вход блока 3.12 поступает логический нуль. Следовательно, на выходе блока 3.12 будет логический нуль и он, без изменения (при отсутствии на входе устройства импульсной помехи) пройдя через логический блок 9, поступит на управляющий вход блока 5. Логический нуль означает, что сигнал не найден, переключение каналов может быть продолжено, поиск полезного сигнала будет продолжен.

Если на вход устройства поступит структурная помеха, то вероятность того, что в момент отсчета будет превышен порог как в блоке 3.8, так и в блоке 3.9 достаточно велика. Это значит, что на первый вход блока 3.12 поступит логический нуль, а на второй вход блока 3.12 поступит логическая единица. С выхода блока 9 на управляющий вход блока 5 поступит логический нуль и поиск сигнала будет продолжен на других каналах.

Если на входе присутствует мощная импульсная помеха, то блок 4 закроет ключ 1 и блок 9 отключит выход (на выходе будет логический нуль), на управляющий вход блока 5 поступит логический нуль и поиск сигнала будет продолжен на других каналах. Но так как импульсная помеха уже прошла в тракт, то она вызовет ошибку в расчете корреляционной функции на время 2Т (где Т - длительность сигнала), в этом случае блок 8 подключит выход через блок 9 только по прошествии времени 2Т, а блок 7 обеспечит отсчет не сразу, а по срезу импульсной помехи.

Если на входе устройства, кроме полезного сигнала, присутствуют структурные и идущие подряд импульсные помехи, часть сигнала и часть структурной помехи по времени будут вырезаны. Это вызвано тем, что при воздействии следующей импульсной помехи функция АКФ сигнала и ВКФ полезного сигнала со структурной помехой будут искажены и на временном участке, превышающем интервал 2Т. Соотношение между АКФ полезного сигнала и ВКФ помехи в этом случае изменятся. Появляется вероятность, что устройство поиска выдаст решение, что обнаружен полезный сигнал, когда полезного сигнала на входе нет.

Блок 9 управляется с помощью двух сигналов, один из которых поступает с выхода блока 4 на первый управляющий вход, а другой - с выхода блока 8 на второй управляющий вход. По своей сути блок 9 - это сложный ключ, который в дальнейшем будем называть электронным коммутатором 9.

Кроме того, учитывая функциональное назначение совокупности блоков 3.1-3.13, целесообразно объединить их в один блок, который в дальнейшем будем называть блоком согласованной фильтрации и предварительной обработки сигнала 3.

Согласно вышеизложенному устройство-прототип в укрупненном виде представлено на фиг.2, где введены следующие обозначения:

1 - ключ;

2 - линейная часть;

3 - блок согласованной фильтрации и предварительной обработки сигнала;

4 - блок сравнения с порогом;

5 - блок управления переключением каналов (БУПК);

6 - генератор тактовых импульсов;

7 - тактируемый RS-триггер;

8 - таймер;

9 - электронный коммутатор (логический блок).

Укрупненный прототип содержит последовательно соединенные ключ 1, линейную часть 2, блок согласованной фильтрации и предварительной обработки сигнала 3 и электронный коммутатор 9, выход которого является выходом устройства, соединенным с управляющим входом блока управления переключением каналов (БУПК) 5, тактовый вход которого соединен с выходом генератора тактовых импульсов 6, а выход БУПК 5 соединен со вторым управляющим входом линейной части 2.

Первый вход ключа 1 является входом устройства, соединенным с входом блока сравнения с порогом 4, выход которого соединен со вторым входом ключа 1, первым управляющим входом электронного коммутатора 9 и через последовательно соединенные тактируемый RS-триггер 7 и таймер 8 - со вторым управляющим входом электронного коммутатора 9. Кроме того, выход таймера 8 соединен со вторым входом тактируемого RS-триггера 7.

Укрупненный прототип работает следующим образом.

На вход устройства поступает полезный сигнал, при отсутствии импульсной и структурной помех он без изменения проходит через блок 1 и поступает на первый вход блока 2. С выхода блока 2 сигнал поступает на вход блока 3, где происходит его согласованная фильтрация и предварительная обработка, в результате чего на выходе блока 3 будет уровень логической единицы, и так как импульсная помеха на входе отсутствует, то эта логическая единица без изменения пройдет через блок 9 и поступит на выход устройства, что свидетельствует об успешном окончании поиска, а также на управляющий вход блока 5, что приведет к фиксации данного канала.

Если на вход устройства поступает смесь полезного сигнала и структурной помехи или одна структурная помеха, то на выходе блока 3 будет сигнал уровня логического нуля, который без изменения пройдет через блок 9 и поступит на управляющий вход блока 5, что приведет к переключению каналов и продолжению поиска полезного сигнала.

Если на входе присутствует мощная импульсная помеха, то блок 4 закроет ключ 1 и блок 9 отключит выход (на выходе будет логический нуль), на управляющий вход блока 5 поступит логический нуль и поиск сигнала будет продолжен на других каналах; при этом блок 8 подключит выход через блок 9 только по прошествии времени 2Т относительно заднего фронта (среза) импульсной помехи.

Если на входе устройства, кроме полезного сигнала, присутствуют структурные и идущие подряд импульсные помехи, то при воздействии следующей импульсной помехи часть сигнала и часть структурной помехи (если она присутствует на входе) по времени будут вырезаны. Это приведет к тому, что АКФ полезного сигнала и ВКФ полезного сигнала со структурной помехой будут искажены и на временном участке, превышающем интервал 2Т. Соотношение между АКФ полезного сигнала и ВКФ помехи в этом случае изменится. Появляется вероятность, что устройство поиска выдаст решение, что обнаружен полезный сигнал, когда полезного сигнала на входе нет.

Таким образом, недостатком устройства-прототипа является низкая помехоустойчивость при одновременном воздействии структурных и идущих подряд импульсных помех.

Для устранения указанных недостатков в устройство поиска широкополосных сигналов, содержащее последовательно соединенные первый ключ, линейную часть, блок согласованной фильтрации и предварительной обработки сигнала и электронный коммутатор, выход которого является выходом устройства; последовательно соединенные генератор тактовых импульсов и блок управления переключением каналов, выход которого соединен со вторым, управляющим входом линейной части; последовательно соединенные блок сравнения с порогом, первый тактируемый RS-триггер и первый таймер, выход которого соединен со вторым входом первого тактируемого RS-триггера и вторым управляющим входом электронного коммутатора, выход которого соединен с управляющим входом блока управления переключением каналов, причем первый вход ключа является входом устройства, соединенным с входом блока сравнения с порогом, выход которого соединен со вторым входом ключа и первым управляющим входом электронного коммутатора, согласно изобретению введены последовательно соединенные второй ключ, второй тактируемый RS-триггер, второй таймер и элемент «ИЛИ», при этом выход блока сравнения с порогом соединен со вторым входом второго ключа, первый вход которого соединен с выходом первого тактируемого RS-триггера, выход первого таймера соединен со вторым входом элемента «ИЛИ», выход которого соединен со вторым входом второго тактируемого RS-триггера; в электронном коммутаторе дополнительно введен третий управляющий вход, соединенный с выходом второго таймера.

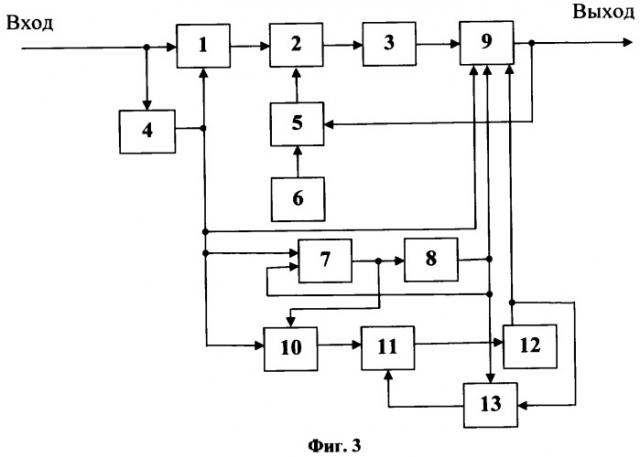

Функциональная схема предлагаемого устройства представлена на фиг.3, где введены следующие обозначения:

1 и 10 - первый и второй ключи;

2 - линейная часть;

3 - блок согласованной фильтрации и предварительной обработки сигнала;

4 - блок сравнения с порогом;

5 - блок управления переключением каналов (БУПК);

6 - генератор тактовых импульсов;

7 и 11 - первый и второй тактируемый RS-триггеры;

8 и 12 - первый и второй таймеры;

9 - электронный коммутатор;

13 - элемент «ИЛИ».

Предлагаемое устройство содержит последовательно соединенные первый ключ 1, линейную часть 2, блок согласованной фильтрации и предварительной обработки сигнала 3 и электронный коммутатор 9, выход которого соединен с управляющим входом блока управления переключением каналов (БУПК) 5, тактовый вход которого соединен с выходом генератора тактовых импульсов 6, а выход БУПК 5 соединен со вторым управляющим входом линейной части 2; последовательно соединенные второй ключ 10, второй тактируемый RS-триггер 11 и второй таймер 12, выход которого соединен с третьим управляющим входом электронного коммутатора 9 и первым входом элемента «ИЛИ» 13, выход которого соединен со вторым входом второго тактируемого RS-триггера 11; последовательно соединенные блок сравнения с порогом 4, первый тактируемый RS-триггер 7 и первый таймер 8, выход которого соединен со вторым управляющим входом электронного коммутатора 9, вторым входом элемента «ИЛИ» 13 и вторым входом первого тактируемого RS-триггера 7, выход которого соединен с первым входом второго ключа 10. Первый вход первого ключа 1 является входом устройства, соединенным с входом блока сравнения с порогом 4, выход которого соединен со вторыми входами первого 1 и второго 10 ключей, а также с первым управляющим входом электронного коммутатора 9, выход которого является выходом устройства.

Предлагаемое устройство работает следующим образом.

На вход устройства поступает полезный сигнал, при отсутствии импульсной и структурной помех он без изменения проходит через блок 1 и поступает на первый вход блока 2. С выхода блока 2 сигнал поступает на вход блока 3, где происходит его согласованная фильтрация и предварительная обработка. В результате чего, на выходе блока 3 будет уровень логической единицы, и так как импульсная помеха на входе отсутствует, то эта логическая единица без изменения пройдет через блок 9 и поступит на управляющий вход блока 5, что приведет к фиксации данного канала, так как выход логической единицы с выхода блока 9 означает, что сигнал найден и поиск закончен.

При отсутствии на входе устройства импульсных помех на выходе блока 4 будет логический нуль, который не сможет переключить блок 1 (отключить вход блока 2). Поступив на первый управляющий вход блока 9, логический нуль также не произведет никаких изменений в работе блока 9. Пройдя через блок 7, логический нуль не запустит таймер 8, на его выходе будет также логический нуль, который, поступив на второй управляющий вход блока 9, не произведет никаких изменений в работе блока 9. Логический нуль с выхода блока 7 разомкнет ключ 10 и на его выходе все время будет уровень логического нуля, который, пройдя без изменения через блок 11, оставит в покое второй таймер 12 и на его выходе будет логический нуль, который не произведет никаких изменений в работе блока 9, то есть электронный коммутатор 9 будет все это время замкнут, то есть будет пропускать сигнал на выход устройства.

Если на вход устройства поступает смесь полезного сигнала и структурной помехи при отсутствии на входе импульсных помех, то, пройдя без изменения через блок 1, сигнал поступает на первый вход блока 2. С выхода блока 2 сигнал поступает на вход блока 3, где происходит его согласованная фильтрация и предварительная обработка. В результате этого на выходе блока 3 будет сигнал уровня логического нуля. Так как импульсных помех на входе нет, то этот логический нуль без изменения пройдет через блок 9 и поступит на управляющий вход блока 5. Логический нуль означает, что сигнал не найден, переключение каналов может быть продолжено, поиск полезного сигнала будет продолжен. В этом случае на выходе блока 4 будет логический нуль, который не закроет ключ 1, то есть не отключит вход блока 2. Остальные блоки будут работать так же, как рассмотрено выше. В результате чего электронный коммутатор 9 откроется и будет все это время пропускать сигнал на выход устройства.

Если на вход устройства поступит одна лишь структурная помеха, то, пройдя без изменения через замкнутый ключ 1, она поступит на первый вход блока 2. С выхода блока 2 сигнал поступает на вход блока 3, где происходит его согласованная фильтрация и предварительная обработка. В результате на выходе блока 3 будет логический нуль. Так как импульсных помех на входе нет, то этот логический нуль без изменения пройдет через блок 9 и поступит на управляющий вход блока 5. Логический нуль означает, что сигнал не найден, переключение каналов может быть продолжено, поиск полезного сигнала будет продолжен на других каналах. Работа нижних блоков для этого случая ничем не отличается от предыдущих двух.

Если на входе присутствует единичная мощная импульсная помеха, то с выхода блока сравнения с порогом 4 сигнал логической единицы поступит на второй вход первого ключа 1, в результате чего он разомкнется, а также поступит на первый управляющий вход электронного коммутатора 9, в результате чего он не будет пропускать сигнал на выход устройства. На управляющий вход блока 5 поступит логический нуль и поиск сигнала будет продолжен на других каналах. Но так как импульсная помеха уже прошла в тракт, то она вызовет ошибку в расчете корреляционной функции на время 2Т. Поэтому таймер 8 подключит выход через электронный коммутатор 9 только по прошествии времени 2Т, а чтобы отсчет начался не сразу, а только по срезу импульсной помехи, то для этого служит первый триггер 7, на выходе которого будет логическая единица, которая и запустит первый таймер 8 на время 2Т. В продолжение этого времени на второй управляющий вход электронного коммутатора 9 будет поступать сигнал уровня логической единицы, в результате чего блок 9 не будет пропускать сигнал на выход устройства, и на его выходе будет логический нуль в продолжение времени 2Т, после этого первый таймер на своем выходе будет иметь логический нуль. В продолжение времени 2Т на управляющий вход ключа 10 будет поступать сигнал логической единицы, который откроет его, но так как ключ 10 откроется после прохождения первой импульсной помехи на входе, то на его выходе будет логический нуль при условии, если на входе устройства нет второй импульсной помехи. На второй таймер 12 поступает уровень логического нуля. На его выходе будет также сигнал логического нуля, который поступает на третий управляющий вход электронного коммутатора 9, в результате чего на выходе электронного коммутатора 9 в продолжение действия импульсной помехи и затем времени 2Т будет логический нуль, который, поступив на управляющий вход блока 5, приведет к продолжению поиска полезного сигнала на других каналах.

Если в продолжение времени 2Т на вход устройства поступит вторая мощная импульсная помеха, то сигнал с выхода блока сравнения с порогом 4 разомкнет первый ключ 1, при этом электронный коммутатор 9 не будет пропускать сигнал на выход устройства. Но так как импульсная помеха уже прошла в тракт, то она вызовет ошибку в расчете корреляционной функции еще на время 2Т. Поэтому сигнал логической единицы с выхода блока 4, пройдя через открытый второй ключ 10, попадет на второй тактируемый RS-триггер 11 и по срезу импульсной помехи запустит второй таймер 12 еще на время 2Т, в продолжение которого на третий управляющий вход электронного коммутатора 9 будет поступать сигнал уровня логической единицы, в результате чего он закроется и не будет пропускать сигнал на выход устройства. То есть на выходе устройства сигнал логического нуля будет находиться еще время 2Т, отсчитывая от среза второй импульсной помехи.

При наличии сигнала логической единицы на выходе первого таймера 8 первый тактируемый RS-триггер 7 перейдет в исходное состояние для возможности работы со следующими поступающими на вход импульсными помехами, а при наличии сигнала логической единицы на выходе либо первого 8, либо второго 12 таймеров второй тактируемый RS-триггер 11 перейдет в исходное состояние.

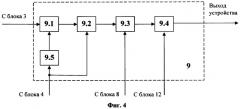

Функциональная схема электронного коммутатора 9 приведена на фиг.4, где введены следующие обозначения:

9.1,...,9.4 - первый, ..., четвертый ключи;

9.5 - блок задержки.

Электронный коммутатор 9 содержит блок задержки 9.5 и последовательно соединенные первый 9.1, второй 9.2, третий 9.3 и четвертый 9.4 ключи. При этом вход блока задержки 9.5, соединенный со вторым входом второго ключа 9.2, является первым управляющим входом электронного коммутатора 9, сигнальным входом которого является первый вход первого ключа 9.1, вторым управляющим входом электронного коммутатора 9 является вход третьего ключа 9.3, а третьим - вход четвертого ключа 9.4, выход которого является выходом электронного коммутатора 9.

Электронный коммутатор 9 управляется с помощью трех сигналов, один из которых поступает с выхода блока сравнения с порогом 4, второй - с выхода первого таймера 8, а третий - с выхода второго таймера 12. Второй ключ 9.2 отключает выход устройства на время действия импульсной помехи, третий ключ 9.3 отключает выход устройства на время действия первого таймера 8, первый ключ 9.1 отключает выход устройства на время между переключением второго 9.2 и третьего 9.3 ключей, а четвертый ключ 9.4 отключает выход устройства на время действия второго таймера 12. Линия задержки 9.5 действует на время длительности импульсной помехи.

Остальные блоки имеют широкое применение. Описание структуры и принципов построения подобных блок-схем можно найти, например, в книге Р.Токхейма «Основы цифровой электроники», перевод с английского под редакцией Е.К.Масловского, Москва, «Мир», 1988 г.

Таким образом, введение дополнительных блоков в заявляемое устройство обеспечивает снижение вероятности ложной синхронизации на структурную помеху в условиях одновременного воздействия структурных и подряд идущих импульсных помех за счет отключения выхода устройства на время воздействия идущих подряд импульсных помех.

Устройство поиска широкополосных сигналов, содержащее последовательно соединенные первый ключ, линейную часть, блок согласованной фильтрации и предварительной обработки сигнала и электронный коммутатор, выход которого является выходом устройства; последовательно соединенные генератор тактовых импульсов и блок управления переключением каналов, выход которого соединен со вторым, управляющим входом линейной части, последовательно соединенные блок сравнения с порогом, первый тактируемый RS-триггер и первый таймер, выход которого соединен со вторым входом первого тактируемого RS-триггера и вторым управляющим входом электронного коммутатора, выход которого соединен с управляющим входом блока управления переключением каналов, причем первый вход ключа является входом устройства, соединенным с входом блока сравнения с порогом, выход которого соединен со вторым входом ключа и первым управляющим входом электронного коммутатора, отличающееся тем, что введены последовательно соединенные второй ключ, второй тактируемый RS-триггер, второй таймер и элемент ИЛИ, при этом выход блока сравнения с порогом соединен со вторым входом второго ключа, первый вход которого соединен с выходом первого тактируемого RS-триггера, выход первого таймера соединен со вторым входом элемента ИЛИ, выход которого соединен со вторым входом второго тактируемого RS-триггера, в электронном коммутаторе дополнительно введен третий управляющий вход, соединенный с выходом второго таймера.