Трехфазный цифровой сигнум-датчик

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБР ЕТЕ НИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

23I22I

Союз Советских

Социалистических

Республик

Зависимое от авт, свидетельства №

Заявлено 27.Х1.1967 (№ 1199738/18-24) Кл, 42птз, 7/00 с присоединением заявки ¹

МПК G 061

УДК 681.325.083.8(088 8) Приоритет

Опубликовано 15.Х1,1968. Бюллетень № 35

Дата опубликования описания 19.П1,1969

Комитет по делам изобретений и открытий при Совете Министров

СССР бД ЧНТ. ИЫ

Авторы изобретения

И. В. Бизин, В. П. Шупов, В. С. Скобелев и Ю. A. Пащенко

Научно-исследовательский и опытно-конструкторский институт автоматизации черной металлургии

Заявитель

ТРЕХФАЗНЫЙ ЦИФРОВОЙ СИГНУМ-ДАТЧИК

Известны трехфазные цифровые сигнумдатчики, содержащие грехразрядный регистр на триггерах, дешифратор, логические схемы

НЕ, ИЛИ, И и индикаторное устройство.

Предложенное устройство отличается тем, что выходы дешифратора попарно соединены с единичным входом одного и нулевым входом последующего триггера регистра, выходы каждого из которых совместно с выходом последующего триггера соединены со схемами И, выходы которых через схему ИЛИ связаны с выходом устройства.

Такое выполнение сигнум-датчика упрощает

его устройство.

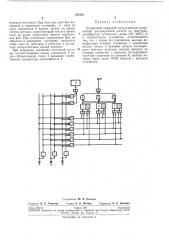

На чертеже приведена блок-схема предлагаемого трехфазного цифрового сигнум-датчика.

Сигнум-датчик построен на потенциальных логических элементах и состоит из трех инверторов НЕ 1, трех статических триггеров 2, схем совпадения 8 и 4, собирательных схем 5 и индикатора неисправности б, Входы 7, 8 и

9 устройства подключены через каналы связи к соответствующим чувствительным элементам, сдвинутым по фазе на 120 эл. Схемы 8 совпадения И на три входа совместно с инверторами 1 образуют дешифратор состояний системы.

Возможны шесть рабочих (нормальных) состояний: 1 0 1; 1 0 0; 1 1 0; 0 1 0; 0 1 1; 0 0 1 и два нерабочих: 0 0 0; 1 1 1, свидетельствующих о ненормальной работе системы (неисправность чувствительных элементов, обрыв канала связи, неисправность входных цепей

5 сигнум-датчика и др.) .

Выходы схем совпадения 8 дешифратора рабочих состояний попарно через две с помощью схем 5 подключены к единичному входу одно10 го и нулевому входу последующего триггера 2 трехразрядного регистра; а выходы схем совпадения дешифратора нерабочих состояний через собирательную схему ИЛИ 5 соединены с индикатором неисправности. Единичные

15 выходы триггеров 2 попарно подключены к схемам 4 совпадения И на два входа, выходы которых через собирательную схему 5 соединены с выходом 10 сигнум-датчика.

20 Сигнум-датчик работает следующим образом, При нормальной работе на выходе одной из шести схем совпадения 8 дешифратора рабочих состояний существует сигнал, который устанавливает один из триггеров 2 в единич25 ное состояние, а последующий за ним — в нулевое. При изменении, преобразуемой величины на один квант в прямом направлении возникает сигнал на выходе другой, соседней схемы совпадения 8, и устанавливает в единич30 ное состояние триггер, ранее находившийся в

231221

Предмет изобретения

Составитель Ю. Н. Колотов

Редактор В. H. Торопова Техред Л. К. Малова Корректор В. В. Крылова

Заказ 300/13 Тираж 530 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, 2

Ти погр афин, п р. Сапунова, 2 нулевом состоянии. При этом два триггера находятся в единичном состоянии, и одна из схем совпадения 4 выдает сигнал на выход сигнум-датчика, существующий там все время, пока на входе происходит прямое чередование фаз. При изменении чередования фаз на обратное в единичном состоянии находится лишь один из триггеров 2 регистра, и на выходе сигнум-датчика сигнал исчезает.

При появлении нерабочих состояний системы соответствующие схемы совпадения 8 через собирательную схему 5 вызывают срабатывание индикатора неисправности 6.

Трехфазный цифровой сигнум-датчик, содержащий трехразрядный регистр иа триггерах, дешифратор, логические схемы НЕ, ИЛИ, И и индикаторное устройство, отличающийся тем, что, с целью его упрощения, выходы дешифратора попарно соединены с единичным входом одного и нулевым входом последующего триггера регистра, выходы каждого из которых совместно с выходом последующего триггера соединены со схемами И, выходы которых через схему ИЛИ связаны с выходом устройства,