Устройство для приема стартстопных сообщений

Иллюстрации

Показать всеИзобретение относится к области связи и может быть использовано в радиолиниях, в проводных, радиорелейных и метеорных линиях связи. Достигаемый технический результат - повышение помехоустойчивости связи. Устройство содержит приемник, амплитудный детектор, пороговые блоки, три формирователя импульсов, три двоичных счетчика, генератор тактовых импульсов (ГТИ), делитель частоты, мультиплексор, счетчик-распределитель, два Д-триггера, оконечный блок, логические элементы, два ключа, два пиковых детектора, три триггера, цифровой компаратор, аттенюатор, сдвиговый регистр, компаратор, фильтр низких частот (ФНЧ). 2 ил.

Реферат

Изобретение относится к области электро- и радиосвязи и может быть использовано в проводных, радио-, радиорелейных и метеорных линиях связи.

Известное устройство для приема стартстопных сообщений содержит последовательно соединенные приемник, амплитудный детектор (АД), фильтр низких частот (ФНЧ), компаратор и запоминающее устройство (ЗУ), сдвиговый регистр и дешифратор, выход которого является выходом устройства. Причем ЗУ, сдвиговый регистр и дешифратор соединены между собой шиной. Кроме того, последовательно соединенные ключ, синхроблок, формирователь импульсов и формирователь пачек импульсов, выход которого соединен с тактовым входом сдвигового регистра. Второй выход формирователя импульсов соединен со счетным входом двоичного счетчика и тактовым входом компаратора. Третий выход формирователя импульсов соединен со вторым входом ключа, первый вход которого соединен с выходом ФНЧ. Последовательно соединенные второй двоичный счетчик, накопитель и пороговое устройство (ПУ), выход которого соединен с управляющим входом дешифратора. При этом выход синхроблока соединен с установочными входами двоичного счетчика и накопителя. Первый выход формирователя импульсов соединен с установочными входами двоичного счетчика и блока выборки и хранения сигнала, счетным выходом второго двоичного счетчика и стробирующими входами сдвигового регистра и накопителя, сигнальный вход которого соединен со вторым входом компаратора и входом блока выборки и хранения сигнала, сигнальный вход которого соединен с выходом ФНЧ, а управляющий вход - с выходом компаратора. Выход двоичного счетчика шиной соединен с информационным входом ЗУ. Вход приемника является входом устройства (см. [1], второй вариант, с.40; и [2] - прототип).

Однако такое устройство имеет большую вероятность ложных тревог.

Наиболее близким по технической сущности к предлагаемому устройству является приемная часть - устройство для приема стартстопных сообщений системы связи [2].

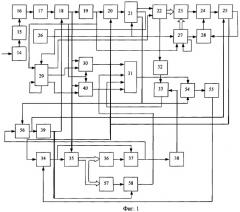

Функциональная схема такого устройства-прототипа приведена на фиг.1.

Это устройство для приема стартстопных сообщений содержит последовательно соединенные приемник 14, АД 15, ФНЧ 16, пороговый блок 17, первый элемент И 18, первый формирователь импульсов 19, первый элемент ИЛИ 20, делитель частоты 21 и первый двоичный счетчик 22, выход которого шиной соединен с входом мультиплексора 23, выход которого через последовательно соединенные сдвиговый регистр 24 и оконечный блок 25 соединен с первым входом второго элемента ИЛИ 28, выход которого соединен с тактовым входом сдвигового регистра 24. Выход ГТИ 26 соединен с тактовым входом делителя частоты 21 и счетным входом второго двоичного счетчика 27, первый выход которого шиной соединен с управляющим входом мультиплексора 23. Второй выход второго двоичного счетчика 27 соединен со вторым входом второго элемента ИЛИ 28. Третий выход второго двоичного счетчика 27 соединен с его запрещающим входом, а установочный вход второго двоичного счетчика 27 соединен с выходом первого формирователя импульсов 19. Кроме того, последовательно соединены счетчик-распределитель 29, первый Д-триггер 30, третий элемент ИЛИ 31, первый триггер 54, первый элемент НЕ 55, четвертый элемент ИЛИ 34 и третий двоичный счетчик 35, выход которого шиной соединен с входами первого 36 и второго 57 цифровых компараторов. Второй выход счетчика-распределителя 29 соединен со стробирующим входом второго Д-триггера 40, выход которого соединен с четвертым входом третьего элемента ИЛИ 31. Третий выход счетчика-распределителя 29 соединен с его установочным входом, а четвертый выход - с установочным входом первого двоичного счетчика 22. Первый вход счетчика-распределителя 29 соединен с установочными входами первого 30 и второго 40 Д-триггеров, а также с выходом первого формирователя импульсов 19. Счетный вход счетчика-распределителя 29 соединен со вторым выходом делителя частоты 21. Информационные входы первого 30 и второго 40 Д-триггеров соединены с выходом первого элемента И 18 и счетным входом третьего двоичного счетчика 35. Выход первого цифрового компаратора 36 через последовательно соединенные второй триггер 37 и второй элемент НЕ 38 соединен с первым входом второго элемента И 33. Выход второго цифрового компаратора 57 через четвертый элемент И 58 соединен со вторым входом третьего элемента ИЛИ 31, третий вход которого подсоединен к выходу второго элемента И 33. Выход переполнения первого двоичного счетчика 22 через второй формирователь импульса 32 соединен со вторым входом второго элемента И 33. Выход четвертого элемента ИЛИ 34 соединен с установочным входом второго триггера 37, выход которого соединен со вторым входом третьего элемента И 56, первый вход которого соединен со вторым входом первого триггера 54 и третьим выходом делителя частоты 21. Выход третьего элемента И 56 соединен с тактовым входом оконечного блока 25 и входом третьего элемента НЕ 39, выход которого соединен со вторыми входами первого 18 и четвертого 58 элементов И. Второй выход оконечного блока 25 соединен со вторыми входами первого 20 и четвертого 34 элементов ИЛИ.

Устройство для приема стартстопных сообщений работает следующим образом.

Принимаемый сигнал после фильтрации в приемнике 14, амплитудного детектирования в блоке 15 и фильтрации в ФНЧ 16 поступает на вход порогового блока 17 с порогом V. При отсутствии помех на его выходе в момент превышения сигналом порога формируется импульс с уровнем логической «1» и длительностью, близкой к значению τ, на втором входе первого элемента И 18 действует сигнал логической «1», на выходе элемента ИЛИ 31 логического «0» и на выходе триггера 54 логической «1». Поэтому первый импульс принимаемого сигнала (синхроимпульс) проходит через блок 18 и на выходе блока 19 по его переднему фронту формируется короткий импульс, который запускает счетчик - распределитель 29 и осуществляет через блок 20 сброс делителя частоты 21. На первом, втором и третьем выходах последнего формируются меандры с периодами следования импульсов, соответственно, равными τ, 0,5τ и 16τ, путем деления частоты ГТИ 26, равной 32/τ, а на четвертом выходе счетчика-распределителя 29 создается импульс длительности 0,5τ с задержкой относительно первого выходного импульса блока 19 на τ, который обнуляет блок 22 своим передним фронтом. После этого в блоке 22 осуществляется подсчет импульсов. В результате к моменту прихода второго импульса с выхода блока 19 в нем оказывается записанным в двоичном виде временное положение второго импульса относительно синхроимпульса.

Этот импульс производит обнуление и разрешение на подсчет импульсов в блоке 27, поступающих с ГТИ 26. В результате сигналами с К разрядов блока 27, действующими через шину на управляющие входы мультиплексора 23, данные К разрядов блока 22 поочередно поступают на вход сдвигового регистра 24 с (К+1)m разрядами, на тактовый вход которого через блок 28 поступают импульсы с выхода первого разряда блока 27. При поступлении (К+1)-го импульса с ГТИ 26 на вход последнего сигнал с его второго выхода запрещает подсчет остальных импульсов до поступления следующего импульса с выхода блока 19.

Аналогичным образом осуществляется определение временного положения остальных (m-1) информационных импульсов. При отсутствии помех, как и раньше, после приема последнего из них на выходе элемента И 56 формируется положительный перепад напряжения (сигнал «сообщение принято»), который запускает оконечный блок 25 (например, ЭЦВМ). При этом на его первом выходе формируются тактовые импульсы с определенной частотой, считывающие на его вход данные с блока 24. После обработки информации в блоке 25 на его втором выходе формируется положительный сигнал «сброс» с длительностью большей 8τ, который положительным фронтом через блок 20 обнуляет блок 21 и через блок 34 блок 35 и триггер 37.

При наличии помех сигнал «сообщение принято» появится, если произойдут одновременно следующие события: на интервалах времени Тn>8τ до приема синхросигнала (стартовая пауза) и после последнего τ-го импульса сообщения (стоповая пауза) не появятся ложные импульсы на выходе блока 17, число импульсов на его выходе N будет равным (m+1), не произойдет переполнение счетчика 22, длительность принимаемых импульсов окажется меньше, например, 2τ, а защитной паузы - больше, например, 1,5τ. Контроль длительности стартовой паузы осуществляется посредством блока 21.

Если в момент действия первого импульса на выходе блока 19 на третьем выходе блока 21 уровень сигнала равен логической «1» (что свидетельствует о том, что Тn>8τ), то это означает, что произошло обнуление триггера 54 и через элементы НЕ 55 и ИЛИ 34 счетчика 35, в котором начинается подсчет числа импульсов, поступающих с выхода блока 18. При N=(m+1) на выходе блока 36 появится импульс, который установит триггер 37 в единичное состояние, и откроется элемент И 56.

Если при этом у последнего (m+1)-го импульса принимаемого сигнала уровень сигнала на третьем выходе блока 21 будет равным «1» (что свидетельствует о наличии стоповой паузы), то на выходе элемента И 56 появится положительный импульс, разрешающий прием сообщения, а на выходе блока 39 - сигнал логического «0», запрещающий передачу сигналов через элемент И 18. Д-триггеры 30 и 40 предназначены для контроля длительностей импульсов сообщения. Выходными импульсами блока 19 они обнуляются; на их вторые входы подаются импульсы с выхода блока 18, а на третьи - с первого и второго выходов счетчика-распределителя 29, соответственно; по заднему фронту последнего осуществляется его блокировка до прихода следующего импульса с выхода блока 19.

Если отсутствует перекрытие по времени импульсов, действующих на первых и вторых их входах, то их состояние не изменяется. При отсутствии стартовой паузы в блоке 35 N будет меньше (m+1), на выходе элемента НЕ 38 (на втором входе блока 33) будет действовать сигнал логической «1» и, если при этом произойдет переполнение блока 22, то на выходах блока 32, блока 33 и элемента ИЛИ 31 появится импульс, устанавливающий триггер 54 в исходное состояние.

То же самое произойдет при переполнении, если N=(m+1). Такой же сигнал возникнет на ее выходе, если произойдет перекрытие импульсов хотя бы в одном из Д-триггеров 30 и 40, или в случае, когда число N окажется большим (m+1) при выполнении прочих условий. Последнее приведет к появлению импульса на выходе блока 39, который через открытый выходным сигналом блока 39 элемент И 58 и элемент ИЛИ 31 поступит на первый вход триггера 54.

Однако такое устройство имеет низкую помехоустойчивость связи.

Оно может начать работу только тогда, когда на интервале времени Тn>8τ отсутствуют превышения помехой порога V в блоке 17. Если при этом первый импульс сигнала придет на вход приемника с задержкой (2+q)τ и в интервале задержки импульс помехи превысит порог и окажется на разрешенной позиции, то это приведет к приему искаженного сообщения или к сбросу устройства. То же самое призойдет, если порог будет превышен помехой на таком же интервале времени после последнего импульса сообщения. Вероятность превышения помехой порога определяется только его значением V (который устанавливается вполне определенным) является постоянной величиной и не зависит от уровня сигнала. В результате этого увеличение последнего не может привести к повышению помехоустойчивости связи.

Для устранения указанного недостатка в устройство для приема стартстопных сообщений, содержащее последовательно соединенные приемник, амплитудный детектор, ФНЧ, пороговый блок, первый элемент И, первый формирователь импульсов, первый элемент ИЛИ, делитель частоты и первый двоичный счетчик, выход которого шиной соединен с входом мультиплексора, выход которого через последовательно соединенные сдвиговый регистр и оконечный блок соединен с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом сдвигового регистра. Выход ГТИ соединен с тактовым входом делителя частоты и счетным входом второго двоичного счетчика, первый выход которого шиной соединен с управляющим входом мультиплексора. Второй выход второго двоичного счетчика соединен со вторым входом второго элемента ИЛИ. Третий выход второго двоичного счетчика соединен с его запрещающим входом, а установочный вход второго двоичного счетчика соединен с выходом первого формирователя импульсов. Кроме того, последовательно соединены счетчик-распределитель, первый Д-триггер и третий элемент ИЛИ, последовательно соединены четвертый элемент ИЛИ и третий двоичный счетчик, выход которого шиной соединен со входом цифрового компаратора. Второй выход счетчика-распределителя соединен со стробирующим входом второго Д-триггера, выход которого соединен с третьим входом третьего элемента ИЛИ. Третий выход счетчика-распределителя соединен с его установочным входом, а четвертый выход - с установочным входом первого двоичного счетчика. Первый вход счетчика-распределителя соединен с установочными входами первого 30 и второго 40 Д-триггеров, а также с выходом первого формирователя импульсов. Счетный вход счетчика-распределителя соединен со вторым выходом делителя частоты. Информационные входы первого и второго Д-триггеров соединены с выходом первого элемента И и счетным входом третьего двоичного счетчика. Выход цифрового компаратора через последовательно соединенные второй триггер и второй элемент НЕ соединен с первым входом второго элемента И. Второй вход третьего элемента ИЛИ подсоединен к выходу второго элемента И. Выход переполнения первого двоичного счетчика через второй формирователь импульса соединен со вторым входом второго элемента И. Выход четвертого элемента ИЛИ соединен с установочным входом второго триггера, вход третьего элемента НЕ соединен с тактовым входом оконечного блока, а его выход соединен со вторым входом первого элемента И. Второй выход оконечного блока соединен со вторыми входами первого и четвертого элементов ИЛИ. Кроме того, содержит первый триггер и третий элемент И. Введены: третьи входы у третьего элемента И и четвертого элемента ИЛИ, а также - пятый элемент ИЛИ, последовательно соединенные второй пороговый блок, первый ключ, первый пиковый детектор и компаратор, выход которого подключен к третьему входу четвертого элемента ИЛИ, последовательно соединенные второй ключ, первый вход которого подсоединен к первому входу первого ключа, второй пиковый детектор и аттенюатор, выход которого подключен к второму входу компаратора, третий формирователь импульса, выход которого соединен с первым входом третьего элемента И, выход которого подключен к счетному входу первого триггера, выход которого соединен со вторым входом третьего элемента И, кроме того, третий триггер, причем вход второго порогового блока соединен с выходом ФНЧ, вход третьего формирователя импульса и счетный вход третьего триггера подключены к выходу первого порогового блока, прямой выход третьего триггера соединен со вторыми входами первого и второго ключей, а его инверсный выход подключен к третьему входу третьего элемента И, выход второго триггера соединен со входом третьего элемента НЕ, установочный вход третьего триггера подсоединен к установочному входу первого триггера, к вторым входам первого и второго пиковых детекторов и к выходу пятого элемента ИЛИ, выход третьего элемента И подключен также к установочному входу компаратора, первый вход четвертого элемента ИЛИ подключен к выходу третьего элемента ИЛИ и к первому входу пятого элемента ИЛИ, второй вход которого соединен со вторым выходом оконечного блока.

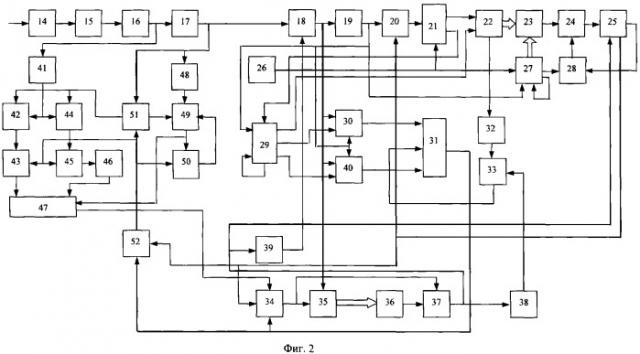

На фиг.2 представлена функциональная схема предлагаемого устройства для приема стартстопных сообщений.

Оно содержит последовательно соединенные приемник 14, амплитудный детектор 15, ФНЧ 16, первый пороговый блок 17, первый элемент И 18, первый формирователь импульсов 19, первый элемент ИЛИ 20, делитель частоты 21 и первый двоичный счетчик 22, выход которого шиной соединен с входом мультиплексора 23, выход которого через последовательно соединенные сдвиговый регистр 24 и оконечный блок 25 соединен с первым входом второго элемента ИЛИ 28, выход которого соединен с тактовым входом сдвигового регистра 24. Выход ГТИ 26 соединен с тактовым входом делителя частоты 21 и счетным входом второго двоичного счетчика 27, первый выход которого шиной соединен с управляющим входом мультиплексора 23. Второй выход второго двоичного счетчика 27 соединен со вторым входом второго элемента ИЛИ 28. Третий выход второго двоичного счетчика 27 соединен с его запрещающим входом, а установочный вход второго двоичного счетчика 27 соединен с выходом первого формирователя импульсов 19. Кроме того, последовательно соединены счетчик-распределитель 29, первый Д-триггер 30 и третий элемент ИЛИ 31, последовательно соединены четвертый элемент ИЛИ 34 и третий двоичный, счетчик 35, выход которого шиной соединен со входом цифрового компаратора 36. Второй выход счетчика-распределителя 29 соединен со стробирующим входом второго Д-триггера 40, выход которого соединен с третьим входом третьего элемента ИЛИ 31. Третий выход счетчика-распределителя 29 соединен с его установочным входом, а четвертый выход с установочным входом первого двоичного счетчика 22. Первый вход счетчика-распределителя 29 соединен с установочными входами первого 30 и второго 40 Д-триггеров, а также с выходом первого формирователя импульсов 19. Счетный вход счетчика-распределителя 29 соединен со вторым выходом делителя частоты 21. Информационные входы первого 30 и второго 40 Д-триггеров соединены с выходом первого элемента И 18 и счетным входом третьего двоичного счетчика 35. Выход цифрового компаратора 36 через последовательно соединенные второй триггер 37 и второй элемент НЕ 38 соединен с первым входом второго элемента И 33. Второй вход третьего элемента ИЛИ 31 подсоединен к выходу второго элемента И 33. Выход переполнения первого двоичного счетчика 22 через второй формирователь импульса 32 соединен со вторым входом второго элемента И 33. Выход четвертого элемента ИЛИ 34 соединен с установочным входом второго триггера 37, вход третьего элемента НЕ 39 соединен с тактовым входом оконечного блока 25 и с выходом второго триггера 37, а его выход соединен со вторым входом первого элемента И 18. Второй выход оконечного блока 25 соединен со вторыми входами первого 20 и четвертого 34 элементов ИЛИ. Кроме того, содержит первый триггер 50, третий элемент И 49, третий триггер 51 и пятый элемент ИЛИ 52; а также последовательно соединенные второй пороговый блок 41, первый ключ 42, первый пиковый детектор 43 и компаратор 44, выход которого подключен к третьему входу четвертого элемента ИЛИ 34, последовательно соединенные второй ключ 45, первый вход которого подсоединен к первому входу первого ключа 42, второй пиковый детектор 45 и аттенюатор 46, выход которого подключен к второму входу компаратора 47, третий формирователь импульса 48, выход которого соединен с первым входом третьего элемента 49 И, выход которого подключен к счетному входу первого триггера 50 выход которого соединен со вторым входом третьего элемента И; причем вход второго порогового блока 41 соединен с выходом ФНЧ 16, вход третьего формирователя импульса 48 и счетный вход третьего триггера 51 подключены к выходу первого порогового блока 17, выход второго триггера 37 подключен ко входу третьего элемента НЕ 39, прямой выход третьего триггера 51 соединен со вторыми входами первого 42 и второго 44 ключей, а его инверсный выход подключен к третьему входу третьего элемента 49 И, установочный вход третьего триггера 51 подсоединен к установочному входу первого триггера 50, к вторым входам первого 43 и второго 45 пиковых детекторов и к выходу пятого элемента ИЛИ 52, выход третьего элемента 49 И подключен также к установочному входу компаратора 47, первый вход четвертого элемента ИЛИ 34 подключен к выходу третьего элемента ИЛИ 31 и первому входу пятого элемента ИЛИ 52, второй вход которого соединен со вторым выходом оконечного блока 25.

Устройство для приема стартстопных сообщений работает следующим образом.

Принимаемый сигнал после фильтрации в приемнике 14, амплитудного детектирования в блоке 15 и фильтрации в ФНЧ 16 поступает на вход порогового блока 17. При отсутствии помех на его выходе в момент превышения сигналом порога формируется импульс с уровнем логической «1» и длительностью, близкой к значению τ, на втором входе первого элемента И 18 действует сигнал логической «1», на выходе элемента ИЛИ 31 логического «0». Поэтому первый импульс принимаемого сигнала (синхроимпульс) проходит через блок 18 и на выходе блока 19 по его переднему фронту формируется короткий импульс, который запускает счетчик - распределитель 29 и осуществляет через блок 20 сброс делителя частоты 21. На первом и втором выходах последнего формируются меандры с периодами следования импульсов, соответственно, равными τ и 0,5τ, путем деления частоты ГТИ 26, равной 32/τ, а на четвертом выходе счетчика-распределителя 29 создается импульс длительности 0,5τ с задержкой относительно первого выходного импульса блока 19 на τ, который обнуляет блок 22 своим передним фронтом. После этого в блоке 22 осуществляется подсчет импульсов. В результате к моменту прихода второго импульса с выхода блока 19 в нем оказывается записанным в двоичном виде временное положение второго импульса относительно синхроимпульса.

Максимальное напряжение U1 синхросигнала после порогового блока 41 с уровнем U1-V (где V - порог такой же, что и в блоке 17) через открытый выходным напряжением с прямого выхода триггера 51 ключ 42 поступает на вход пикового детектора 43 и запоминается в нем. Второй ключ 44 при этом находится в исходном закрытом состоянии. Положительным фронтом второго выходного импульса блока 17 состояние триггера 51 изменяется на противоположное, в результате чего ключ 42 закрывается, ключ 44 открывается, а на третий вход элемента 49 поступает положительный сигнал. По отрицательному фронту второго выходного импульса блока 17 в формирователе 48 создается короткий импульс, который через блок 49 поступает на третий вход компаратора 47, на выходе которого создастся положительный импульс, если напряжение на втором его входе окажется больше, чем на первом, это приведет к обнулению блока 35. Второй импульс с выхода блока 41 с уровнем U2-V запоминается в пиковом детекторе 45, ослабляется в аттенюаторе 46 в 1,5 раза и поступает на второй вход блока 47. Так как при отсутствии помех U1=U2, то на выходе последнего положительный импульс не создастся. При поступлении импульса с выхода блока 48 также изменяет свое состояние на противоположное триггер 50, в результате чего запрещается прохождение через элемент 49 следующих импульсов с выхода блока 48. Указанная процедура позволяет исключить в устройстве контроль стартовой и стоповой пауз.

Второй выходной импульс формирователя 19 производит обнуление и разрешение на подсчет импульсов в блоке 27, поступающих с ГТИ 26. В результате сигналами с К разрядов блока 27, действующими через шину на управляющие входы мультиплексора 23, данные К разрядов блока 22 поочередно поступают на вход сдвигового регистра 24 с (К+1) m разрядами, на тактовый вход которого через блок 28 поступают импульсы с выхода первого разряда блока 27. При поступлении (К+1)-го импульса с ГТИ 26 на вход последнего сигнал с его второго выхода запрещает подсчет остальных импульсов до поступления следующего импульса с выхода блока 19.

Аналогичным образом осуществляется определение временного положения остальных (m-1) информационных импульсов. При отсутствии помех, как и раньше, после приема последнего из них на входе элемента НЕ 39 формируется положительный перепад напряжения (сигнал «сообщение принято»), который запускает оконечный блок 25 (например, ЭЦВМ). При этом на его первом выходе формируются тактовые импульсы с определенной частотой, считывающие на его вход данные с блока 24. После обработки информации в блоке 25 на его втором выходе формируется положительный сигнал «сброс» с длительностью большей 8τ, который положительным фронтом через блок 20 обнуляет блок 21, через блок 34 блок 35 и триггер 37 и через блок 52 блоки 43, 45, 50 и 51.

При наличии помех сигнал «сообщение принято» появится, если произойдут одновременно следующие события: число импульсов на выходе блока 17 N будет равным (m+1), не произойдет переполнение счетчика 22, длительность принимаемых импульсов окажется меньше, например, 2τ, а защитной паузы - больше, например, 1,5τ и не появится импульс на выходе компаратора Д-триггеры 30 и 40 предназначены для контроля длительностей импульсов сообщения. Выходными импульсами блока 19 они обнуляются; на их вторые входы подаются импульсы с выхода блока 18, а на третьи - с первого и второго выходов счетчика-распределителя 29, соответственно; по заднему фронту последнего осуществляется его блокировка до прихода следующего импульса с выхода блока 19. Если отсутствует перекрытие по времени импульсов, действующих на первых и вторых их входах, то их состояние не изменяется. Если при этом произойдет переполнение блока 22, то на выходах блока 32, блока 33 и элемента ИЛИ 31 появится импульс, устанавливающий устройство в исходное состояние. То же самое произойдет при переполнении, если N=(m+l). Такой же сигнал возникнет на ее выходе, если произойдет перекрытие импульсов хотя бы в одном из Д-триггеров 30 и 40.

Если на выходе компаратора 47 возникнет импульс, то считается, что непосредственно перед сообщением произошло превышение помехой порога. При этом будет осуществлен сброс блока 35 и обработка в устройстве сообщения начнется с синхроимпульса. После появления сигнала «сброс» на втором выходе блока 25 триггеры 50, 51 и блоки 43 и 45 установятся в исходное состояние.

Введение блоков 41-52 позволяет осуществить селекцию синхроимпульса при превышении порога помехой до начала сообщения. Если такое превышение происходит (вероятность его мала и равна примерно 10-4), то за синхроимпульс принимается импульс помехи. Но уровень ее (U1-V) с большой вероятностью будет меньше (U2-V) (где U2 в данном случае - уровень синхроимпульса) и если при этом на выходе блока 47 появится импульс, то происходит обнуление блока 35 и обработка принимаемого сигнала, начиная с синхроимпульса, возобновляется. Статистическое моделирование устройства показало, что помехоустойчивость связи при таком методе приема сообщения возрастает на порядок.

Таким образом, применение предложенного устройства позволяет повысить помехоустойчивость связи.

Все блоки, входящие в устройство, являются известными. Пиковый детектор может быть выполнен, например, по схеме рис.8.12 в книге Б.И.Горшкова «Радиоэлектронные устройства». М.: Радио и связь, 1984.

Источники информации

1. В.И.Николаев, Г.Б.Волобуев, В.И.Ледовских. О помехоустойчивости m-ичных сигналов при стартстопной передаче сообщений. Телекоммуникации, №1, 2001, с.38-41, (ООО «Наука и технологии», М., 2001).

2. Патент РФ №2218669, Н04L 25/38, Н04J 11/00.

Устройство для приема стартстопных сообщений, содержащее последовательно соединенные приемник, амплитудный детектор, ФНЧ, пороговый блок, первый элемент И, первый формирователь импульсов, первый элемент ИЛИ, делитель частоты и первый двоичный счетчик, выход которого шиной соединен с входом мультиплексора, выход которого через последовательно соединенные сдвиговый регистр и оконечный блок соединен с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом сдвигового регистра, причем выход ГТИ соединен с тактовым входом делителя частоты и счетным входом второго двоичного счетчика, первый выход которого шиной соединен с управляющим входом мультиплексора, второй выход второго двоичного счетчика соединен со вторым входом второго элемента ИЛИ, третий выход второго двоичного счетчика соединен с его запрещающим входом, а установочный вход второго двоичного счетчика соединен с выходом первого формирователя импульсов, кроме того, последовательно соединенные счетчик-распределитель, первый Д-триггер и третий элемент ИЛИ, последовательно соединенные четвертый элемент ИЛИ и третий двоичный счетчик, выход которого шиной соединен со входом цифрового компаратора, второй выход счетчика-распределителя соединен со стробирующим входом второго Д-триггера, выход которого соединен с третьим входом третьего элемента ИЛИ, третий выход счетчика-распределителя соединен с его установочным входом, а четвертый выход - с установочным входом первого двоичного счетчика, первый вход счетчика-распределителя соединен с установочными входами первого и второго Д-триггеров, а также с выходом первого формирователя импульсов, счетный вход счетчика-распределителя соединен со вторым выходом делителя частоты, информационные входы первого и второго Д-триггеров соединены с выходом первого элемента И и счетным входом третьего двоичного счетчика, выход цифрового компаратора через последовательно соединенные второй триггер и второй элемент НЕ соединен с первым входом второго элемента И, второй вход третьего элемента ИЛИ подсоединен к выходу второго элемента И, выход переполнения первого двоичного счетчика через второй формирователь импульса соединен со вторым входом второго элемента И, выход четвертого элемента ИЛИ соединен с установочным входом второго триггера, вход третьего элемента НЕ соединен с тактовым входом оконечного блока, а его выход соединен со вторым входом первого элемента И, второй выход оконечного блока соединен со вторыми входами первого и четвертого элементов ИЛИ, кроме того, первый триггер и третий элемент И, отличающееся тем, что введены третьи входы у третьего элемента И и четвертого элемента ИЛИ, а также пятый элемент ИЛИ, последовательно соединенные второй пороговый блок, первый ключ, первый пиковый детектор и компаратор, выход которого подключен к третьему входу четвертого элемента ИЛИ, последовательно соединенные второй ключ, первый вход которого подсоединен к первому входу первого ключа, второй пиковый детектор и аттенюатор, выход которого подключен к второму входу компаратора, третий формирователь импульса, выход которого соединен с первым входом третьего элемента И, выход которого подключен к счетному входу первого триггера, выход которого соединен со вторым входом третьего элемента И, а также третий триггер, причем вход второго порогового блока соединен с выходом ФНЧ, вход третьего формирователя импульса и счетный вход третьего триггера подключены к выходу первого порогового блока, прямой выход третьего триггера соединен со вторыми входами первого и второго ключей, а его инверсный выход подключен к третьему входу третьего элемента И, выход второго триггера соединен со входом третьего элемента НЕ, установочный вход третьего триггера подсоединен к установочному входу первого триггера, к вторым входам первого и второго пиковых детекторов и к выходу пятого элемента ИЛИ, выход третьего элемента И подключен также к установочному входу компаратора, первый вход четвертого элемента ИЛИ подключен к выходу третьего элемента ИЛИ и первому входу пятого элемента ИЛИ, второй вход которого соединен со вторым выходом оконечного блока.