Временной дискриминатор устройства тактовой синхронизации

Иллюстрации

Показать всеИзобретение относится к области радиосвязи и может применяться в демодуляторах радиорелейных систем связи, использующих сигналы с квадратурной амплитудной манипуляцией. Технический результат заключается в повышении помехоустойчивости устройства. Это достигается тем, что сигнал ошибки вырабатывается всякий раз, когда на двух соседних тактовых интервала происходит смена значения модулирующего символа, а не только, когда происходит изменение его знака. Устройство содержит последовательно соединенные решающее устройство (РУ) (1), сумматор (4), второй вход которого соединен с выходом РУ (1) через последовательно соединенные инвертор знака (3) и первый блок задержки (БЗ) (2), и перемножитель (6), а также второй БЗ (5), соединенный со вторым входом устройства. Введены последовательно соединенные второй сумматор (7), первый вход которого соединен с выходом БЗ (2), второй вход - с выходом инвертора знака (3), делитель на два (8) и третий сумматор (9), второй вход которого соединен с выходом БЗ (5), а его выход - со вторым входом перемножителя (6). РУ (1) выносит решение о значении принимаемого модулирующего символа, а не о его знаке. 1 з.п. ф-лы, 15 ил., 1 табл.

Реферат

Предлагаемое изобретение относится к области радиосвязи и может применяться в демодуляторах радиорелейных систем связи, использующих сигналы с квадратурной амплитудной манипуляцией.

Сигналы с квадратурной амплитудной манипуляцией (КАМ сигналы) удобно представить в виде суммы квадратурных составляющих:

где А - амплитуда сигнала, ω0=2πf0 - несущая частота сигнала, I(t) и Q(t) - модулирующие функции, которые задают метод модуляции.

Модулирующие функции I(t) и Q(t) можно представить в виде

где ai и bi - многоуровневые модулирующие символы, длительностью T, p(t) - элементарный модулирующий сигнал, обычно формируемый с помощью фильтров. Параметры фильтров выбирают так, чтобы отсутствовала межсимвольная интерференция.

Сигнальные точки КАМ сигналов расположены в узлах квадратной решетки (фиг.1). В частности, модулирующие символы ai и bi для сигналов ФМ4 принимают значения ±1, а для сигналов КАМ256 - от -15 до 15 с шагом 2.

Упрощенная структурная схема когерентного демодулятора КАМ сигналов приведена на фиг.2. В усилителе промежуточной частоты (УПЧ) с регулируемым коэффициентом передачи осуществляется усиление и фильтрация сигнала. В формирователе квадратурных сигналов (ФК) осуществляется перенос сигнала на видеочастоту с формированием отсчетов синфазного и квадратурного сигналов. Устройство выделения информации (УВИ) осуществляет выделение информации из принимаемого сигнала, а устройство тактовой синхронизации (УТС) - сигнал тактовой синхронизации. Поддержание постоянного уровня сигнала на входе УВИ осуществляет устройство автоматической регулировки усиления (АРУ). Опорное колебание, с точностью до фазы, для когерентного приема сигналов выделяется из информационного сигнала устройством выделения несущей частоты (УВН). С помощью адаптивного корректора (АК) осуществляется коррекция неидеальных частотных характеристик канала.

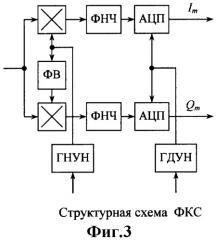

Структурная схема формирователя цифровых отсчетов квадратурных сигналов приведена на фиг.3. ФК состоит из двух перемножителей (фазовых детекторов), генератора сигнала несущей частоты (ГНУН), управляемого напряжением, фазовращателя сигнала несущей частоты на 90° (ФВ), двух фильтров нижних частот (ФНЧ), двух аналого-цифровых преобразователей (АЦП) и генератора частоты дискретизации (ГДУН), управляемого напряжением. Частота дискретизации сигналов в АЦП обычно равна удвоенной тактовой частоте входного сигнала: fд=2fm. Формирование на выходе АЦП двух отсчетов сигнала за длительность одного информационного символа необходимо для работы временного дискриминатора УТС.

Более подробная структурная схема когерентного демодулятора КАМ сигналов приведена на фиг.4. Здесь ФОС - фильтр основной селекции, ДМ - демультиплексор, в котором осуществляется разделение отсчетов сигнала на четные и нечетные, АК - адаптивный корректор, РУ - решающее устройство, ФНЧ - фильтр нижних частот, АД - амплитудный детектор устройства АРУ, ВД - временной дискриминатор УТС, ФД - фазовый детектор УВН.

Временной дискриминатор УТС состоит из двух временных дискриминаторов (один из них работает по отсчетам синфазного сигнала I2n-1, I2n, второй - по отсчетам квадратурного сигнала Q2n-1, Q2n), сигналы с выходов которых складываются и подаются на ФНЧ УТС.

Устройства тактовой синхронизации отличаются алгоритмами работы временных дискриминаторов. В частности, алгоритм с опережающим и запаздывающим стробированием и синфазно-среднефазный алгоритм описаны в [Спилкер Дж. Цифровая спутниковая связь. Пер. с англ. / Под ред. В.В.Маркова. - М.: Связь, 1979. - 592 с., ил.]. Другой возможный алгоритм описан в [Mueller K.H., Muller M. Timing recovery in digital synchronous data receivers. - IEEE Trans. Commun., vol. COM-24, pp.516-531, May 1976]. В последнем случае временной дискриминатор состоит из первого перемножителя, первый вход которого соединен с первым входом устройства через решающее устройство, второй вход - со вторым входом устройства через первую линию задержки на время T, второго перемножителя, первый вход которого соединен с первым входом устройства через решающее устройство и вторую линию задержки на время Т, второй вход - со вторым входом устройства, и сумматора, на входы которого подаются сигналы с выходов перемножителей (выход второго перемножителя берется с обратным знаком). Перечисленные выше алгоритмы работы временных дискриминаторов имеют низкую помехоустойчивость при приеме КАМ сигналов.

Наиболее близким по технической сущности и достигаемому положительному эффекту, принятым за прототип, является временной дискриминатор, алгоритм работы которого описан в, например [Парамонов А.М., Куропаткин О.И., Сосенко И.В. Выбор параметров фильтров устройств автоматического регулирования демодуляторов ФМ сигналов при их реализации на микросхемах фирмы Intersil. - Chip News / Инженерная электроника, 2001, №9, с.14-20].

Следует отметить, что этот алгоритм является цифровой реализацией синфазно-среднефазного алгоритма.

Математически алгоритм работы этого временного дискриминатора можно записать в виде

где функция sgn(x) означает знак х и принимает значения ±1.

На фиг.5 представлена структурная схема этого устройства для, например, синфазного сигнала. Устройство содержит последовательно соединенные решающее устройство 1, вход которого соединен с первым входом устройства (I2n), сумматор 4, второй вход которого соединен с выходом решающего устройства 1 через последовательно соединенные инвертор знака 2 и первый блок задержки 3 на время T, и перемножитель 6, второй вход которого соединен со вторым входом устройства (I2n-1) через второй блок задержки 5 на время T/2, а его выход - с выходом устройства.

Устройство работает следующим образом. На входы ВД поступают отсчеты синфазного (или квадратурного) сигнала в конце (I2n-1) и в середине символов (I2n), как это показано на фиг.6 (здесь в качестве примера использован вид модуляции ФМ4 (КАМ4) и последовательность символов 101). Сигнал ошибки с точностью до знака равен отсчетам сигнала в конце символа. В решающем устройстве 1 выносится решение о знаке принимаемого символа (1 или -1), а на выходе сумматора 4 - решение о наличии и направлении перехода символов на двух соседних тактовых интервалах. Сигнал на выходе сумматора 4 принимает значения: 0 (переход отсутствует), 1 (переход из -1 в 1), или -1 (переход из 1 в -1). Сигнал ошибки на выходе ВД формируется путем перемножения отсчета сигнала в конце символа (I2n-1), задержанного на время T/2 во втором блоке задержки 5, на сигнал на выходе сумматора 4. В частности, когда переход отсутствует, сигнал ошибки равен нулю.

Описанный выше алгоритм работы временного дискриминатора широко используется и при приеме КАМ сигналов.

Диаграммы, поясняющие работу временного дискриминатора для сигналов КАМ256 при отсутствии помех и при фиксированной ошибке, равной 7/4, приведены на фиг.7. Здесь размах сигналов 1, 2, 6, 7 и 8 уменьшен в 16 раз.

Недостатком описанного устройства является его низкая помехоустойчивость.

Цель изобретения - повышение помехоустойчивости устройства.

Поставленная цель достигается тем, что во временной дискриминатор, содержащий последовательно соединенные решающее устройство, вход которого соединен с первым входом устройства, сумматор, второй вход которого соединен с выходом решающего устройства через последовательно соединенные инвертор знака и первый блок задержки, и перемножитель, выход которого соединен с выходом устройства, а также второй блок задержки, соединенный со вторым входом устройства, введены последовательно соединенные второй сумматор, первый вход которого соединен с выходом первого блока задержки, второй вход - с выходом инвертора знака, делитель на два и третий сумматор, второй вход которого соединен с выходом второго блока задержки, а его выход - со вторым входом перемножителя, а решающее устройство выполнено в виде набора компараторов, первые входы которых соединены с первым входом устройства, а на вторые входы подаются пороговые уровни, и логического устройства, входы которого соединены с выходами компараторов, а его выход - с выходом решающего устройства.

Анализ существенных отличий предлагаемого изобретения показывает, что второй сумматор, делитель на два и третий сумматор, а также решающее устройство, выполненное в виде набора компараторов и логического устройства, не используется в прототипе.

Фиг.1. Фазовые портреты многопозиционных КАМ сигналов: а - ФМ4, б - KAM16, в - КАМ32, г - КАМ64, д - КАМ128, е - КАМ256. Показывают расположение сигнальных точек КАМ сигналов на фазовой плоскости.

Фиг.2. Упрощенная структурная схема когерентного демодулятора КАМ сигналов.

Фиг.3. Структурная схема формирователя квадратурных сигналов (ФКС).

Фиг.4. Структурная схема когерентного демодулятора КАМ сигналов.

Фиг.5. Структурная схема временного дискриминатора (прототипа).

Фиг.6. Формирование сигнала ошибки во временном дискриминаторе (прототипе).

Фиг.7. Диаграммы временного дискриминатора (прототипа).

Фиг.8. Структурная схема временного дискриминатора (заявляемого устройства).

Фиг.9. Диаграммы временного дискриминатора (заявляемого устройства).

Фиг.10. Дискриминационные характеристики временного дискриминатора (прототипа и заявляемого устройства) для сигналов ФМ4.

Фиг.11. Флуктуационные характеристики временного дискриминатора (прототипа и заявляемого устройства) для сигналов ФМ4.

Фиг.12. Дискриминационные характеристики временного дискриминатора (прототипа) для сигналов КАМ256.

Фиг.13. Флуктуационные характеристики временного дискриминатора (прототипа) для сигналов КАМ256.

Фиг.14. Дискриминационные характеристики временного дискриминатора (заявляемого устройства) для сигналов КАМ256.

Фиг.15. Флуктуационные характеристики временного дискриминатора (заявляемого устройства) для сигналов КАМ256.

Математически алгоритм работы заявляемого временного дискриминатора можно записать в виде

де - оценки квадратурных сигналов, формируемые на выходе решающего устройства.

Отметим, что алгоритм (4) совпадает с алгоритмом (3) для сигналов ФМ4.

Предлагаемое устройство изображено на фиг.8. Устройство содержит последовательно соединенные решающее устройство 1, вход которого соединен с первым входом устройства, первый сумматор 4, второй вход которого соединен с выходом решающего устройства 1 через последовательно соединенные инвертор знака 2 и первый блок задержки 3, и перемножитель 6, выход которого соединен с выходом устройства, а также второй блок задержки 5, вход которого соединен со вторым входом устройства, и последовательно соединенные второй сумматор 7, первый вход которого соединен с выходом первого блока задержки 3, второй вход - с выходом инвертора знака 2, делитель на два 8 и третий сумматор 9, второй вход которого соединен с выходом второго блока задержки 5, а его выход - со вторым входом перемножителя 6.

Устройство работает следующим образом. На входы ВД поступают отсчеты в конце (I2n-1) и в середине символов (I2n). В решающем устройстве 1 на основе отсчетов в середине символов выносится решение о принимаемом информационном символе (например, для сигналов КАМ256 (см. фиг.1е) решающее устройство содержит 15 компараторов, на вторые входы которых подаются пороговые уровни от -14 до 14 с шагом 2, и логическое устройство, на выходе которого формируется четырехразрядное решение, принимающее значения в диапазоне от -15 до 15 с шагом 2), а на выходе сумматора 4 - решение о величине изменения уровня символов на двух соседних тактовых интервалах. В случае сигналов КАМ256 сигнал на выходе сумматора 4 может принимать значения от -30 до 30 с шагом 2. Если этот сигнал равен нулю, то изменение уровня информационных символов на двух соседних тактовых интервалах отсутствует. Сигнал ошибки с точностью до знака формируется на выходе третьего сумматора 9, в котором осуществляется вычитание из отсчета сигнала в конце символа, задержанного на время 7/2 во втором блоке задержки 5, половины суммы оценок информационных символов на двух соседних тактовых интервалах (второе слагаемое формируется с помощью второго сумматора и делителя на два). Сигнал ошибки на выходе ВД формируется путем перемножения сигналов с выходов первого сумматора 4 и третьего сумматора 9.

Диаграммы, поясняющие работу временного дискриминатора для сигналов КАМ256 при отсутствии помех и при фиксированной ошибке, равной T/4, приведены на фиг.9. Здесь размах сигналов 1-8 уменьшен в 16 раз, а размах сигнала 9 - в 256 раз.

Техническое преимущество заявляемого устройства заключается в том, что оно за счет введения последовательно соединенных второго сумматора, делителя на два и третьего сумматора и другого выполнения решающего устройства позволяет повысить его помехоустойчивость. Докажем это.

Выходной сигнал ВД, при действии на его входе полезного сигнала и шумовой помехи, можно представить в виде суммы u(x)=F(x)+ξ(t,x), где x=Δϕ - ошибка слежения, F(x) - математическое ожидание выходного сигнала, ξ(t,x) - флуктуационная (шумовая) составляющая этого напряжения, зависящая в общем случае от ошибки x.

ВД является цифровьм устройством, сигнал на его выходе квантован по времени и уровню. При этом шумовая составляющая сигнала на выходе дискриминатора является последовательностью двуполярных импульсов со случайными амплитудами. Длительность импульсов равна Т=1/fm, где fm - тактовая частота сигнала. Амплитуды импульсов являются коррелированными случайными величинами со средним значением, равным нулю, и дисперсией σξ2/(x). Спектральная плотность такой последовательности прямоугольных импульсов равна

где N - длительность выборки в тактах, Ri - коэффициент автокорреляции при сдвиге на i тактов.

Шум ξ(t, x) имеет равномерную спектральную плотность в полосе, значительно превышающей полосу пропускания УТС. При этом шум ξ(t, x) можно считать белым и представить его в виде ξ(t,x)=G1/2(0, x)·ξ0(t), где G(0, x) - значение спектральной плотности шума ξ(t, x) на нулевой частоте, ξ0(t) - белый шум с единичной спектральной плотностью. В рассматриваемом случае

Зависимость F(x) от ошибки слежения x называют дискриминационной характеристикой (ДХ) дискриминатора. Зависимость G(0,x) от ошибки слежения x называют флуктуационной характеристикой (ФХ) дискриминатора.

Получение аналитических выражений для ДХ и ФХ представляет собой очень сложную математическую задачу. Поэтому зависимости F(x) и G(0, x) обычно получают методом компьютерного статистического моделирования дискриминаторов.

Полученные этим методом дискриминационные F(y) и нормированные флуктуационные G(0, y)/2T характеристики (y=Δϕ/2π - ошибка, выраженная в долях тактового интервала) временных дискриминаторов УТС при нескольких рабочих значениях отношения сигнал/шум, приходящихся на бит информации q, представлены на фиг.10, 11 для сигналов ФМ4, на фиг.12, 13 - для сигналов КАМ256 (алгоритм (3)) и на фиг.14, 15 - для сигналов КАМ256 (алгоритм (4)). Моделирование проводилось для идеального канала с частотной характеристикой типа приподнятый косинус с коэффициентом округления 0,5.

Временные дискриминаторы УТС когерентных демодуляторов ФМ и КАМ сигналов работают и при наличии расстройки по несущей частоте (см. фиг.10, 12 и 14). На фиг.10 одной из дискриминационных характеристик соответствует расстройка по несущей частоте Δf0≈0,012/T, на фиг.12 и 14 - Δf0≈0,01/T. Однако наличие расстройки по несущей частоте приводит к значительному уменьшению крутизны дискриминационной характеристики и увеличению уровня шума на выходе временного дискриминатора.

Сравнение характеристик временных дискриминаторов с алгоритмами работы (3) и (4) для сигналов КАМ256 показывает, что дискриминационные характеристики в обоих случаях примерно одинаковые, уровень же шума на выходе временного дискриминатора, работающего в соответствии с алгоритмом (4), значительно ниже (при нулевой ошибке - примерно в 4 раза).

При шумовом входном воздействии в виде белого шума со спектральной плотностью G(0,х) дисперсия ошибки слежения в установившемся режиме определяется выражением (см., например [Первачев С.В., Валуев А.А., Чиликин В.М. Статистическая динамика радиотехнических следящих систем. М.: Сов. Радио, 1973, 488 с., ил.]):

где Kξx(ω) - коэффициент передачи замкнутого устройства для шумового воздействия по ошибке слежения, хуст - математическое ожидание ошибки слежения в установившемся режиме, обычно равное нулю.

Выражение (7) можно переписать в следующем виде:

где - эффективная полоса устройства, К3(ω) - коэффициент передачи замкнутого устройства.

Из выражения (8) следует, что при одном и том же значении эффективной полосы помехоустойчивость УТС определяется помехоустойчивостью его временного дискриминатора - отношением квадрата крутизны дискриминационной характеристики к значению флуктуационной характеристики при нулевой ошибке.

Рассчитанные по характеристикам временных дискриминаторов (полученным методом компьютерного статистического моделирования при отношении сигнал/шум, соответствующем вероятности ошибки в бите 10-3 для разных видов модуляции) отношения квадрата крутизны дискриминационной характеристики SДу к значению нормированной флуктуационной характеристики G(0,0)/2T приведены в таблице.

| Таблица | ||||||

| Вид модуляции | ФМ4 | КАМ16 | КАМ32 | КАМ64 | КАМ128 | КАМ256 |

| q, ДБ | 7 | 10,5 | 12,5 | 15,0 | 17,0 | 19,5 |

| SДу | 0,64 | 0,60/0,74 | 0,49/0,57 | 0,46/0,52 | 0,42/0,40 | 0,44/0,46 |

| 54,0 | 31,3/108,3 | 21,0/93,5 | 17,9/76,1 | 15,0/78,4 | 17,1/69,3 | |

| выигрыш, дБ | 0 | 5,4 | 6,5 | 6,3 | 7,2 | 6,1 |

Для КАМ сигналов указаны значения для обоих алгоритмов работы временного дискриминатора (значение для алгоритма (3)/значение для алгоритма (4)). Здесь же приведены значения выигрыша в дБ (201 g (σx для алгоритма(3)/σxдля алгоритма (4))) при одном и том же значении эффективной полосы УТС.

Приведенные выше дискриминационные и флуктуационные характеристики временных дискриминаторов УТС для сигналов КАМ256 и данные таблицы доказывают, что помехоустойчивость заявляемого временного дискриминатора выше, чем помехоустойчивость прототипа.

С другой стороны, при одном и том же значении дисперсии ошибки в УТС использование алгоритма работы временного дискриминатора (4) вместо (3) позволяет в значительной степени расширить полосу захвата устройства и уменьшить длительность переходного процесса, т.е. увеличить его быстродействие.

1. Временной дискриминатор устройства тактовой синхронизации, содержащий последовательно соединенные решающее устройство, вход которого соединен с первым входом устройства, сумматор, второй вход которого соединен с выходом решающего устройства через последовательно соединенные инвертор знака и первый блок задержки, и перемножитель, выход которого соединен с выходом устройства, а также второй блок задержки, соединенный со вторым входом устройства, отличающийся тем, что введены последовательно соединенные второй сумматор, первый вход которого соединен с выходом первого блока задержки, второй вход - с выходом инвертор знака, делитель на два и третий сумматор, второй вход которого соединен с выходом второго блока задержки, а его выход - со вторым входом перемножителя.

2. Временной дискриминатор по п.1, отличающийся тем, что решающее устройство выполнено в виде набора компараторов, первые входы которых соединены с первым входом устройства, а на вторые входы подаются пороговые уровни, и логического устройства, входы которого соединены с выходами компараторов, а его выход - с выходом решающего устройства.