Система дистанционного обучения студентов

Иллюстрации

Показать всеИзобретение относится к вычислительной технике, в частности к системе дистанционного обучения, используемой для обучения студентов. Техническим результатом является повышение быстродействия системы путем исключения поиска данных контрольного теста обучаемых по всему объему базы данных сервера и локализации поиска только по опорным адресам базы данных, соответствующим заданным параметрам контрольного теста. Технический результат достигается тем, что система содержит пять регистров, блок селекции базового адреса теста обучения, блок проверки окончания заданий теста, блок определения корректности ответа обучаемого, блок формирования сигналов считывания теста, блок оценки ответов обучаемого, блок селекции базового адреса контрольного теста, блок селекции адреса временного периода, сумматор, блок сравнения, блок подсчета числа сделок. 10 ил.

Реферат

Изобретение относится к вычислительной технике, в частности к системе дистанционного обучения студентов, основанной на использовании новых информационных технологий в процессе обучения.

Как правило, любой образовательный курс содержит значительный массив теоретического контента, разбитый на так называемые "фреймы", то есть отдельные фрагменты информации по данному курсу, составленные по определенной методике. Кроме того, образовательный курс высшей школы включает также некоторый интерактивный массив в виде тестов и практических задач, которые предлагаются в конце разделов курса.

Исследования Алана Картера и Колстона Сенгера [4] показали, что человек, осваивая какую-то новую дисциплину, чаще всего воспринимает представляемые знания в форме пакетов знаний, иначе идеопластов (от англ. Idea - идея, понятие и [plast]ic - гибкий, пластический).

Идеопласты представляют собою стойкое индивидуальное понятие человека о том или другом фрагменте знания, которое расценивается им как истинное. Каждый идеопласт человек использует как определенную аксиому, "черный ящик", редко вникая в его суть. Так, например, классическим примером идеопластов являются тригонометрические соотношения или другие математические формулы, которые воспринимаются человеком как однозначно истинные, и что сразу могут использоваться на практике. Человеческое мышление может быть условно сведено к комбинированию идеопластов и образованию новых, а потому главная задача любого обучения - дать студенту базовый набор идеопластов и научить его самостоятельно образовывать новые.

Важнейшим элементом при этом предусматривается создание общего формата дистанционного курса, который бы учитывал все особенности дистанционного обучения и индивидуальный подход к каждому студенту. Получить такую модель можно, создав сценарии (стили), которые бы превращали учебные модули к определенному общему виду, имеющему следующую архитектуру:

- схему типа (формы) документа;

- набор документов данного типа;

- письма DSSSL-стилей, которые бы задавали преобразование.

Аналогичную архитектуру предлагает современная, более совершенная относительно возможностей и гибкости архитектура языка XML. Именно данная архитектура и используется как основа при конструировании курсов.

При создании дистанционных курсов каждый фрейм (фреймом будем считать наименьшую часть дистанционного курса, не принимая во внимание аналогичное понятие в языке разметки документов HTML, и которая содержит логически завершенный и легко понятный информационный пакет), в сущности, является документом, который нужно отображать соответственно требованиям пользователя (или аппаратным требованиям его компьютера), превращать соответственно режиму просмотра (как справочник, или же лекцию, или же контрольную работу), отделять из фреймов контрольные вопросы и формировать итоговые контрольные работы.

Для этого можно применять аналогичный подход, создав общую схему документа-фрейма", а потом по ней создать набор сценариев-стилей преобразования, за которыми будет формироваться представление документа и т.п. Упомянутые выше "уровни сложности курса", таким образом, будут формироваться не собственно учителем, а программно.

Такое технологическое решение позволяет учителю сконцентрироваться на разработке собственно курса, а не на чисто технических нюансах. Если продумать структуру курса и записать ее в виде диаграмм UML, то с помощью специальных программных средств (например, Rational Rose) автоматически создается структура сайта дистанционного обучения, а при использовании C++ или Java - готовая модель для программного продукта.

На практике учитель, читая курс, всегда погружается в учебную среду. Интуитивные оценки, которые он делает по ходу работы, помогают ему корректировать процесс обучения в реальном времени.

Дистанционные же курсы обучения не позволяют учителю реализовать подобные действия, поэтому учебную среду для него необходимо создать искусственно с помощью технологических средств.

Действительно, в процессе обучения студент сначала читает материал и старается его понять. Существует простая оценка - чем дольше студент работает над текстом, тем сложнее он его усваивает.

Однако, как отличить тяжесть восприятия от медленного чтения. Для этого используется дополнительная косвенная оценка - поправка на скорость чтения. Ее суть в том, что студенту перед прохождением курса дается простой, желательно, даже очень простой текст (или несколько), в конце которого дается несколько простых, но не тривиальных вопросов, составленных таким образом, чтобы они отображали суть текста.

К вопросам студент может перейти только по нажатию кнопки "завершить". Время, которое прошло от момента открытия текста до нажатия кнопки, - и есть приблизительное время чтения, которое может служить основой для поправки на скорость чтения.

Если студент правильно отвечает на весь вопрос, время записывается. Несколько итераций этого теста дают зависимость скорости чтения от объема текста, и, таким образом, при оценке скорости восприятия студентом той или другой темы можно сделать поправку и точно определить - "тяжело" ему воспринимать текст или он просто медленно читает. Тяжесть восприятия текста - это, кстати, оценка, какую преподаватель обычно делает интуитивно.

После прочтения текста и его более-менее овладения студент переходит к практическому примеру. Этот пример можно оформить как модуль с произвольными параметрами.

Если студент, не просто пролистав пример, выполнил определенный набор типичных задач, а проверил, как изменения параметров влияют на результат, то это и есть первый косвенный сигнал о том, что он интересуется темой и понимает ее.

После практической задачи студент переходит к тесту (условно). В этом тесте может быть два или больше вопросов. Здесь также можно применить некоторые косвенные оценки для определения того вопроса теста, который вызывает наибольшие трудности.

Простейшая такая оценка - оценка времени фокусирования. Студент, читая и решая задачи, тратит определенное время. Чем большее это время, тем большую "тяжесть" соответствующая тема вызывает у студента. Сделав поправку на скорость чтения (см. выше), можно определить, сколько именно времени он фокусировался на решении конкретной задачи.

Таким образом, преподаватель получает не только информацию о правильности или неправильность ответа, но и то, насколько трудным для студента был тот или иной вопрос. И эта оценка в академическом обучении называется интуитивной.

В конце-концов последней из более или менее простых косвенных оценок есть оценка системности работы студента. Она может быть определена из анализа пути прохождения курса. Для этого необходимо немного модифицировать классическую схему разбивки материала и ввести несколько уровней сложности.

Каждый фрейм должен не просто отбивать определенный идеопласт, а быть рассчитаным на определенный уровень восприятия. Эти уровни могут быть определены экспериментально, критерием выступает форма подачи материала.

Известны системы, которые могли бы быть использованы для решения поставленной задачи [1, 2].

Первая из известных систем содержит вычислительный блок, соединенный с блоками ввода функциональных признаков и логической обработки, выходы которых подключены к блоку памяти, блок отображения, подключенный к вычислительному блоку и к блоку принятия решений [1].

Существенный недостаток данного технического решения состоит в его ограниченных функциональных возможностях, обусловленных тем, что описание входных ситуаций при обучении и контроле качества знаний возможно лишь в пространстве ограниченного числа признаков, что приводит к низкой эффективности его использования.

Известна и другая система, содержащая блоки приема данных обучаемого, выходы которых соединены с блоком памяти и с блоком обработки данных, блок селекции временных интервалов, выходы которого подключены к блоку оценки ответов обучаемых, к блоку памяти и к блоку обработки данных, выходы которого соединены с одними входами блока коммутации каналов выдачи данных, другие входы которого соединены с блоком селекции временных интервалов, а выходы являются выходами системы [2].

Последнее из перечисленных выше технических решений наиболее близко к описываемому.

Его недостаток заключается в невысоком быстродействии системы, обусловленном тем, что при запуске контрольного теста обучаемого поиск запрашиваемых данных ведется по всему объему базы данных системы, что приводит к необоснованной потере времени и невозможности реализации режима обучения в реальном масштабе времени.

Цель изобретения - повышение быстродействия системы путем исключения поиска данных контрольного теста обучаемых по всему объему базы данных сервера и локализации поиска только по опорным адресам базы данных, соответствующим заданным параметрам контрольного теста.

Поставленная цель достигается тем, что в систему, содержащую первый регистр, информационный и синхронизирующий входы которого являются первыми информационным и синхронизирующим входами системы соответственно, второй регистр, информационный и синхронизирующий входы которого являются вторыми информационным и синхронизирующим входами системы соответственно, третий регистр, информационный и синхронизирующий входы которого являются третьими информационным и синхронизирующим входами системы соответственно, блок определения корректности ответа обучаемого, один информационный вход которого соединен с выходом второго регистра, другой информационный вход подключен к выходу третьего регистра, синхронизирующий вход соединен со вторым синхронизирующим входом системы, а информационный выход является первым информационным выходом системы, четвертый регистр, информационный и синхронизирующий входы которого являются четвертыми информационным и синхронизирующим входами системы соответственно, блок оценки знаний обучаемого, первый и второй счетные входы которого соединены с первым и вторым счетными выходами блока определения корректности ответа обучаемого соответственно, а информационные выходы являются вторым и третьим информационными выходами системы, пятый регистр, информационный и синхронизирующий входы которого являются пятыми информационным и синхронизирующим входами системы соответственно, и блок формирования сигналов считывания заданий теста, информационный выход которого является адресным выходом системы, а синхронизирующий выход является первым синхронизирующим выходом системы, подключенным к установочному входу блока определения корректности ответа обучаемого, введены блок селекции базового адреса теста обучения, информационный вход которого соединен с выходом первого регистра, синхронизирующий вход подключен к первому синхронизирующему входу системы, один информационный выход соединен с первым информационным входом блока формирования сигналов считывания заданий теста, первый синхронизирующий вход которого подключен к синхронизирующему выходу блока селекции базового адреса теста обучения, блок проверки окончания заданий теста, информационный вход которого соединен с другим информационным выходом блока селекции базового адреса теста обучения, первый синхронизирующий вход подключен к синхронизирующему выходу блока селекции базового адреса теста обучения, второй синхронизирующий вход соединен с первым синхронизирующим выходом блока определения корректности ответа обучаемого, а счетный вход соединен с первым синхронизирующим выходом системы, при этом один выход блока проверки окончания заданий теста подключен к первому счетному входу блока формирования сигналов считывания заданий теста, а другой выход является сигнальным выходом системы, блок селекции базового адреса контрольного теста, информационный вход которого соединен с первым информационным выходом четвертого регистра, а синхронизирующий вход подключен к четвертому синхронизирующему входу системы, блок селекции адреса временного периода, информационный вход которого соединен со вторым информационным выходом четвертого регистра, синхронизирующий вход подключен к синхронизирующему выходу блока селекции базового адреса контрольного теста, а синхронизирующий выход соединен со вторым синхронизирующим входом блока формирования сигналов считывания заданий теста, второй счетный вход которого подключен ко второму синхронизирующему выходу блока определения корректности ответа обучаемого, блок сравнения, один информационный вход которого соединен с выходом пятого регистра, другой информационный вход является шестым информационным входом системы, а синхронизирующий вход подключен к пятому синхронизирующему входу системы, блок подсчета числа сделок, информационный вход которого соединен с одним информационным выходом блока селекции базового адреса контрольного теста, а синхронизирующие входы подключены к соответствующим выходам блока сравнения, при этом информационный выход блока подсчета числа найденных сделок является четвертым информационным выходом системы, один синхронизирующий выход является вторым синхронизирующим выходом системы, а другой соединен с третьим счетным входом блока формирования сигналов считывания заданий теста, и сумматор, один информационный вход которого подключен ко второму информационному выходу блока селекции базового адреса контрольного теста, другой информационный вход соединен с информационным выходом блока селекции адреса временного периода, синхронизирующий вход подключен к синхронизирующему выходу блока селекции адреса временного периода, а выход сумматора соединен со вторым информационным входом блока формирования сигналов считывания заданий теста.

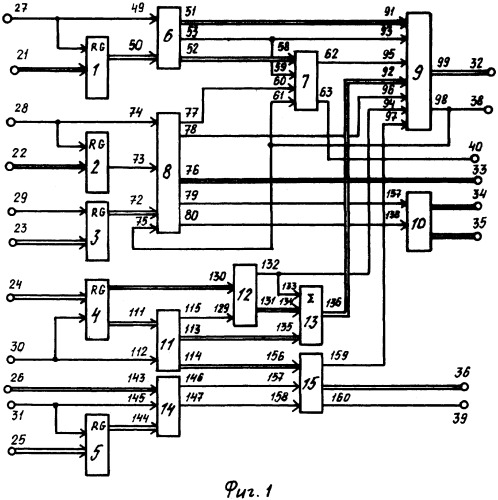

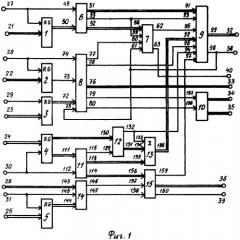

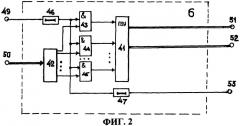

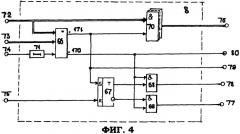

Сущность изобретения поясняется чертежами, где на фиг.1 представлена структурная схема системы, на фиг.2 приведен пример конкретной конструктивной реализации блока селекции базового адреса теста обучения, на фиг.3 приведен пример конкретной конструктивной реализации блока проверки окончания заданий теста, на фиг.4 приведен пример конкретной конструктивной реализации блока проверки корректности ответа обучаемого, на фиг.5 приведен пример конкретной конструктивной реализации блока формирования сигналов считывания заданий теста, на фиг.6 приведен пример конкретной конструктивной реализации блока селекции базового адреса контрольного теста, на фиг.7 приведен пример конкретной конструктивной реализации блока селекции адреса временного периода, на фиг.8 приведен пример конкретной конструктивной реализации блока сравнения, на фиг.9 приведен пример конкретной конструктивной реализации блока подсчета числа сделок, на фиг.10 приведен пример конкретной конструктивной реализации блока оценки ответов обучаемого.

Система (фиг.1) содержит первый 1, второй 2, третий 3, четвертый 4 и пятый 5 регистры, блок 6 селекции базового адреса теста обучения, блок 7 проверки окончания заданий теста, блок 8 определения корректности ответа обучаемого, блок 9 формирования сигналов считывания заданий теста, блок 10 оценки ответов обучаемого, блок 11 селекции базового адреса контрольного теста, блок 12 селекции адреса временного периода, сумматор 13, блок 14 сравнения, блок 15 подсчета числа сделок.

На фиг.1 показаны первый 21, второй 22, третий 23, четвертый 24, пятый 25 и шестой 26 информационные входы системы, первый 27, второй 28, третий 29, четвертый 30 и пятый 31 синхронизирующие входы системы, а также адресный 32 выход системы, первый 33, второй 34, третий 35 и четвертый 36 информационные выходы системы, первый 38 и второй 39 синхронизирующие выходы, и сигнальный 40 выход системы.

Блок 6 селекции базового адреса теста обучения (фиг.2) содержит блок памяти 41, выполненный в виде постоянного запоминающего устройства, дешифратор 42, элементы 43-45 И, элементы 46, 47 задержки. На чертеже показаны синхронизирующий 49 и информационный 50 входы, а также первый 51 и второй 52 информационные и синхронизирующий 53 выходы.

Блок 7 проверки окончания заданий теста (фиг.3) содержит компаратор 55, регистр 56 и счетчик 57. На чертеже показаны информационный 58, первый 59 и второй 60 синхронизирующие входы, счетный 61 вход, а также первый 62 и второй 63 выходы.

Блок 8 определения корректности ответов обучаемого (фиг.4) содержит компаратор 66, триггер 67, элементы 68, 69 И, элементы 70 И группы и элемент 71 задержки. На чертеже также показаны первый 72 и второй 73 информационные входы, синхронизирующий 74 и установочный 75 входы, а также информационный 76 выход, первый 77 и второй 78 синхронизирующие, первый 79 и второй 80 счетные выходы.

Блок 9 формирования сигналов считывания заданий теста (фиг.5) содержит счетчик 81, триггер 82, группы 83-84 элементов И, элементы 85 ИЛИ группы, элементы 86-88 ИЛИ и элементы 89, 90 задержки. На чертеже показаны первый 91 и второй 92 информационные входы, первый 93 и второй 94 синхронизирующие входы, первый 95, второй 96 и третий 97 счетные входы, а также синхронизирующий 98 и информационный 99 выходы.

Блок 11 селекции базового адреса контрольного теста (фиг.6) содержит блок памяти 101, выполненный в виде постоянного запоминающего устройства (ПЗУ), регистры 102 и 103, дешифратор 104, элементы 105-107 И, элементы 108-110 задержки. На чертеже показаны информационный 111 и синхронизирующий 112 входы, первый 113 и второй 114 информационные и синхронизирующий 115 выходы.

Блок 12 селекции адреса временного периода (фиг.7) содержит блок памяти 121, выполненный в виде постоянного запоминающего устройства, регистр 122, дешифратор 123, элементы 124-126 И, элементы 127, 128 задержки. На чертеже показаны синхронизирующий 129 и информационный 130 входы, а также информационный 131 и синхронизирующий 132 выходы.

Блок 14 сравнения (фиг.8) содержит компаратор 141 и элемент 142 задержки. На чертеже показаны первый 143 и второй 144 информационные и синхронизирующий 145 входы, а также выходы 146, 147 блока.

Блок 15 подсчета числа сделок (фиг.9) содержит компаратор 151, счетчики 152, 153, элемент 154 ИЛИ, элемент 155 задержки. На чертеже показаны информационный 156, первый 157 и второй 158 синхронизирующие входы, а также первый 159 и второй 160 синхронизирующие и информационный 161 выходы блока.

Блок 10 оценки ответов обучаемого пользователя (фиг.10) содержит счетчики 139 и 140. На чертеже показаны первый 137 и второй 138 счетные входы, а также первый 34 и второй 35 информационные выходы блока.

Все узлы и элементы системы выполнены на стандартных потенциально-импульсных элементах.

В основу системы дистанционного обучения студентов положены задания для самоконтроля и контроля, реализуемые в этих двух различных режимах работы. Методология построения тестов (т.е. серии тестовых заданий) для самоконтроля и контроля усвоения знаний обучаемых в какой-либо предметной области в целом сходная.

Однако есть и различия. Так, прямое и единственное назначение контрольных тестов - это проверка усвоения знаний по изучаемой дисциплине, в то время как задания для самоконтроля включают в себя и элементы обучения, ибо в этом случае при проведении контроля сообщаются правильные ответы [3].

Исходя из этого, требования к корректности составления контрольных тестов более жесткие, поскольку исследуемый уровень знаний должен быть адекватно отражен некоторыми количественными показателями. Для того чтобы подготовленные тесты действительно позволяли оценить степень усвоения учебного материала, они должны быть составлены в соответствии с определенными требованиями классической теории тестирования [4].

Удаленное автоматизированное рабочее место (АРМ) обучаемого пользователя состоит из терминала, имеющего экран для воспроизведения тестовых заданий, примеры которых приведены в упомянутом источнике [3], и клавиатуру персонального компьютера. Управление предъявлением тестовых заданий в системе дистанционного обучения осуществляется с сервера (на чертеже не показано).

Система работает следующим образом.

В процессе проведения дистанционного обучения студентов на информационный вход 21 системы поступает код идентификатора обучаемого пользователя, который с информационного входа 21 системы заносится в регистр 1 синхронизирующим импульсом, поступающим на синхронизирующий вход 27 системы.

С выхода регистра 1 код идентификатора обучаемого поступает на информационный вход 50 блока 6, откуда он подается на вход дешифратора 42, расшифровывающего код идентификатора и выдающего на один из своих выходов высокий потенциал, поступающий на соответствующие входы элементов 43-45 И.

Для определенности допустим, что высоким потенциалом с первого выхода дешифратора 42 будет открыт элемент 44 И. Синхронизирующий импульс с входа 27 системы через вход 49 блока 6 задерживается элементом 46 на время срабатывания дешифратора 42 и поступает через элемент 44 И на вход фиксированной ячейки постоянного запоминающего устройства (ПЗУ) 41.

В фиксированной ячейке этого блока памяти хранится кодовое сообщение, структура которого в первых К1 разрядах хранит начальный адрес первого тестового задания, а во вторых К2 разрядах хранит общее количество заданий в данном тесте:

| НАЧАЛЬНЫЙ АДРЕС ПЕРВОГО ТЕСТОВОГО ЗАДАНИЯ | ОБЩЕЕ КОЛИЧЕСТВО ЗАДАНИЙ В ДАННОМ ТЕСТЕ |

| (К1 разрядов) | (К2 разрядов) |

Содержимое К1 разрядов фиксированной ячейки ПЗУ 41 считывается на выход 51 блока 6, а содержимое К2 разрядов фиксированной ячейки ПЗУ 41 считывается на выход 52 блока 6.

С выхода 51 блока 6 код начального адреса первого тестового задания через вход 91 блока 9 подается на входы элементов 84 И, открытых по второму входу высоким потенциалом с инверсного выхода триггера 82, находящегося в исходном состоянии. Код начального адреса первого тестового задания проходит через элементы 84 И группы и элементы 85 ИЛИ группы на информационный вход счетчика 81.

Параллельно с этим процессом синхронизирующий импульс с выхода элемента 46 задержки блока 6, задержанный элементом 47 на время считывания содержимого фиксированной ячейки ПЗУ 41, с выхода 53 блока 6 поступает на синхронизирующий вход 93 блока 9 и далее поступает, во-первых, на установочный вход триггера 82, подтверждая или устанавливая его в исходное состояние.

Во-вторых, этот же импульс проходит через элемент 86 ИЛИ, задерживается элементом 89 на время срабатывания триггера 82 и далее поступает на синхронизирующий вход счетчика 81, записывая в него код начального адреса первого тестового задания, которое должно быть предъявлено обучаемому пользователю.

В-третьих, этот же синхронизирующий импульс с выхода элемента 89 походит через элемент 87 ИЛИ, задерживается элементом 90 на время занесения кода начального адреса в счетчик 81 и далее с выхода 98 выдается на выход 38 системы, откуда он поступает на вход первого канала прерывания сервера системы дистанционного обучения.

С приходом этого импульса сервер переходит на подпрограмму опроса содержимого ячейки памяти, адрес которой сформирован на выходе 99 счетчика 81, выдаваемого на адресный выход 32 системы, и выдачи кода первого задания теста обучения на удаленное автоматизированное рабочее место обучаемого пользователя, а кода правильного ответа через вход 23 на информационный вход регистра 3, куда он заносится синхронизирующим импульсом сервера, поступающим через вход 29 системы.

Структура кодограммы, хранящейся в ячейке с начальным адресом первого задания обучающего теста, имеет следующий вид:

| КОД | КОД |

| первого задания теста обучения | правильного ответа на задание теста обучения |

Параллельно с процессом выдачи первого задания теста обучаемому пользователю код общего количества заданий в тесте обучения с выхода 52 блока 6 поступает через вход 58 блока 7 на информационный вход регистра 56 блока 7, в который и заносится синхронизирующим импульсом с выхода 53 блока 6 через вход 59 блока 7.

Кроме того, с выхода 98 блока 9 импульс считывания задания теста обучения через вход 61 блока 7 поступает на счетный вход счетчика 57, фиксируя в счетчике 57 факт выдачи первого задания теста обучаемому пользователю.

Коды с выходов регистра 56 и счетчика 57 подаются на информационные входы компаратора 55, который сравнивает входные коды по сигналу, поступающему на вход 60 блока 7 с выхода 77 блока 8.

После получения первого задания теста обучаемый пользователь на своем автоматизированном рабочем месте обдумывает его, формирует и отправляет ответ, код которого поступает через вход 22 системы на информационный вход регистра 2, куда и заносится синхронизирующим импульсом с входа 28 системы.

Код ответа, сформированного обучаемым, с выхода регистра 2 через вход 73 блока 8 поступает на один информационный вход компаратора 66, на другой информационный вход которого подается код правильного ответа на данное задание теста с выхода регистра 3 через вход 72 блока 8, который также поступает на одни входы элементов 70 И группы.

Синхронизирующий импульс с входа 28 системы через вход 74 блока 8 задерживается элементом 71 на время занесения кода ответа обучаемого в регистр 2 и далее поступает на синхронизирующий вход компаратора 66, который сравнивает код ответа обучаемого и код правильного ответа. Если коды ответов совпали, т.е. обучаемый пользователь правильно ответил на первое задание теста, то на выходе 170 компаратора 66 формируется импульс, который, во-первых, с выхода 80 блока 8 через вход 138 блока 10 поступает на счетный вход счетчика 140, подсчитывающего число правильных ответов на все задания обучающего теста.

Во-вторых, этот же импульс проходит через элемент 69 И, открытый по второму входу высоким потенциалом с инверсного выхода триггера 67, находящегося в исходном состоянии, на выход 77 блока 8 и далее через вход 60 блока 7 на синхронизирующий вход компаратора 55, сравнивающего число заданий в тесте обучения регистра 56 с числом заданий, уже предъявленных обучаемому пользователю в счетчике 57.

Учитывая, что к этому моменту времени обучаемому предъявлено только первое задание, показания регистра 56 будут намного больше показаний счетчика 57, и на выходе 172 компаратора 55 формируется сигнал. Этот сигнал с выхода 62 блока 7 поступает на вход 95 блока 9 и далее проходит через элемент 88 ИЛИ на счетный вход счетчика 81, формируя адрес считывания очередного (следующего) задания теста, который выдается на выход 99 блока 9 и далее на адресный выход 32 системы.

Кроме того, этот же импульс проходит через элемент 87 ИЛИ на вход элемента 90, где задерживается на время срабатывания счетчика 81, и далее через выход 98 блока 9 выдается на выход 38 системы, откуда вновь поступает на вход первого канала прерывания сервера. С приходом этого импульса сервер вновь переходит на подпрограмму опроса содержимого очередной ячейки памяти, адрес которой сформирован на выходе 99 счетчика 81, выдаваемого на адресный выход 32 системы, и выдачи кода следующего задания теста обучения на удаленное автоматизированное рабочее место обучаемого пользователя, а кода правильного ответа через вход 23 на информационный вход регистра 3, куда он заносится синхронизирующим импульсом сервера, поступающим через вход 29 системы.

Если же коды ответов, находящихся в регистрах 2 и 3, не совпали, т.е. обучаемый неправильно ответил на предъявленное ему первое задание, то сигнал появится на выходе 171 компаратора, который, во-первых, через выход 79 блока 8 и вход 137 блока 10 сразу же поступает на счетный вход счетчика 139, фиксирующего число неправильных ответов на все задания теста обучения.

Во-вторых, этот же импульс поступает на вторые входы элементов 70 И группы и переписывает код правильного ответа с выхода регистра 3 через элементы 70 И группы на выход 76 блока 8 и далее через выход 33 системы на автоматизированное рабочее место обучаемого.

В-третьих, этот же импульс поступает на единичный вход триггера 67 и устанавливает его в единичное состояние, при котором триггер 67 открывает по одному входу элемент 68 И, подготавливая цепь прохождения импульса с выхода 170 компаратора через элемент 68 И на выход 78 блока 8.

Получив код правильного ответа после неправильного ответа на задание теста, обучаемый повторяет ввод в регистр 2 теперь уже кода правильного ответа, который заносится в регистр 2 синхронизирующим импульсом с входа 28 системы.

Синхронизирующий импульс с входа 28 системы через вход 74 блока 8 задерживается элементом 71 на время занесения кода ответа обучаемого в регистр 2 и далее поступает на синхронизирующий вход компаратора 66, который сравнивает код ответа обучаемого и код правильного ответа. Поскольку в данном случае коды ответов обязательно совпадут, то на выходе 170 компаратора 66 формируется импульс, который, во-первых, с выхода 80 блока 8 через вход 138 блока 10 поступает на счетный вход счетчика 140, подсчитывающего число правильных ответов на все задания обучающего теста.

Во-вторых, этот же импульс проходит через элемент 68 И, открытый по второму входу высоким потенциалом с прямого выхода триггера 67, находящегося в единичном состоянии, на выход 78 блока 8 и далее через вход 96 блока 9 и через элемент 88 ИЛИ на счетный вход счетчика 81, подготавливая адрес считывания следующего задания теста обучения.

Кроме того, этот же импульс с выхода элемента 88 ИЛИ проходит через элемент 87 ИЛИ на вход элемента 90, где задерживается на время срабатывания счетчика 81, и далее через выход 98 блока 9 выдается на выход 38 системы, откуда вновь поступает на вход первого канала прерывания сервера. С приходом этого импульса сервер вновь переходит на подпрограмму опроса содержимого очередной ячейки памяти, адрес которой сформирован на выходе 99 счетчика 81, выдаваемого на адресный выход 32 системы, и выдачи кода следующего задания теста обучения на удаленное АРМ обучаемого пользователя, а кода правильного ответа через вход 23 на информационный вход регистра 3, куда он заносится синхронизирующим импульсом сервера, поступающим через вход 29 системы.

Описанный процесс обучения пользователя будет продолжаться до тех пор, пока компаратор 55 блока 7 не зафиксирует равенство кодов в регистре 56 и счетчике 57 путем выдачи сигнала на выход 173 компаратора 55 и далее через выход 63 блока 7 на выход 40 системы. По этому сигналу, поступающему на вход второго канала прерывания сервера, сервер переходит на подпрограмму опроса показаний счетчиков 139 и 140 блока 10 с выходов 34 и 35 системы, соответственно, и определения степени готовности обучаемого к выполнению контрольного теста.

Если число неправильных ответов превышает заданный порог, то описанная процедура обучения вновь повторяется до тех пор, пока число неправильных ответов сократится до требуемого уровня, что будет свидетельствовать о готовности обучаемого к выполнению контрольного теста.

В отличие от известных систем описываемая система дистанционного обучения реализует проверку степени подготовленности обучаемых к работе на контрольной базе данных. Контрольный тест предполагает проведение конкретных маркетинговых исследований рынка электронных торгов каждым из обучаемых по различным вопросам. В качестве примера контрольного теста, используемого для проверки готовности обучаемого к реальной работе, рассмотрим тест, в процессе работы по которому обучаемый должен дать ответ на вопрос: по какому товару из заданной группы заключаются сделки с наибольшим объемом торгов.

Для решения этой задачи на своем автоматизированном рабочем месте обучаемый должен сформулировать соответствующий запрос, кодограмма которого имеет следующую структуру:

| КОД ТОВАРА | КОД ГОДА | КОД ЗАДАННОГО ОБЪЕМА СДЕЛОК |

| проведения маркетингового исследования | (порог) в текущем году |

При этом код выбранного товара и цифровое значение кода года с информационного входа 24 системы поступают на информационный вход регистра 4, а код заданного объема сделок с информационного входа 26 системы поступает на вход 143 блока сравнения 14.

Поступление кодограммы запроса с АРМа обучаемого сопровождается синхронизирующим импульсом, поступающим на вход 30 системы и далее на синхронизирующий вход регистра 4, занося в него цифровое значение кода года и код выбранного товара.

Код товара со второго выхода регистра 4 поступает на вход 111 блока 11, откуда он подается на вход дешифратора 104, который расшифровывает код товара, выдавая на один из своих выходов высокий потенциал и открывая тем самым один из элементов 105-107 И.

Тот же синхронизирующий импульс с входа 30 системы поступает на вход 112 блока 11 и далее после задержки элементом 108 на время занесения кода в регистр 4 и время срабатывания дешифратора 104 поступает на опрос состояния элементов 105-107 И.

Учитывая то обстоятельство, что открытым по одному входу будет только один из элементов 105-107 И, то, пройдя соответствующий элемент И, синхроимпульс поступает на вход считывания фиксированной ячейки памяти постоянного запоминающего устройства (ПЗУ) 101, где хранится базовый (начальный) адрес раздела памяти сервера (на чертеже не показан), в котором хранятся все записи о сделках с выбранным товаром.

Структура считываемого кода из фиксированной ячейки памяти ПЗУ 101 имеет следующий вид:

| Код | Код |

| Базового адреса раздела памяти сервера базы данных | Общего числа записей сделок с выбранным товаром |

Код базового адреса раздела памяти по заданному товару и код общего числа записей сделок с выбранным товаром с выходов ПЗУ 101 поступают на информационные входы регистров 102 и 103 соответственно, куда и заносятся синхронизирующим импульсом с выхода элемента 109, задерживающего синхронизирующий импульс с выхода элемента задержки 108 на время считывания кодов из ПЗУ.

Код базового адреса раздела памяти сервера базы данных с выхода регистра 102 через выход 113 блока 11 выдается на вход 135 сумматора 13, а код общего числа записей всех сделок по заданному товару с выхода регистра 103 через выход 114 блока 11 выдается на информационный вход 156 блока 15. Выдача кодов с выходов регистров 102 и 103 разрешается синхроимпульсом с выхода элемента 110, задерживающим синхронизирующий импульс на время срабатывания регистров 102 и 103.

Синхронизирующий импульс с выхода элемента 110 задержки через выход 115 блока 11 поступает на синхронизирующий вход 129 блока 12, на информационный вход 130 которого с первого выхода регистра 4 подан код года, поступающий затем на вход дешифратора 123.

Дешифратор 123 расшифровывает код признака года, выдавая на один из входов элементов 124-126 И высокий потенциал. В результате этого синхронизирующий импульс с входа 129 блока 12, во-первых, проходит соответствующий элемент И, открытый дешифратором 123, на вход считывания фиксированной ячейки памяти ПЗУ 121, из которой считывает опорный адрес года в регистр 122, куда он и заносится синхронизирующим импульсом с входа 129, задержанным элементом 127 на время считывания кода из ПЗУ 121.

С выхода регистра 122 опорный адрес года через выход 131 блока 12 поступает на информационный вход 134 сумматора 13, на другой вход которого подан код базового адреса раздела заданного товара с выхода 113 блока 11.

Параллельно с этим синхронизирующий импульс с выхода элемента 127 блока 12 задерживается элементом 128 на время срабатывания регистра 122 и с выхода 132 поступает как на синхронизирующий вход сумматора 13, так и на синхронизирующий вход 94 блока 9.

По синхронизирующему импульсу сумматор 13 формирует результирующий адрес считывания данных контрольного теста по заданному товару в текущем году из базы данных сервера (базовый адрес страницы текущего года в разделе заданного товара), который с выхода 136 сумматора 13 через вход 92 блока 9 поступает на входы элементов 83 И группы.

Одновременно с этим импульс с входа 94 блока 9 сразу же поступает на единичный вход триггера 82 и устанавливает его в единичное состояние, при котором элементы 83 И группы открываются и код базового адреса страницы текущего года проходит через элементы 85 ИЛИ группы и поступает на информационный вход счетчика 81.

Кроме того, этот же импульс с входа 94 проходит элемент 86 ИЛИ, задерживается элементом 89 на время срабатывания триггера 82, и, во-первых, поступает на синхронизирующий вход счетчика 81, занося в него код базового адреса страницы текущего года в разделе заданного товара.

Во-вторых, тот ж