Система объемной видеозаписи и воспроизведения

Иллюстрации

Показать всеИзобретение относится к аппаратным устройствам телевизионной техники и может быть использовано для формирования и воспроизведения объемных изображений. Техническим результатом является обеспечение объемной видеозаписи трех пространств и воспроизведение изображения трехмерного на трех экранах с восприятием зрителем объемного изображения на каждом. В видеозаписывающую часть системы объемной записи и воспроизведения введены три фотоэлектрических преобразователя, а воспроизводящая часть включает три воспроизводящих канала с плоскопанельным светодиодным экраном в каждом и ИК-передатчиком на его корпусе, 3Д-очки с ИК-приемником на оправе. 1 табл., 18 ил.

Реферат

Изобретение относится к аппаратным устройствам телевизионной техники, может быть использовано для формирования и воспроизведения объемных изображений.

Прототипом принята "Цифровая видеокамера" [1], содержащая один фотоэлектрический преобразователь, являющийся датчиком трех основных цветов R, G, В и включающий первый усилитель и первый пьезодефлектор с отражателем на торце, объектив, второй усилитель и второй пьезодефлектор с отражателем на торце, четыре источника опорных напряжений, блок строчной развертки из задающего генератора и выходного каскада, блок кадровой развертки из элемента И, задающего генератора и суммирующего усилителя, первое и второе дихроичные зеркала, три микрообъектива, три фотоприемника, три предварительных усилителя, три АЦП видеосигнала, последовательно соединенные задающий генератор и синтезатор частот, с первого по четвертый элементы И, накопитель цифровой информации, устройство воспроизведения, включающее задающий генератор, синтезатор частот, ключ, три канала обработки кодов R, G, В, каждый из которых включает последовательно соединенные регистр, блок обработки кодов, первый блок задержек и сумматор и второй блок задержек, включает с 1-го по 6-й блоки импульсных усилителей, блок модуляции излучений, первый усилитель и первый пьезодефлектор с отражателем на торце, второй усилитель и второй пьезодефлектор с отражателем на торце, четыре источника опорных напряжений, блок строчной и кадровой разверток, проекционный объектив и матовый экран. Недостатками прототипа являются: невозможность записи объемного трехмерного пространства и, как следствие, невозможность создания для зрителя условий стереоэффекта при воспроизведении.

Цель изобретения - осуществление объемной видеозаписи трех пространств с получением стереоэффекта при ее воспроизведении.

Техническим результатом являются объемная запись трех пространств /фронтального, правого и левого/, воспроизведение изображения трех пространств на трех экранах с восприятием зрителем объемного изображения на каждом. Результат достигается синхронной видеосъемкой тремя фотоэлектрическими преобразователями, формирующими стереопары изображения фронтального, правого и левого пространств и синхронным воспроизведением изображений трех пространств на трех широкоформатных светодиодных экранах и просмотром изображений на них через 3Д-очки.

Сущность заявляемой системы в том, что в ее видеозаписывающую часть введены три фотоэлектрических преобразователя, геометрическая ось правого и левого фотоэлектрических преобразователя составляет прямую линию, геометрическая ось фронтального фотоэлектрического преобразователя перпендикулярна этой линии и пересекает ее посередине, а воспроизводящая часть включает 3Д-очки с ИК-приемником на оправе, синтезатор частот, три идентичных воспроизводящих канала, каждый из которых включает три канала цветов R, G, B, ключ и триггер, плоскопанельный светодиодный экран /СД-экран/ и, расположенный на его корпусе, ИК-передатчик.

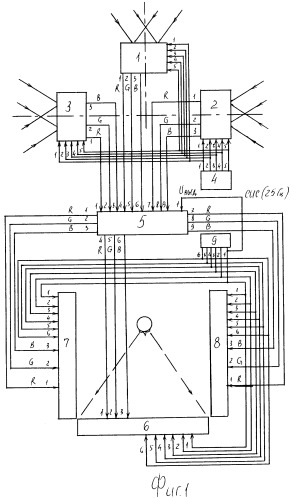

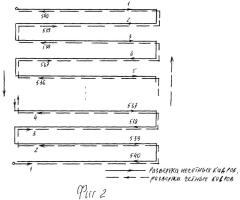

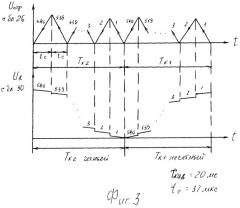

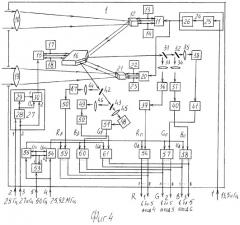

Структурная схема системы на фиг.1, развертка растра на фиг.2, формы управляющих напряжений на фиг.3, фотоэлектрический преобразователь на фиг.4, АЦП видеосигнала на фиг.5, конструкция пьезодефлектора на фиг.6, суммирующий усилитель на фиг.7, воспроизводящий канал на фиг.8, блок удвоения строк на фиг.9, блок удвоения отсчетов на фиг.10, первый блок задержек на фиг.11, накопитель кодов кадра на фиг.12, накопитель кодов нечетного кадра на фиг.13, накопитель кодов четного кадра на фиг.14, блок регистров на фиг.15 и 16, светодиодная ячейка на фиг.17, матрица светодиодов и расположение нейтральных светофильтров на светодиодах на фиг.18.

В видеозаписывающей части каждый фотоэлектрический преобразователь /ФЭП/ воспроизводит видеорежим 960×540×50 Гц: 960 - число кодируемых отсчетов в строке, 540 - число кодируемых строк в кадре, 50 Гц - частота кадров /правых и левых в сумме 25+25/. Частота стереопар 25 Гц, каждая включает правый и левый кадр, следующие поочередно друг за другом. Коды видеосигналов 8-разрядные, что определяет цветопередачу в составе 16777216 оттенков /224/. В каждом ФЭП развертка строк прогрессивная без обратных ходов и по строкам и по кадрам, что выполняется применением для строчной и кадровой разверток пьезодефлекторов со световым отражателем на свободном торце. Тактовая частота в видеозаписывающей части, она же и частота дискретизации кодов видеосигналов:

fД=540×50 Гц × 960=25,92 МГц;

частота строк fс=540×50 Гц=27 кГц, частота колебаний пьезодефлектора строчной развертки .

Длительность строки 37 мкс , длительность кадра 20 мс

Период следования параллельных кодов 38,5 нс .

Коды видеосигналов с частотой дискретизации 25,92 МГц в параллельном виде поступают в накопитель цифровой информации. Фотоэлектрические преобразователи управляющими сигналами обеспечиваются с синтезатора частот. Воспроизводящая часть в составе трех воспроизводящих каналов синхронно воспроизводит три видеорежима 1920×1080×50 Гц на трех плоскопанельных светодиодных экранах с разрешением формата НДТV, в котором 1920 - число отсчетов в строке, 1080 - число строк в кадре, 50 Гц - частота кадров. Частота стереопар 25 Гц. Частота дискретизации в воспроизводящей части . Длительность кадра 20 мс, строчная и кадровая развертки отсутствуют. Разрешение на каждом из трех экранах 2073600 пикселов /1926×1080/. Воспроизводящая часть обеспечивает восприятие зрителями объемного изображения с каждого из трех экранов через 3Д-очки [2 c.558-565], в которых синхронно со сменой кадров правого и левого поочередно перекрывается поле зрения тому из глаз, кадр которого отсутствует на экране. Система объемной видеозаписи и воспроизведения включает /фиг.1/ видеозаписывающую часть, содержащую первый 1 /фронтальный/, второй 2 /правый/ и третий 3 /левый/ фотоэлектрические преобразователи, каждый из которых является датчиком двух изображений одного пространства и формирует три видеосигнала правого кадра RП, GП, BП стереопары и три видеосигнала левого кадра стереопары RЛ, GЛ, BЛ, геометрические оси правого и левого ФЭП составляют одну прямую линию, геометрическая ось фронтального ФЭП перпендикулярна этой линии и пересекает ее посередине, и включает синтезатор 4 частот и накопитель 5 цифровой информации, включает воспроизводящую часть, содержащую первый 6, второй 7 и третий 8 воспроизводящие каналы и синтезатор 9 частот. Фотоэлектрические преобразователи 1, 2, 3 идентичны, каждый включает /фиг.4/ первый /правый/ объектив 10, последовательно соединенные первый усилитель 11 и первый пьезодефлектор 12 с отражателем на торце, расположенный в задней фокальной плоскости объектива 10, первый источник 13 положительного опорного напряжения, второй источник 14 отрицательного опорного напряжения, последовательно соединенные второй усилитель 15 и второй пьезодефлектор 16, передний торец которого имеет две грани, расположенные под соответствующим углом друг к другу и с отражателем на каждой грани, третий источник 17 положительного опорного напряжения, четвертый источник 18 отрицательного опорного напряжения, второй объектив 19 /левый/, последовательно соединенный третий усилитель 20 и третий пьезодефлектор 21 с отражателем на торце, расположенный в задней фокальной плоскости второго объектива 19, пятый источник 22 положительного опорного напряжения, шестой источник 23 отрицательного опорного напряжения, блок 24 строчной развертки из задающего генератора 25 и выходного каскада 26, блок 27 кадровой развертки, включающий последовательно соединенные элемент И 28, задающий генератор 29 и суммирующий усилитель 30, первое 31 и второе 32 дихроичные зеркала, расположенные друг за другом и против первого отражателя пьезодефлектора 16, первый 33, второй 34, третий 35 микрообъективы, первый 36, второй 38, третий 37 фотоприемники, первый 39, второй 41 и третий 40 предварительные усилители, третье 42 и четвертое 43 дихроичные зеркала, расположенные друг за другом и против второго отражателя пьезодефлектора 16, четвертый 44, пятый 45 и шестой 46 микрообъективы, четвертый 47, пятый 48, шестой 49 фотоприемники, четвертый 50, пятый 51, шестой 52 предварительные усилители. Второй объектив 19 расположен слева от объектива 10, оптическая ось его параллельна оптической оси объектива 10, расстояние между осями объективов соответствует оптимальному получению стереоскопического эффекта для зрения человека. Управляющими входами ФЭП являются: первым - вход /13,5 кГц/ блока 24 строчной развертки, вторым - первый вход /25 Гц/ блока кадровой развертки 27, третьим - второй вход /27 кГц/ блока кадровой развертки, четвертый - объединенные сигнальные входы /25,92 МГц/ ключей 54, 55, пятым - вход /50 Гц/ триггера 53. Фотоэлектрический преобразователь 1, 2, 3 включает триггер 53, первый 54 и второй 55 ключи и с первого 56 по шестой 61 АЦП видеосигнала. Управляющие с первого по пятый входы ФЭП 1, 2, 3 подключены к одноименным выходам синтезатора 4 частот /фиг.1/. Информационные выходы 1, 2, 3 ФЭП подключены к информационным входам накопителя 5 цифровой информации соответственно 4, 5, 6, 7, 8, 9, 1, 2, 3. Информационные выходы накопителя 5 цифровой информации подключены: 1, 2, 3 к информационным входам 1, 2, 3 второго 7 воспроизводящего канала, выходы 4, 5, 6 к информационным входам 1, 2, 3 первого 6 воспроизводящего канала, выходы 7, 8, 9 к информационным входам 1, 2, 3 третьего 8 воспроизводящего канала. Одноименные управляющие входы с первого по шестой первого, второго и третьего воспроизводящих каналов 6, 7, 8 объединены и подключены к выходам соответственно с первого по шестой синтезатора 9 частот, первый выход которого подключен и к первому управляющему входу накопителя 5 цифровой информации, Uвыд.

АЦП с 56 по 61 идентичны /фиг.5/, каждый включает последовательно соединенные усилитель 62 и пьезодефлектор 63 с отражателем на торце, источник 64 положительного опорного напряжения, источник 65 отрицательного опорного напряжения, излучатель из импульсного светодиода 66, щелевой диафрагмы 67 и микрообъектива 68, линейку 69 многоэлементного фотоприемника и шифратор 70. Все пьезодефлекторы 12, 16, 21, 63 являются торцевыми биморфными пьезоэлементами со световым отражателем на торце, конструктивно выполнены /фиг.6/ одинаково [3 с.118] из первой 71 и второй 72 пьезопластин, внутреннего электрода 73, первого 74 и второго 75 внешних электродов. Один конец пьезопластин закреплен в держателе 76, на свободном торце расположен световой отражатель 77. Свободный торец пьезодефлектора 16 выполнен из двух граней под углом друг к другу, каждая грань имеет свой отражатель для разведения лучей правого и левого объективов по разным направлениям. Суммирующий усилитель 30 /фиг.7/ включает 11-разрядный счетчик 78 импульсов, дешифратор 79, первый 80 и второй 81 ключи, первый 821 и второй 822 формирователи импульсов и выходной усилитель 83. Первым информационным входом является первый вход выходного усилителя 83, вторым - счетный вход счетчика 78 импульсов, управляющим входом являются объединенные управляющие входы ключей 80, 81 и управляющий вход блока 78. Выходом является выход выходного усилителя 83.

Воспроизводящая часть включает три идентичных 6, 7, 8 воспроизводящих канала, каждый из которых содержит /фиг.8/ канал сигнала R, включающий последовательно соединенные блок 84 удвоения строк, накопитель 85 кодов кадра и блок 86 формирователей импульсов, канал сигнала G, включающий последовательно соединенные блок 87 удвоения строк, накопитель 88 кодов кадра и блок 89 формирователей импульсов, канал сигнала В, включающий последовательно соединенные блок 90 удвоения строк, накопитель 91 кодов кадра и блок 92 формирователей импульсов, содержит последовательно соединенные ключ 94 и триггер 95, светодиодный экран 93 /СД-экран/, ИК-передатчик 96, расположенный на корпусе СД-экрана 93, и включает 3Д-очки 97 с ИК-приемником 98 на их оправе. Первым, вторым и третьим информационными входами воспроизводящего канала 6 /7, 8/ являются 1-8 информационные входы соответственно блоков 84, 87, 90 удвоения строк. С первого по шестой управляющими входами являются: первым - управляющий вход /25 Гц/ ключа 94 и ИК-передатчика 96, вторым - объединенные сигнальный вход ключа 94 /50 Гц/ и вторые управляющие входы блоков 84, 87, 90, третьим - объединенные третьи управляющие входы /54 кГц/ накопителей 85, 88, 91 кодов кадра, четвертым - объединенные четвертые управляющие входы /51,84 МГц/ накопителей 85, 88, 91 кодов кадра и четвертые управляющие входы блоков 84, 87, 90 удвоения строк, пятым - объединенные первые управляющие входы /25,92 МГц/ блоков 84, 87, 90 удвоения строк, шестым - объединенные третьи управляющие входы /27 кГц/ блоков 84, 87, 90 удвоения строк. Выходами канала 6 /7, 8/ являются выходы блоков 86, 89, 92 формирователей импульсов /16588800×3 выходов/, подключенные к соответствующим входам /16588800×3/ СД-экрана 93.

Блоки удвоения строк 84, 87, 90 идентичны /фиг.9/, каждый включает последовательно соединенные блок 99 удвоения отсчетов /в прототипе это блок обработки кодов/, первый блок 100 задержек, сумматор 101, второй блок 102 задержек, информационным входом блока 84 удвоения строк являются 1-8 информационные входы блока 99 удвоения отсчетов. Управляющих входов четыре: первый - управляющий вход /25,92 МГц/ блока 99, подключенный к выходу 5 блока 9, второй - первый управляющий вход /Uк 50 Гц/ первого блока задержек 100, подключенный к выходу 2 блока 9, третий - второй управляющий вход /27 кГц/ первого блока 100 задержек, подключенный к выходу 6 блока 9, четвертый - третий управляющий вход /51,84 МГц/ блока 100, подключенный к четвертому выходу блока 9. Выходами блока 84 /87, 90/ являются 1-8 выходы сумматора 101/540 промежуточных строк/ и 1-8 выходы второго блока 102 задержек /540 текущих строк/. Блок 99 удвоения отсчетов /фиг.10/ производит удвоение отсчетов в каждой строке с 960 до 1920 и содержит триггер 103, первый 104 и второй 105 блоки ключей по 8 ключей в блоке /по числу разрядов в кода/, первый 106, второй 107, третий 108, четвертый 109 регистры, первый 110 и второй 111 блоки элементов задержек по числу разрядов в коде, выполняющие задержку кодов на 38,6 нс, сумматор 112 и 16 диодов. Информационным входом блока 99 являются поразрядно объединенные 1-8 входы блоков 104, 105 ключей, подключенные к соответствующему выходу накопителя 5 цифровой информации /фиг.1/, управляющим входом является вход /25,92 МГц/ триггера 103, подключенный к 5-му выходу блока 9. Выходами блока 99 являются поразрядно объединенные 1-8 выходы блоков 110, 111 и 0-7 выходы сумматора 112. Первый блок 100 задержек /фиг.11/ производит задержку кодов на длительность строки 37 мкс и включает элемент И 113, первый 114 и второй 115 ключи, первый 116 и второй 117 распределители импульсов и восемь регистров 1181-8 по 1920 разрядов каждый. Информационными входами блока 100 являются поразрядно объединенный вторые /информационные/ входы разрядов восьми регистров 118, подключенные к 1-8 выходам блока 99. Управляющими входами являются: первым и вторым - первый и второй входы /50 Гц и 27 кГц/ элементов И 113, подключенные к второму и шестому выходам блока 9, третьим - объединенные сигнальные входы /51,84 МГц/ ключей 114, 115, подключенные к 4 выходу блока 9. Выходом являются поразрядно объединенные выходы разрядов 1-8 регистров 118.

Накопители 85, 88, 91 кодов кадра идентичны, каждый включает /фиг.12/ два накопителя 851 и 852 кодов нечетного кадра и два накопителя 853 и 854 кодов четного кадра, информационными входами блока 85 являются 1-8 входы накопителей 851,2 кодов нечетного кадра и 1-8 входы накопителей 853,4 кодов четного кадра, подключенные соответственно к выходам блоков 101, 102. Управляющих входов четыре: первым являются объединенные первые управляющие входы блоков 851,2, вторым - первые управляющие входы блоков 853,4, третьим - объединенные вторые управляющие входы блоков 851-854, четвертым - объединенные третьи управляющие входы блоков 851-854. Выходы блоков 851 и 853 соответствующим образом объединены и являются первой группой выходов блока 85, выходы блоков 852 и 854 также соответствующим образом объединены и являются второй группой выходов блока 85 кодов кадра. Всего выходов 16588800 /8294400×2/.

Накопители 851 и 852 кодов нечетного кадра идентичны, каждый включает /фиг.13/ с 1-го по 540-й блоки 119 регистров. Информационными входами блока 851 /852/ являются поразрядно объединенные 1-8 входы блоков 1191-540 регистров. Управляющими входами являются: первым - первый управляющий вход первого блока 1191 регистров, вторым - объединенные вторые управляющие входы /Uвыд 54 кГц/ блоков 119 регистров, третьим - объединенные третьи управляющие входы /51,84 МГц/ блоков 1191-540 регистров. Первый управляющий выход каждого предыдущего блока 119 регистров является первым управляющим входом каждого последующего блока 119 регистров. Первый выход последнего блока 119540 регистров подключен параллельно к четвертым управляющим входам всех блоков 119 регистров. Выходами накопителя 851,2 кодов являются выходы всех разрядов восьми регистров всех блоков 1191-540 регистров, 8294400 выходов. Накопители 853 и 854 кодов четного кадра идентичны /фиг.14/ каждый включает с 540-го по 1-й блоки 120 регистров. Информационными входами блока 853,4 являются поразрядно объединенные 1-8 входы блоков 120540-1 регистров. Управляющими входами являются: первым - первый управляющий вход первого блока 120540 регистров, вторым - объединенные вторые - управляющие входы /Uвыд 54 кГц/ блоков 120 регистров, третьим - объединенные третьи управляющие входы /UД 51, 84 МГц/ блоков 120 регистров. Первый управляющий выход каждого предыдущего блока регистров является первым управляющим входом каждого последующего блока 120 регистров. Управляющий выход последнего блока 1201 регистров подключен параллельно к четвертым управляющим входам всех блоков 120540-1 регистров. Выходами накопителя 853 и 854 кодов четного кадра являются выходы всех разрядов восьми регистров всех блоков 120540-1 регистров /8294400 выходов/.

Блоки 119 регистров /и блоки 120 регистров/ идентичны /фиг.15, 16/, каждый включает первый 121 и второй 122 ключи, распределитель 123 импульсов и восемь регистров 1241-8. Информационным входом блока являются поразрядно объединенные третьи /информационные/ входы разрядов восьми регистров 124. Управляющими входами являются: первым - первый управляющий вход первого ключа 121, вторым - сигнальный вход /Uвыд 54 кГц/ второго ключа 122, третьим - сигнальный вход /UД 51,84 МГц/ первого ключа 121, четвертым - управляющий /первый/ вход ключа 122, подключенный к управляющему выходу блока 119540 регистров. Последний /1920-й/ выход распределителя 123 импульсов подключен к второму управляющему входу первого ключа 121 и является управляющим выходом к первому управляющему входу первого ключа 121 в следующем блоке 1192 регистров. Выход первого ключа 121 подключен к входу распределителя 123 импульсов, выходы которого последовательно с первого по 1920-й подключены к первым управляющим входам разрядов параллельно восьми регистров 124. Выход второго ключа 122 подключен параллельно к вторым управляющим входам разрядов восьми регистров 124 и к второму управляющему входу ключа 122, закрывая его после прохода одного импульса выдачи. Выходами блока 119 регистров являются параллельные выходы всех разрядов восьми регистров 1191-8, всего выходов 15360 /1920×8/. При развертке нечетных кадров выдаются коды 1080 строк /540 промежуточных плюс 540 текущих/ накопителями 851 и 852 кодов нечетного кадра. Выходов с блока 851 8294400 /1920×540×8/, выходов с блока 852 столько же 8294400, это коды текущих строк. При развертке четного кадра выдаются коды 1080 строк /540+540/ накопителями 853 и 854 кодов четного кадра. Выходов с каждого блока 853, 854 по 8294400.

Выходы блоков 85, 88, 91 подключены к входам блоков 86, 89, 92 формирователей импульсов, назначение которых выдавать управляющие импульсы /сигналы/ на запитывание светодиодов в СД-ячейках экрана 93. Каждый блок формирователей импульсов включает формирователей импульсов по числу строк 1080 в кадре /на экране/, числу кодов в строке 1920 и разрядов в коде 8, т.е. 16588800.

При развертке нечетного кадра /сверху - вниз/ первая строка кадра вверху экрана, 1080-я строка внизу экрана. При развертке четного кадра /снизу - вверх/ первая строка кадра внизу экрана, а 1080-я строка - вверху. Поэтому для накопления кодов нечетных /правых/ кадров применяются блоки 851 и 852 /фиг.12/, для накопления кодов четных /левых/ кадров применяются блоки 853 и 854. Современные технологии позволяют изготавливать микросхемы с десятками миллионов транзисторов в микросхеме [4 с.65, 5 с.26], следовательно, каждый из блоков 86, 89, 92 формирователей импульсов можно исполнить в одной микросхеме. Амплитуда управляющего сигнала /импульса/ с каждого формирователя импульса соответствует рабочему напряжению применяемых светодиодов, длительность сигнала соответствует длительности 20 мс кадра для непрерывного излучения светодиодами весь период кадра. Плоскопанельный светодиодный экран 93 /СД-экран/ представляет совокупность 2073600 светодиодных ячеек /СД-ячеек/ по числу пикселов в кадре /1920×1080/, отношение сторон экрана 16:9. Каждая СД-ячейка формирует один пиксел изображения и состоит /фиг.17/ из непрозрачного корпуса 125 формой прямоугольного параллелепипеда, матрицы 126 светодиодов трех основных цветов R, G, В и соответствующей формы микролинзы, 127, выполняющей сбор потоков цветных излучений от 24 светодиодов матрицы и формирования из них пиксела требуемого размера и формы. В матрице 24 светодиода: 8 красного цвета излучения, по числу разрядов в коде, 8 зеленого и 8 синего цвета излучения. Матрица расположена в фокальной плоскости микролинзы 127. Светодиоды микроминиатюрного исполнения с диаметром излучающей части 0,4 мм расположены в пять рядов по 5 колонок /фиг.18/. Реакция светодиодов на управляющий сигнал мгновенная /десятки наносекунд/ [6 c.9], время отклика нулевое. Форма матрицы - квадрат со стороной 2,0 мм /0,4 мм × 5/, площадью 4 мм2. Торцовые стороны корпуса СД-ячейки квадраты со стороной 2 мм, глубина корпуса ячейки соответствует фокусному расстоянию микролинзы /несколько миллиметров/. Излучаемые светодиодами цветовые потоки модулируются по яркости преобразованием "код - яркость излучения". Модуляция выполняется применением на каждом светодиоде ослабляющего нейтрального светофильтра, плотность которого соответствует весу разряда в коде, к которому принадлежит светодиод. Кратность ослабления излучения светодиодов осуществляется соответственно коэффициентам двоичных разрядов кода, к которым принадлежат светодиоды. Светодиод первого /старшего/ разряда кода не имеет светофильтра, т.е. его светофильтр плотностью 0х, светодиод второго разряда кода имеет светофильтр плотностью 2х, светодиод третьего разряда кода имеет светофильтр 4х и т.д., светодиод 8-го разряда имеет светофильтр кратностью 128х. Вариант расположения светодиодов в матрице и их светофильтров показан на фиг.18. Распределение коэффициентов двоичных разрядов в коде, соответствующая им плотность нейтральных светофильтров и вес разряда в коде даны в таблице.

| Разряды кода | 1 старший разряд | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| младш. разряд | ||||||||

| Двоичные коэффициенты | 1 | 0,5 | 0,25 | 0,125 | 0,0625 | 0,031 | 0,0156 | 0,0078 |

| Нейтральные светофильтры | 0х | 2х | 4х | 8х | 16х | 32х | 64х | 128х |

| Вес разряда в коде, в % | 50% | 25 | 12,5 | 6,25 | 3,1 | 1,57 | 0,78% | 0,39% |

Излучение 24 светодиодов суммируется микролинзой 127, на выходе которой яркость, насыщенность и цветовой тон результирующего излучения определяются взаимным соотношением составляющих трех цветов сигналов R, G, В. В СД-экране 93 при числе ячеек 2073600 светодиодов одного цвета применяется 16588800 /2073600×8/, а трех цветов применяется 49766400 /16588800×3/. При размере торца корпуса СД-ячейки 2×2 мм размеры каждого из трех экранов 93 составят:

по горизонтали 1920×2 мм = 3840 мм,

по вертикали 1080×2 мм = 2160 мм,

по диагонали 4,4 м или 173 дюйма.

Три фотоэлектрических преобразователя 1, 2, 3 /фиг.1/ выполняют синхронно идентичную работу по формированию изображений трех пространств: первый - фронтального, второй - правого и третий левого. Каждый ФЭП формирует шесть аналоговых видеосигналов двух изображений от правого 10 и левого 19 объективов /фиг.4/, которые с предварительных усилителей 39, 41, 40 поступают на входы АЦП 56, 57, 58, с предварительных усилителей 50, 51, 52 поступают на входы АЦП 59, 61, 60. Поочередная выдача кодов нечетных и четных кадров с АЦП 56-58 и 59-61 выполняется триггером 53 и ключами 54, 55. Синтезатор 4 частот выдает с первого выхода импульсы 13,5 кГц на вход блока 24 в ФЭП 1, 2, 3, со второго выхода - синхроимпульсы стереопар /СИС/ 25 Гц на вторые входы ФЭП, с третьего - строчные синхроимпульсы 27 кГц на третьи входы ФЭП, с четвертого - импульсы дискретизации 25,92 МГц на сигнальные входы ключей 54, 55 /4-й вход ФЭП/, с пятого - импульсы частоты кадров 50 Гц на пятый вход ФЭП /вход триггера 53/. Сигнал с первого выхода триггера 53 открывает ключ 54, пропускающий импульсы 25,92 МГц на тактовые входы АЦП 56-58. Сигнал с второго выхода триггера 53 закрывает ключ 54, открывает ключ 55, пропускающий тактовые импульсы на входы АЦП 59-61. В первый период кадра /и всех нечетных/ АЦП 56-58 преобразуют аналоговые видеосигналы RП, GП, ВП в 8-разрядные коды, которые в параллельном виде поступают на 4, 5, 6 входы накопителя 5 цифровой информации, во втором периоде кадра /и всех четных/ АЦП 59-61 преобразуют аналоговые видеосигналы RЛ, GЛ, BЛ в 8-разрядные коды, поступающие в параллельном виде на те же 4, 5, 6 входы блока 5. Такие же процессы идут в ФЭП 2 и 3, коды R, G, В с которых поступают соответственно на входы 7, 8, 9 и 1, 2, 3. Накопитель 5 цифровой информации включает девять синхронно работающих накопителей с первого по девятый кодов видеоданных, объединенные в один корпус, первичные видеоданные, загружаемые в накопители кодов видеоданных, не подвергаются сжатию, поэтому накопители кодов видеоданных выбираются по параметру скорости записи /и выдачи/ кодов, составляющей 25,92 Мбайт/с. За кадр формируется 518,4 кбайт /960×540/ каждого цвета, за секунду в блок 5 выдается 25,92 Мбайт/с: 518,4×50.

За минуту передается с ФЭП на запись 1,5552 Гбайт/мин /25,92×60 с/, за час передается с ФЭП кодов отдельно каждого цвета 93,312 Гбайт/час /1,5552×60 мин/. Этим требованиям вполне удовлетворяют накопители видеоданных на жестких дисках /винчестеры/, имеющие параметр записи от 30 Мбайт/с и выше [2 с.352, 7 с.47] при емкости до 500 Гбайт [8 c.41]. Таких накопителей для записи отдельно R, G, В с трех ФЭП в блоке 5 должно быть девять /для каждого цвета отдельно/. В качестве интерфейсов могут быть параллельные интерфейсы АТА-6, обеспечивающие передачу данных со скоростью до 100 Мбайт/с [2 с.376]. Объектив 10 /фиг.4/ создает правое изображение в плоскости отражателя пьезодефлектора 12. Отражатель имеет ширину 0,02 мм, длину 10,8 мм /0,02 мм × 540/. Размеры развертывающего элемента 0,02×0,02 мм. По управляющим сигналам /фиг.3/ с усилителя 11 пьезодефлектор 12 производит колебания торца с отражателем относительно первого отражателя пьезодефлектора 16, выполняя сканирование строки правого изображения. Объектив 19 создает левое изображение в плоскости отражателя пьезодефлектора 21. Отражатель его имеет те же размеры и выполняет колебания торца относительно второго отражателя пьезодефлектора 16, выполняя сканирование строки левого изображения. Блок 24 строчной развертки выдает линейно изменяющееся напряжение в виде равнобедренного треугольника. Период управляющего напряжения по длительности равен периоду двух строк. Для растра в 540 отрок при 50 гц пьезодефлекторы 12 и 21 синхронно и синфазно колеблются с частотой 13,5 кГц. За период одного колебания идет развертка двух строк, частота их 27 кГц. Развертка строк прогрессивная без обратных ходов. Пьезодефлектор 16 выполняет кадровую развертку двух кадров: при развертке вниз /фиг.2/ идут нечетные /правые/ кадры, при развертке вверх идут четные /левые/ кадры, пьезодефлектор 16 колеблются с частотой 25 Гц, что составляет 50 кадров в секунду. Кадровая развертка без обратных ходов. Ширина отражателей пьезодефлектора 16 по 0,02 мм, длина каждого 19,2 мм /960×0,02 мм/. С выхода суммирующего усилителя 30 в усилитель 15 поступает линейно изменяющееся и ступенчатое напряжение /фиг.3/, усиливаемое до необходимой величины усилителем 15 [3 с.122]. Суммирующий усилитель 30 /фиг.7/ выполняет суммирование линейного напряжения с задающего генератора 29 с импульсами 27 кГц строк. Каждый импульс строки перемещает строку в конце ее хода на шаг в одну строку, получаются 540 строк: все активные. Назначение блоков 78-82 - подавать на второй вход выходного усилителя 83 в нужное время отрицательные /при развертке вниз/ и положительные /при развертке вверх/ импульсы соответствующей амплитуды и длительности. Сигнал Uo с элемента И 28 обнуляет счетчик 78, который 11-разрядный и производит счет строчных импульсов 27 кГц, цикл счета 1080 импульсов /540×2/. Сигнал Uo открывает ключ 80, закрывает ключ 81. Ключ 80 пропускает 540 строчных импульсов на вход первого формирователя 821 импульсов, выдающего отрицательные импульсы на второй вход выходного усилителя 83. Идет развертка правого кадра стереопары. С приходом 540-го импульса счетчик 78 формирует код числа 540, при котором дешифратор 79 выходным сигналом закрывает ключ 80, открывает ключ 81, пропускающий импульсы строк во второй формирователь 822 импульсов, выдающий положительные импульсы на второй вход блока выходного усилителя 83, следует развертка левого /четного/ кадра стереопары. При поступлении импульса 25 Гц с блока 28 счетчик 78 обнуляется, процесс развертки следующий стереопары повторяется. Отраженные от первого отражателя пьезодефлектора 16 цветные лучи направляются: красного цвета отражаются от первого дихроичного зеркала 31, объективом 33 собираются в фотоприемник 36, синего цвета проходят зеркало 31, отражаются от второго зеркала 32, объективом 34 собираются в фотоприемник 37, зеленого цвета проходят сквозь оба зеркала 31, 32 и объективом 35 собираются в фотоприемник 38. С фотоприемников аналоговые видеосигналы поступают в предварительные усилители. Аналогичный процесс проходят лучи от второго отражателя пьезодефлектора 16. С предварительных усилителей сигналы правого кадра поступают в АЦП 56-58, во втором периоде кадра сигналы левого кадра /второй кадр стереопары/ с предварительных усилителей поступают в АЦП 59-61. АЦП 56-61 имеют один принцип преобразования, заключающийся в развертке луча /фиг.5/ от светодиода 66 отражателем пьезодефлектора 63 по плоскости входных зрачков фотоприемников линейки 69 многоэлементного фотоприемника. Световой импульс преобразуется в электрический сигнал, возбуждающий соответствующую шину шифратора 70. Дискретизация преобразований 25,92 МГц. Источник излучения импульсный светодиод АЛ402А с временем срабатывания 25 нс, что удовлетворяет частоте 25,92 МГц /38,5 нс/. Фотоприемниками в линейке 69 являются лавинные фотодиоды ЛФД с временем срабатывания 10 нс. Время одного преобразования составляет 25+10=35 нс. Линейка 69 включает 255 фотоприемников для кодирования сигналов 8-разрядным кодом. Шифратор из микросхем К155ИВ1 с временем срабатывания 20 нс. Шифратор 70 формирует коды с 00000001 по 11111111. Первому фотоприемнику в линейке соответствует код 00000001, второму - код 00000010, третьему - код 00000011, и т.д., 255-у соответствует код 11111111. Коды АЦП 56-61 в параллельном виде с трех информационных выходов ФЭП 1, 2, 3 поступают соответственно на входы 4, 5, 6, 7, 8, 9, 1, 2, 3 в свои с первого по девятый накопители видеоданных накопителя 5 цифровой информации.

Синтезатор 9 частот воспроизводящей части выдает: с первого выхода импульсы стереопар СИС 25 Гц на первый управляющий вход блока 5 Uвыд /фиг.1/, на управляющие входы ключей 94 /фиг.8/ и ИК-передатчиков 96 в трех воспроизводящих каналах 6, 7, 8 /фиг.1/, с второго - импульсы 50 Гц частоты кадров на сигнальный вход ключа 94 и на вторые - управляющие входы блоков 84, 87, 90 удвоения строк, с третьего - импульсы Uвыд 54 кГц на третьи управляющие входы накопителей 85, 88, 91 кодов, с четвертого - импульсы 51,84 МГц двойной частоты дискретизации на четвертые управляющие входы накопителей 85, 88, 91 кодов и блоков 84, 87, 90 удвоения строк, с пятого - импульсы дискретизации 25,92 МГц на первые управляющие входы блоков 84, 87, 90 удвоения строк, с шестого - синхроимпульсы строк 27 кГц на третьи управляющие входы блоков 84, 87, 90.

При воспроизведении изображения с синтезатора 9 частот на первый управляющий вход накопителя 5 цифровой информации подается сигнал Uвыд СИС /25 Гц/. Так как запись кодов в блоке 5 начинается с первого кадра стереопары /правого/, то и воспроизведение начинается выдачей кодов первого кадра стереопары /правого/, осуществляемое синхроимпульсом СИС стереопары с первого выхода блока синтезатора 9 частот. Коды цветовых сигналов в параллельном виде с информационных выходов блока 5 поступают в воспроизводящие каналы 6, 7, 8 на информационные входы блоков 84, 87, 90 удвоения строк /фиг.8/, на управляющие входы которых и на управляющие входы накопителей 85, 88, 91 кодов и управляющий вход ключа 94 поступают управляющие сигналы с выходов 1-6 блока 9. В блоках 84, 87, 90 коды поступают на входы 1-8 блока 99 удвоения отсчетов. Удвоение отсчетов выполняется /фиг.10/ получением средних /промежуточных/ отсчетов между каждым прошедшим кодом и следующим за ним. Блок выполняет сложение предыдущего и последующего кодов и деление кода суммы на два. Период следования кодов в блок 99 составляет 38,5 нс /25,92 МГц/, на выходе блока 99 составляет 19,3 нс /51,84 МГц/. Каждый код используется дважды: первый раз как последующий, второй раз как предыдущий. Для этого блок 99 имеет четыре регистра 106, 107, 108, 109. Сумматор 112 выполняет сложение двух 8-разрядных кодов за время до 19 нс. При поступлении на вход триггера 103 первого импульса дискретизации 25,92 МГц с его первого выхода сигнал Uвыд1 одновременно выдает "код 0" с регистра 107 в сумматор 112, "код 0" с регистра 108 в блок 111 элементов задержек и через диоды на вторые входы сумматора 112 и открывает ключи в блоке 104, первый код "код 1" поступает в регистры 106, 107. Сумматор 112 выполняет сложение "код 0 + код 0". С приходом второго импульса на вход триггера 103 он же выдает с сумматора 112 код суммы, при этом без затрат времени идет деление на 2. Деление выполняется отбрасыванием из кода суммы младшего разряда, как это делается при делении десятичного числа на десять, выполняется деление соответствующим подключением выходов сумматора 112 к выходам блоков 111 и 110:

| выходы сумматора 112 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| ↓ | ↓ | ↓ | ↓ | ↓ | ↓ | ↓ | ↓ | ↓ | |

| выходы блоков 110, 111 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

Разряд 0 означает разряд переноса при сумме кодов. Процесс сложения в сумматоре занимает 19 нс. В блоках 110 и 111 коды задерживаются на 38 нс, но первая половина времени задержки 19 нс приходится на время сложения, следовательно, после выхода с сумматора 112 кода №1 через 19 нс за ним с блока 111 следует код №2 "код 0". Сигнал Uвыд2 с второго выхода триггера 103 одновременно выдает с регистра 106 "код 1" в блок 110 для задержки его не 38 нс и через диоды в сумматор 112, с регистра 109 "код 0" в сумматор 112 и открывает ключи в блоке 105, "код 2" поступает в регистры 108, 109, а сумматор 112 выполняет сложение, и код №3 с приходом третьего импульса на вход триггера 103 выдается на выход, через 19 нс за ним следует код №4 "код 1". Сигнал Uвыд3 с первого выхода триггера 103 одновременно выдает с регистра 107 "код 1" в сумматор, с регистра 108 "код 2" в блок 111 для задержки и через диоды в сумматор 112 и открывает ключи в блоке 104, регистры 106, 107 заполняются кодом "код 3". Сумматор 112 за 19 нс выполняет сложение "код 1 + код 2". С приходом четвертого импульса на вход триггера 103 код №5