Управляющая эвм

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники и предназначено для обработки данных и программного управления в качестве базового аппаратного средства информационно-управляющих систем (ИУС). Технический результат заключается в расширении функциональных возможностей в части визуализации графической информации, в повышении быстродействия за счет использования микропроцессора с повышенным быстродействием и увеличения объемов оперативной и репрограммируемой памяти. ЭВМ содержит интерфейсы последовательных каналов, системную шину и блок управления, блок взаимодействия, блок обработки данных изображения, блок источников питания и дополнительные каналы связи 8 з.п. ф-лы, 7 ил.

Реферат

Заявляемое техническое решение относится к области вычислительной техники и предназначено для обработки данных и программного управления в качестве базового аппаратного средства информационно-управляющих систем (ИУС), многофункциональных многопроцессорных систем обработки изображений и сигналов, в том числе при реализации задач электронной картографии и взаимодействия.

Техническое решение может найти применение при создании универсального оборудования для обработки данных вообще с визуализацией результатов, в том числе для оборудования, отличающегося сочетанием двух и более вычислительных машин, каждая из которых, по меньшей мере, снабжена процессорным элементом, устройствами ввода/вывода, постоянной и оперативной памятью, позволяющих вести многозадачную обработку данных с воздействием на содержание или порядок расположения обрабатываемых данных; при создании бортовых устройств программного управления для транспортных объектов различного назначения.

Современные требования к повышению эффективности использования аппаратуры управления объектами в различных сферах народного хозяйства предопределяют необходимость разработки и создания отказоустойчивых, гибко реконфигурируемых интегрированных многопроцессорных информационно-управляющих систем, обеспечивающих интеграцию разнородного оборудования в единую интегрированную информационно-управляющую систему на основе использования универсальных аппаратно-программных средств.

Сведения об имеющихся разработках аппаратных средств информационно-управляющих систем находят отражение в описаниях изобретений.

Так, известная микроЭВМ (см. заявку №2000114602/09 на патент РФ на изобретение «Микроэлектронная вычислительная машина» авторов Комарченко П.Я. и Пономарева И.Н., заявл. 2000.06.08, опубл. 2001.04.27, МПК 7 G06F 15/00) с целью повышения производительности и сокращения числа оборудования содержит центральный процессор, устройство ввода-вывода, статическое оперативное запоминающее устройство, устройство ввода, причем центральный процессор включает устройство сопряжения с магистралью, резидентное оперативное запоминающее устройство, устройство синхронизации, микропроцессор, при этом устройство ввода-вывода содержит узел связи, узел селектора адреса, узел логики управления, узел управления приемопередачей, узел приемопередачи.

Признаком, общим с заявляемым техническим решением, является центральный процессор, в состав которого входит микропроцессор и оперативное запоминающее устройство.

Причины, препятствующие достижению требуемого технического результата, заключаются в ограниченных функциональных возможностях, в том числе отсутствии визуализации результатов, долговременного хранения информации, учета времени.

Наиболее близким техническим решением к заявляемому является программируемый логический контроллер (см. описание к патенту РФ №2101757 по заявке №95120422/09 на изобретение «Программируемый логический контроллер» Научно-исследовательского института системных исследований Российской Академии наук (НИИСИ РАН) авторов Бобкова С.Г. и др., МПК 6 G06F 9/00, заявл. 1995.01.10, опубл. 1998.01.10), содержащий для повышения надежности работы микропроцессор, локальную шину, двухпортовое статическое оперативное запоминающее устройство, интерфейсы шин типа VME и ISA, постоянное запоминающее устройство, электрическую программируемую постоянную память, часы реального времени, контроллер клавиатуры, системный контроллер, универсальный программируемый сторожевой таймер, интерфейсы последовательных каналов типа RS-232 и RS-485, периферийную шину, интерфейс субмодулей, буферные усилители адреса и приемники/передатчики данных.

Признаками, общими с заявляемым техническим решением, являются микропроцессор, локальная шина, статическое оперативное запоминающее устройство, постоянное запоминающее устройство, постоянная память, часы реального времени, системный контроллер, интерфейсы последовательных каналов типа RS-232 и RS-485, приемники/передатчики данных.

Причины, препятствующие достижению требуемого технического результата, заключаются в ограниченных функциональных возможностях, в том числе отсутствии визуализации результатов и возможности хранения достаточных объемов информации.

Задача, на решение которой направлено заявляемое техническое решение, заключается в расширении функциональных возможностей в части визуализации графической информации, а также за счет использования микропроцессора с повышенным быстродействием и увеличения объемов оперативной и репрограммируемой памяти.

Технический результат, достигаемый при использовании заявляемого технического решения, заключается в расширении функциональных возможностей в части визуализации графической информации, в повышении быстродействия за счет использования микропроцессора с повышенным быстродействием и увеличения объемов оперативной и репрограммируемой памяти.

Расширение функциональных возможностей управляющей ЭВМ в части визуализации графической информации, повышении быстродействия и увеличении объемов оперативной и репрограммируемой памяти, в свою очередь, позволяет:

- применять управляющую ЭВМ в качестве базового аппаратного средства при построении ИУС различного назначения;

- осуществлять с помощью управляющей ЭВМ вычисления и управление, сбор, хранение, обновление и отображение информации о комплексе управления собственного объекта;

- осуществлять административный контроль и общее управление комплексом управления собственного объекта;

- осуществлять тестовый контроль и самодиагностику;

- выполнять базовые функции бортовой геоинформационной системы;

- осуществлять взаимодействие в составе автоматизированных систем управления (АСУ) многоуровневых сетей управления;

- осуществлять ведение интерактивного диалога с членами экипажа собственного объекта.

Технический результат достигается тем, что в управляющую ЭВМ, содержащую блок управления, состоящий из микропроцессора, локальной шины, оперативного и постоянного запоминающих устройств, часов и системного контроллера, введены блок взаимодействия, блок обработки данных изображения, блок источников питания, системная шина и дополнительные каналы связи, соединенные между собой посредством системной шины, причем блок управления дополнительно содержит контроллер системной шины, шинный формирователь, генераторы тактовой частоты и второе постоянное запоминающее устройство, соединенные между собой посредством локальной шины, блок взаимодействия содержит периферийный узел управления и узел приема и передачи, соединенные между собой посредством локальной шины, узел приема и передачи блока взаимодействия содержит генератор тактовой частоты и приемопередатчики, соединенные между собой посредством локальной шины, при этом блок управления предназначен для решения задач программного управления и обработки информации под управлением операционной системы, а также управления блоками управляющей ЭВМ, взаимодействия и связи с внешними устройствами и внешней отладочной host-ЭВМ, блок взаимодействия предназначен для работы в качестве дополнительного универсального вычислительного устройства с функциями контроллера последовательных интерфейсов, блок обработки данных изображения предназначен для предварительной обработки и вывода видеоданных и графической информации на внешний дисплей, блок источников питания предназначен для использования в качестве многоканального стабилизирующего источника вторичного электропитания.

Технический результат достигается также тем, что блок обработки данных изображения содержит видеоконтроллер, оперативное запоминающее устройство, n аналого-цифровых и n цифроаналоговых преобразователей, n приемников цифрового канала, n передатчиков цифрового канала, где n=1, 2, ..., N, соединенных между собой посредством локальной шины данных, локальной системной шины и моста системной шины.

Технический результат достигается также тем, что блок источников питания содержит узлы включения, защиты, сигнализации и контроля и управления, фильтр входной, измеритель температуры и каналы вторичных источников питания, соединенные между собой и подключенные к системной шине.

Технический результат достигается также тем, что системный контроллер блока управления содержит управляющий контроллер, регистр адреса, контроллер загрузки, дешифратор, контроллер управления памятью, контроллеры последовательных портов, системные таймеры, контроллер взаимодействия с памятью, контроллер канала связи, первичный загрузчик, шину адреса и управления и шину данных, соединенные между собой.

Технический результат достигается также тем, что узел приема и передачи блока взаимодействия дополнительно содержит коммутатор, соединенный входом с выходом управляющего контроллера и входом-выходом с одним из дополнительных каналов связи, соединенным с блоком взаимодействия.

Технический результат достигается также тем, что блок обработки данных изображения содержит видеоконтроллер, оперативное запоминающее устройство, буферное оперативное запоминающее устройство, аналого-цифровой и цифроаналоговый преобразователи и локальную шину данных, соединенные между собой.

Технический результат достигается также тем, что видеоконтроллер блока обработки данных изображения содержит контроллеры системной шины, синхронизации, аналого-цифрового и цифроаналогового преобразователей, оперативного запоминающего устройства, ускоритель графических операций, регистры управления, арбитр шины данных, буферное оперативное запоминающее устройство, соединенные между собой.

Технический результат достигается также тем, что видеоконтроллер блока обработки данных изображения содержит дополнительно контроллер буферного оперативного запоминающего устройства, соединенного первыми входами-выходами с пятыми входами-выходами регистров управления и вторыми - с буферным оперативным запоминающим устройством блока обработки данных изображения.

Технический результат достигается также тем, что периферийный узел управления блока взаимодействия состоит из микропроцессора, оперативного и постоянных запоминающих устройств, часов, системного контроллера, контроллера системной шины, шинного формирователя, локальной шины и генераторов тактовой частоты, соединенные между собой.

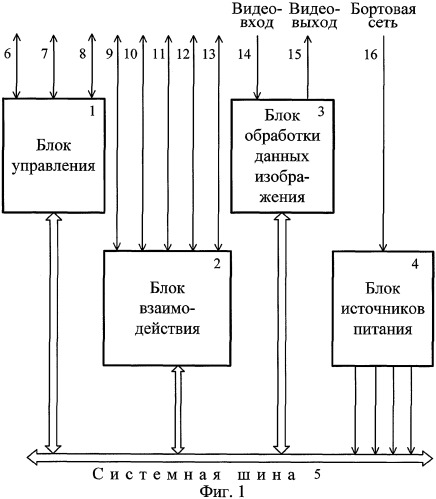

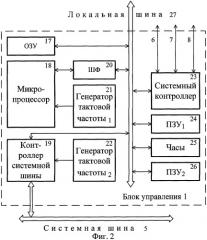

Изобретение поясняется чертежами, где на фиг.1 изображена блок-схема устройства программного управления и обработки данных, фиг.2 - блок-схема блока управления, на фиг.3 и 3.1 - варианты блок-схемы блока взаимодействия, на фиг.4 и 4.1 - варианты блок-схемы блока обработки данных изображения, на фиг.5 - схема блока источников питания, фиг.6 - структурная схема системного контроллера блока управления, фиг.7 - структурная схема видеоконтроллера блока обработки данных изображения.

Пример реализации заявляемого технического решения приведен для случая использования его в качестве базового средства ИУС.

Для достижения заявленного технического результата управляющая ЭВМ может состоять, например, из блока управления 1 (см. фиг.1), блока взаимодействия 2, блока обработки данных изображения 3 и блока источников питания 4, соединенных между собой посредством системной шины 5, интерфейсов последовательных каналов 6 и 7 и дополнительных каналов связи 8, 9, 10, 11, 12, 13, 14, 15 и 16, причем, интерфейсы последовательных каналов 6 и 7 могут быть типа RS-232, RS-422 и RS-485, каналы 8 и 13 - специализированных технологических, 11 и 12 - аналогичными 6 и 7 соответственно, 14 - использоваться в качестве видеовхода, 15 - в качестве видеовыхода, а 16 - являться входом электропитания от бортовой сети.

Блок управления 1 может содержать, например, (см. фиг.2) оперативное запоминающее устройство (ОЗУ) 17, микропроцессор 18, контроллер системной шины 19, шинный формирователь 20, первый 21 и второй 22 генераторы тактовой частоты, системный контроллер 23, первое постоянное запоминающее устройство (ПЗУ) 24, часы 25, второе ПЗУ 26, локальную шину 27.

Блок взаимодействия 2 может содержать, например, (см. фиг.3) узел приема и передачи 28, периферийный узел управления 29 и локальную шину 30, причем узел приема и передачи 28 может состоять, например, из генератора тактовой частоты 31, приемопередатчиков 32, управляющего контроллера 33 и контроллера загрузки 34.

В то же время узел приема и передачи 28 блока взаимодействия 2 может состоять, например, (см. фиг.3.1) из генератора тактовой частоты 31, приемопередатчиков 32, управляющего контроллера 33, контроллера загрузки 34 и коммутатора 35.

Периферийный узел управления 29 можно выполнить аналогичным блоку управления 1.

Блок обработки данных изображения 3 может содержать, к примеру, (см. фиг.4) n аналого-цифровых преобразователей 36.1, ..., 36.n (n=1, 2, ..., N), видеоконтроллер 37, n цифроаналоговых преобразователей 38.1, ..., 38.n (n=1, 2, ..., N), локальную шину данных 39, ОЗУ 40, локальную системную шину 41, n приемников цифрового канала 42.1, ..., 42.n (n=1, 2, ..., N), n передатчиков цифрового канала 43.1, ..., 3.n (n=1, 2, ..., N), мост системной шины 44.

Блок обработки данных изображения 3 может содержать в частном случае, например, (см. фиг.4.1) аналого-цифровой преобразователь (АЦП) 36, видеоконтроллер 37, цифроаналоговый преобразователь (ЦАП) 38, локальную шину данных 39, ОЗУ 40 и буферное ОЗУ (БОЗУ) 45.

Схема блока источников питания 4 может содержать, например, (см. фиг.5) узел защиты 48, фильтр входной 49, измеритель температуры 50, узел сигнализации 51, узел включения 52, узел контроля и управления 53, канал вторичного источника питания (ВИП) «+3,3 В» 54, канал ВИП «+5,0 В» 55, канал ВИП «+12.0 В» 56, канал ВИП «-12,0 В» 57.

Структурная схема системного контроллера 23 блока управления 1 может содержать, например, (см. фиг.6) управляющий контроллер 58, включающий в себя функции системного контроллера прерываний, контроллера взаимодействия с микропроцессором 18 и контроллером системной шины 19, а также функции управления режимами DMA (режимами доступа к ОЗУ 17 от контроллера системной шины без участия микропроцессора 18), регистр адреса 59, контроллер загрузки 60, дешифратор 61, контроллер управления памятью (ОЗУ 17) 62, контроллер последовательных портов RS-232-63 и 64, контроллер последовательного порта RS-422/485-65, системный таймер, состоящий, в общем случае, из n таймеров с T.1 66 до Т.n 67, контроллер взаимодействия с памятью 68, т.е. с ПЗУ 24, контроллер канала связи, например, технологического 69, первичный загрузчик 70, шину адреса и управления 71 и шину данных 72.

Структурная схема видеоконтроллера 37 блока обработки данных изображения 3 может содержать, например, (см. фиг.7) контроллер системной шины 73, БОЗУ 74, арбитр шины данных 75, контроллер АЦП 76, регистры управления 77, ускоритель графических операций 78, контроллер синхронизации 79, контроллер ОЗУ 80, контроллер БОЗУ 81, контроллер ЦАП 82.

Блок управления 1 (см. фиг.1), блок обработки изображения данных 2, блок взаимодействия 3 и блок источников питания 4 соединены между собой посредством системной шины 5.

Интерфейсы последовательных каналов RS-422/485 и RS-232 6 и 7 соответственно и канал связи 8 соединены с входами-выходами блока управления 1. Каналы связи 9, 10, 11, 12 и 13 соединены с входами-выходами блока взаимодействия 2. Каналы видеовхода 14 и видеовыхода 15 соединены с входом и выходом блока данных изображения 3.

Вход электропитания бортовой сети 16 соединен с входом блока источника питания 4.

ОЗУ 17 (см. фиг.2) блока управления 1 соединено входами-выходами с локальной шиной 27. Микропроцессор 18 соединен своими входами-выходами с первыми входами-выходами шинного формирователя 20 и входом с выходом первого генератора тактовой частоты 21. Контроллер системной шины 19 соединен своими входами-выходами с системной шиной 5, входом с выходом второго генератора тактовой частоты 22 и входами-выходами с локальной шиной 27. Шинный формирователь 20 соединен своими входами-выходами с локальной шиной 27. Системный контроллер 23 соединен своим первыми входами-выходами с локальной шиной 27, вторыми с интерфейсом последовательного канала RS-422/485 6, третьими с интерфейсом последовательного канала RS-232 7 и четвертыми с технологическим каналом 8. Первое и второе ПЗУ 24 и 26 соответственно и часы 25 соединены входами-выходами с локальной шиной 27.

Блок взаимодействия 2 состоит из узла приема и передачи 28 и периферийного узла управления 29, соединенных между собой посредством локальной шины 30 (см. фиг.3 и фиг.3.1).

Узел приема и передачи 28 содержит генератор тактовой частоты 31 (см. фиг.3) и приемопередатчики 32, соединенные своими входами-выходами с первыми и вторыми входами-выходами управляющего контроллера 33 соответственно, соединенного третьими и четвертыми входами-выходами с локальной шиной 30 и первыми входами-выходами контроллера загрузки 34 соответственно, вторые входы-выходы которого соединены с локальной шиной 30. Вторые входы-выходы приемопередатчиков 32 соединены с каналом связи 9. Первые входы-выходы периферийного узла управления 29 соединены с локальной шиной 30, а вторые - с системной шиной 5. Третий, четвертый и пятый входы-выходы периферийного узла управления 29 соединены с каналами связи 11, 12 и 13 соответственно.

Узел приема и передачи 28, представленный на фиг.3.1, помимо указанных на фиг.3, содержит коммутатор 35, соединенный входом с выходом управляющего контроллера 33. Вход-выход коммутатора 35 соединен с каналом связи 10. Взаимосвязи остальных узлов аналогичны представленным на фиг.3.

В блоке обработки данных изображения 3 (см. фиг.4) АЦП 36.1, ..., 36.n своими входами соединены с видеовходом 14, а выходами с входами видеоконтроллера 37. Выходы видеоконтроллера 37 соединены со входами ЦАП 38.1, ..., 38.n, выходы которых соединены с видеовыходом 15. Видеоконтроллер 37 соединен первыми входами-выходами посредством локальной шины данных 39 с ОЗУ 40 и вторыми с локальной системной шиной 41. Входы видеоконтроллера 37 соединены с выходами приемников цифрового канала 42.1, ..., 42.n, которые также соединены с выходами соответствующих им АЦП 36.1, ..., 36.n. Выходы видеоконтроллера 37 соединены со входами передатчиков цифрового канала 43.1, ..., 43.n, которые также соединены со входами соответствующих им ЦАП 38.1, ..., 38.n. Локальная системная шина 41 соединена с мостом системной шины 44, соединенным с системной шиной 5.

Блок обработки данных изображения 3 (см. фиг.4.1) содержит АЦП 36, соединенный входом с видеовходом 14 управляющей ЭВМ, а выходом с первым входом видеоконтроллера 37. Там же ЦАП 38 соединен выходом с видеовыходом 15, а входом с выходом БОЗУ 45, первые входы-выходы которого соединены со вторыми входами-выходами видеоконтроллера 37, пятые входы-выходы которого соединены с системной шиной 5, третьи - с первыми входами-выходами ОЗУ 40 посредством локальной шины данных 39 и четвертые - со вторыми входами-выходами ОЗУ 40 непосредственно. Вторые входы-выходы БОЗУ 45 соединены с локальной шиной данных 39.

В схеме блока источников питания 4 (см. фиг.5) вход узла защиты 48 соединен с каналом бортовой сети 16, а выходом со входом фильтра входного 49. Измеритель температуры 50 и узел сигнализации 51 соединены с узлом включения 52 через узел контроля и управления 53, причем второй вход узла включения 52 соединен с первым выходом узла контроля и управления 53, второй выход которого соединен со входом узла сигнализации 51, выход измерителя температуры 50 соединен со вторым входом узла контроля и управления 53, на третий вход которого поступает сигнал (дистанционного) включения по каналу бортовой сети 16. Выход узла включения 52 соединен со входами каналов ВИП 54, 55, 56 и 57, выходы которых соединены с четвертым входом узла контроля и управления 53 и являются выходами блока источников питания 4 (см. фиг.1), подключенных к каналам питания системной шины 5. Выход входного фильтра 49 соединен с первыми входами узлов включения 53 и контроля и управления 53.

Управляющий контроллер 58 (см. фиг.6) системного контроллера 23 блока управления 1 соединен своими первыми входами-выходами с первыми входами-выходами регистра адреса 59, контроллера загрузки 60, дешифратора 61, контроллера управления памятью 62, контроллеров последовательных портов 63, 64 и 65, системных таймеров 66 и 67, контроллера взаимодействия с памятью 68, контроллера канала связи 69 и первичного загрузчика 70 посредством шины адреса и управления 71. Шина данных 72 соединена со вторыми входами-выходами управляющего контроллера 58, регистра адреса 59, контроллера загрузки 60, контроллеров последовательных портов 63, 64 и 65, системных таймеров 66 и 67, контроллера взаимодействия с памятью 68, контроллера канала связи 69, а также с выходом первичного загрузчика 70. Третьи входы-выходы контроллеров последовательных портов 63, 64 и 65 и контроллера канала связи 69 соединены с интерфейсами последовательных каналов 7 и 6 и канала связи 8 соответственно. Третий вход-выход управляющего контроллера 58 соединен посредством локальной шины 27 (см. фиг.2) с микропроцессором 18 и контроллером системной шины 19 и предназначен для обмена сигналами управления, а выход - с микропроцессором 18 (также посредством локальной шины 27) и предназначен для сигналов прерываний. Выходы дешифратора 61 предназначены для передачи сигналов выбора адресов внешних устройств посредством локальной шины 27. Выход контроллера управления памятью 62 предназначен для сигналов управления, направляемых в ОЗУ 17 посредством локальной шины 27. Выход контроллера загрузки 60 предназначен для передачи сигналов загрузки внешних устройств посредством локальной шины 27. Вторые входы-выходы регистра адреса 59, соединенные с шиной данных 72, предназначены для передачи сигналов на мультиплексированную шину также посредством локальной шины 27.

Контроллер системной шины 73 видеоконтроллера 37 своими первыми входами-выходами соединен с системной шиной 5 (см. фиг.7), вторыми - с входами-выходами БОЗУ74, выход которого соединен со входом арбитра шины данных 75, группа входов которого соединена с группой выходов контроллера АЦП 76. Третьи входы-выходы контроллера системной шины 73 соединены с входами-выходами регистров управления 77, первый выход которого соединен с входом БОЗУ 74, второй - со входом контроллера АЦП 76. Ускоритель графических операций 78 входами-выходами соединен с первыми входами-выходами арбитра шины данных 75. Третий выход регистров управления 77 соединен со входом контроллера синхронизации 79. Вторые входы-выходы арбитра шины данных 75 соединены с первыми входами-выходами контроллера ОЗУ 80, вторые входы-выходы которого соединены с локальной шиной данных 41. Четвертый и пятый выходы регистров управления 77 соединены со входами контроллера БОЗУ 81 и контроллера ЦАП 82 соответственно. Входы-выходы контроллера ЦАП 82 соединены с ЦАП 38 (см. фиг.4.1). Входы-выходы контроллера БОЗУ 81 соединены с БОЗУ 39 (см. фиг.4). Третьи входы-выходы контроллера ОЗУ 80 соединены с ОЗУ 40 (см. фиг.4 и 4.1).

При использовании заявляемого технического решения в качестве базового средства ИУС оно может быть предназначено для решения, например, следующих задач:

- управления в реальном масштабе времени, в том числе осуществления вычислений и управления сбора, хранения, обновления и отображения информации о комплексе управления собственного объекта;

- административного контроля и общего управления комплексом управления собственного объекта;

- тестового контроля и самодиагностики;

- выполнения базовых функций бортовой геоинформационной системы;

- взаимодействия в составе многоуровневых сетей управления;

- ведения интерактивного диалога в собственной локальной сети (с членами экипажа собственного объекта).

Блок управления 1 (см. фиг.2) может быть предназначен для решения задач управления и обработки информации как в качестве системного, так и периферийного устройства и позволяет обеспечить выполнение задач процедурной обработки данных под управлением программ, записанных в ПЗУ 24 и 26, поддержки функционирования операционной системы, управления блоками управляющей ЭВМ, поддержки взаимодействия с внешними устройствами, поддержки связи с внешней отладочной host-ПЭВМ и записи в ПЗУ 24 и 26 программ и данных, требующих долгосрочного хранения.

Назначение узлов блока управления 1 может быть следующим (см. фиг.2).

Системная шина 5 (например, CompactPCI PICMG 2.0 R 3.0 или РС/104-Plus "PCI-Only" Version 1.1) предназначена для взаимодействия с периферийными блоками и узлами управляющей ЭВМ.

Интерфейсы последовательных каналов 6 и 7 предназначены для связи с внешними устройствами по, например, последовательному каналу RS-422/485 и двум RS-232 соответственно.

Канал связи 8 предназначен для поддержки связи с отладочной host-ПЭВМ.

ОЗУ 17 предназначено для хранения программ и различных данных, используемых микропроцессором 18, и может быть выполнено как динамическое оперативное запоминающее устройство, так и синхронное динамическое запоминающее устройство.

Микропроцессор 18 предназначен для выполнения различных вычислительных операций под управлением программного обеспечения.

Контроллер системной шины 19 предназначен для обеспечения интерфейса с системной шиной 5 и устройствами на ней.

Шинный формирователь 20 предназначен для электрической развязки шины микропроцессора 18 и локальной шины 27 блока управления 1 для возможности отключения микропроцессора 18 от локальной шины 27, например, при DMA обменах (прямом доступе к памяти посредством пересылки данных между ОЗУ 17 и периферийными устройствами без участия микропроцессора 18).

Генераторы тактовой частоты 21 и 22 предназначены для генерации тактовой частоты (серии прямоугольных импульсов, меандра) заданного номинала, стабильности и скважности с целью синхронизации всех операций, осуществляемых микропроцессором 18 и контроллером системной шины 19 соответственно.

Системный контроллер 23 предназначен для выработки сигналов управления различным устройствам блока управления 1, реализации различных интерфейсов и системных функций.

Первое ПЗУ 24 предназначено для постоянного (энергонезависимого) хранения пользовательских программ и данных.

Часы 25 предназначены для отсчета реального времени.

ПЗУ2 26 предназначено для постоянного (энергонезависимого) хранения системного программного обеспечения (ПО) и различных программ.

Локальная шина 27 предназначена для поддержки обмена данными между узлами блока управления 1 и является мультиплексированной процессорной шиной.

Блок взаимодействия 2 (см. фиг.3 и фиг.3.1) может быть предназначен для работы в качестве дополнительного универсального вычислительного устройства с функциями конфигурации контроллера в ИУС на базе системной шины, например, CompactPCI или PC/104-Plus «PCI-Only» Version 1.1 с выполнением организации взаимодействия, например, по цифровому каналу с внешними устройствами, например с радиостанцией или абонентами последовательного мультиплексного канала, и обеспечения функционирования операционной системы.

Назначение узлов блока взаимодействия 2 для связи с внешними объектами по мультиплексированной процессорной шине может быть следующим (см. фиг.3).

Назначение каналов связи 11, 12 и 13 аналогично назначению интерфейсов последовательных каналов 6 и 7 и каналу 8.

Узел приема и передачи 28 предназначен непосредственно для организации взаимодействия с внешними объектами управления под управлением периферийного узла управления 29.

Периферийный узел управления 29 предназначен для решения задач управления и обработки информации в качестве периферийного устройства на базе системной шины, например CompactPCI и PC/104-Plus «PCI-Only» Version 1.1, и позволяет обеспечить выполнение задач процедурной обработки данных под управлением программ, записанных в репрограммируемом постоянном запоминающем устройстве, поддержки функционирования операционной системы, управления блоками, поддержки взаимодействия с внешними устройствами по каналам связи 9, 10, 11, 12 и 13 (например, RS-232, RS-422, RS-485, полнодуплексному технологическому каналу), поддержки связи с внешней отладочной инструментальной host-ПЭВМ и записи в репрограммируемое постоянное запоминающее устройство программ и данных, требующих долгосрочного хранения. Состав и назначение внутренних блоков периферийного узла управления 29 могут быть аналогичны составу и назначению узлов блока управления 1. Подключение узла приема и передачи 28 к периферийному узлу управления 29 может осуществляться по шине 30 (см. фиг.3), аналогичной локальной шине 27 блока управления 1 (см. фиг.2).

Генератор тактовой частоты 31 предназначен для генерации тактовой частоты (серии прямоугольных импульсов, меандра) заданного номинала, стабильности и скважности с целью синхронизации всех операций, осуществляемых управляющим контроллером 33.

Приемопередатчики 32 предназначены для реализации физического уровня взаимодействия и обеспечения гальванической развязки с внутренними цепями управляющей ЭВМ.

Контроллер 33 предназначен для обмена данными с внешними объектами управления по каналу связи 9 под программным управлением периферийного узла управления 29.

Контроллер загрузки 34 предназначен для программной загрузки конфигурации контроллера 33 непосредственно от периферийного узла управления 29.

Коммутатор 35 (см. фиг.3.1) предназначен, например, для включения и выключения аппаратуры спутниковой навигации или другого зависимого устройства, которым можно управлять программно. Коммутатор 35 может также обеспечивать гальваническую развязку канала 10 и внутренних цепей управляющей ЭВМ.

Назначение остальных узлов блока взаимодействия 2, приведенных на фиг.3.1, аналогично назначению узлов, приведенных на фиг.3.

Блок обработки данных изображения 3 (см. фиг.4 и фиг.4.1) может быть предназначен для предварительной обработки видеоданных и вывода видеоданных и графической информации на внешний дисплей, переключения начального адреса вывода видеоизображения из видеопамяти, что может позволить использовать двойную (или более) буферизацию при выводе видеоизображения на экран, формирования нескольких окон видеоизображения с осуществлением переключения между ними (видимое окно) с помощью регистра адреса активного окна.

Назначение узлов блока обработки данных изображения 3 может быть следующим (см. фиг.4 и фиг.4.1).

АЦП 36 предназначен для преобразования входного аналогового видеосигнала (например, в соответствии со стандартом ГОСТ 7845 или ГОСТ 28406, вариантом интерфейса V(А)) в цифровой формат (например, YUV 422 в соответствии со стандартом ITU-R BT.656). В общем случае аналоговых входов может быть n, причем n=1, ..., N, и АЦП соответственно также n (36.1, ..., 36.n).

Видеоконтроллер 37 предназначен для взаимодействия с блоком управления 1 по системной шине 5, в том числе через локальную системную шину и мост системной шины 44 (см. фиг.4), ввода видеоинформации в цифровом формате (например, YUV 422 в соответствии со стандартом ITU-R BT.656), вывода видеоинформации в цифровом или аналоговом формате (например, в соответствии с ГОСТ 28406, вариант интерфейса V(А)), организации работы с ОЗУ 40, выполнения операций, связанных с обработкой видеоинформации, получаемой по системной шине 5 или от внешних источников, выполнения операций прорисовки графических примитивов (например, построение точки, линии, треугольника, полигона, эллипса и т.д.), формирования синхронизации основных узлов блока обработки данных изображения 3.

ЦАП 38 предназначен для преобразования видеосигнала, получаемого от видеоконтроллера 37 в цифровом формате, в аналоговый вид (например, в соответствии со стандартом ГОСТ 7845 или ГОСТ 28406, вариант интерфейса V(A)). В общем случае аналоговых выходов может быть n, причем n=1, 2, ..., N, и соответственно ЦАП также может быть n (38.1, ..., 38.n). ЦАП 38 может также входить в состав видеоконтроллера 37.

Локальная шина данных 39 предназначена для обеспечения обмена данными между узлами блока обработки данных изображения 3.

ОЗУ 40 предназначено для временного хранения видеоданных.

Локальная системная шина 41 предназначена для обеспечения взаимодействия между видеоконтроллером 37, периферийными устройствами, которые могут быть подключены дополнительно к локальной системной шине 41 и мостом системной шины 44.

Приемники цифрового канала 42.1, ..., 42.n (n=0, 1, 2, ..., N) предназначены для приема видеоданных по каналу 14 в цифровом формате (например, по каналу LVDS в соответствии со стандартом ANSI/TIA/EIA-644).

Передатчики цифрового канала 43.1, ..., 43.n (n=0, 1, 2, ..., N) предназначены для передачи видеоданных в цифровом формате (например, по каналу LVDS в соответствии со стандартом ANSI/TIA/EIA-644).

Мост системной шины 44 предназначен для «расширения» системной шины 5, организации локальной системной шины 41 и обеспечения взаимодействия между видеоконтроллером 37, периферийными устройствами, которые могут быть подключены дополнительно к локальной системной шине 41 блоком управления 1 по системной шине 5. В общем случае мост системной шины 44 может отсутствовать, и видеоконтроллер 37 в этом случае может быть подключен непосредственно к системной шине 5.

БОЗУ 45 предназначено для буферизации входных и выходных видеоданных.

Блок источников питания (БИП) 4 (см. фиг.5) может быть предназначен для использования в системе электропитания (СЭП) объекта эксплуатации в качестве многоканального стабилизирующего источника вторичного электропитания.

Назначение узлов блока источников питания 4 (см. фиг.5) может быть следующим).

Узел защиты 48 предназначен для защиты внутренних цепей БИП 4 при неправильной полярности входного напряжения, ограничения уровня импульсных помех и пульсаций напряжения бортовой (первичной) сети питания.

Фильтр входной 49 предназначен для низкочастотной фильтрации напряжения, полученного на выходе узла защиты 48.

Измеритель температуры 50 предназначен для измерения температуры элементов БИП 4.

Узел сигнализации 51 предназначен для сигнализации о состоянии БИП 4 оператору посредством, например, световой индикации и ЭВМ посредством сигналов (например, DEG#, сообщающих, например, о нагреве БИП 4 до фиксированной температуры и, например, FAL# о выключении выходных напряжений за время, например, не менее 100 мкс до начала фактического выключения) (см. фиг.5).

Узел включения 52 предназначен для управления включением/ выключением каналов ВИП 4 под управлением узла контроля и управления 53.

Узел контроля и управления 53 предназначен для сбора информации о состоянии БИП 4 (температура, значения выходного напряжения каналов ВИП 4), об уровне входного сигнала включения, управления включением/выключением БИП 4 и управления сигнализации о состоянии БИП 4.

Каналы ВИП 54-57 предназначены для формирования напряжений питания блоков ЭВМ (+3,3 В, +5,0 В, +12,0 В и -12,0 В) из входного напряжения бортовой сети 16 после ограничения помех, пульсаций и низкочастотной фильтрации.

Системный контроллер 23 блока управления 1 (см. фиг.6) предназначен для формирования сигналов различных устройств блока управления 1 под управлением микропроцессора 18 (см. фиг.2).

Назначение узлов системного контроллера 23 (см. фиг.6) может быть следующим.

Управляющий контроллер 58 предназначен для осуществления функций прерывания, взаимодействия микропроцессора 18 и контроллера системной шины 19 блока управления 1 (см. фиг.2), а также для управления режимами DMA.

Регистр адреса 59 предназначен для фиксирования и формирования текущего адреса из мультиплексированной шины.

Контроллер загрузки 60 предназначен для осуществления загрузки программируемых логических схем (ПЛИС) внешних устройств.

Дешифратор 61 предназначен для определения ресурса, которому выставляются сигналы управления, по выставленному микропроцессором 18 адресу.

Контроллер управления памятью (ОЗУ 17) 62 предназначен для выставления сигналов управления микросхемам ОЗУ 17, при обращении к ним микропроцессора 18 или контроллера системной шины 19.

Контроллеры последовательных портов RS-232-63 и 64 и RS-422/485-65 предназначены для формирования сигналов интерфейса UART (где UART - universal asynchronous receiver/transmitter, логический и канальный уровни интерфейсов RS232/422/485, физический уровень этих интерфейсов формируется на внешних по отношению к системному контроллеру 23 формирователях под управлением микропроцессора 18).

Системный таймер, состоящий, в общем случае, из n таймеров с T.1 66 до Т.n 67, предназначен для отсчета системного времени.

Контроллер взаимодействия с памятью 68, т.е. с ПЗУ 24, предназначен для выставления сигналов управления пользовательских данных микросхемам ПЗУ 24 при обращении к ним микропроцессор