Способ и устройство тасования данных

Иллюстрации

Показать всеИзобретение относится к области микропроцессоров и компьютерных систем. Технический результат изобретения заключается в улучшении характеристик процессора и повышении его производительности. Технический результат достигается за счет того, что согласно инструкции тасования принимают первый операнд, содержащий набор из L элементов данных, и второй операнд, содержащий набор из L масок тасования, причем каждая из масок тасования включает в себя поле «сброс в нуль» и поле выбора, для каждой маски тасования если поле «сброс в нуль» маски тасования не установлено, то перемещают данные, указанные полем выбора маски тасования, из элемента данных первого операнда в ассоциированный элемент данных результата, и если поле «сброс в нуль» маски тасования установлено, то помещают нуль в ассоциированный элемент данных результата. 8 н. и 46 з.п. ф-лы, 16 ил.

Реферат

Настоящая заявка подана как частичное продолжение патентной заявки США 09/952,891 на «Устройство и способ для эффективной фильтрации и свертки данных информационного содержимого» от 29 октября 2001.

Настоящая патентная заявка связана с совместно поданной патентной заявкой США № - на «Способ и устройство для параллельного табличного преобразования с использованием SIMD-инструкций» от 30 июня 2003 и совместно поданной патентной заявкой США № - на «Способ и устройство для переупорядочивания данных между множеством регистров» от 30 июня 2003.

Область техники

Настоящее изобретение относится к области микропроцессоров и компьютерных систем. Более конкретно, настоящее изобретение относится к способу и устройству для тасования данных.

Предшествующий уровень техники

Компьютерные системы все в возрастающей степени проникают в жизнь современного общества. Возможности обработки компьютеров повысили эффективность и производительность труда работников в широком спектре профессий. Так как расходы на приобретение и получение в собственность компьютеров продолжает падать, все большее количество пользователей получают возможность пользоваться выгодами, обеспечиваемыми более новыми и более быстродействующими машинами. Кроме того, многие люди являются приверженцами использования дорожных компьютеров (ноутбуков) ввиду обеспечиваемой ими свободы использования. Мобильные компьютеры дают возможность пользователям простым способом переносить свои данные и работать с ними, когда они покидают место работы или совершают поездки. Этот сценарий хорошо знаком специалистам по маркетингу, должностным лицам корпораций и даже студентам.

По мере совершенствования технологии процессоров также генерируются обновленные коды программного обеспечения для исполнения на машинах с такими процессорами. Пользователи в общем случае ожидают и требуют более высоких показателей от своих компьютеров, независимо от типа используемого программного обеспечения. Один такой вопрос может возникнуть в связи с инструкциями и операциями, которые в текущий момент исполняются в процессоре. Некоторые типы операций требуют больше времени для вычисления ввиду сложности операций и/или типа требуемых схем. Это обеспечивает возможность оптимизации способа, которым исполняются некоторые сложные операции в процессоре.

Мультимедийные приложения способствуют развитию микропроцессоров в течение более десятка лет. Реально большинство компьютерных модернизаций в последние годы стимулировались мультимедийными приложениями. Эти модернизации преобладающим образом имели место в потребительских сегментах, хотя значительный прогресс также наблюдался в предпринимательском сегменте для достижения таких целей, как усовершенствование за счет занимательности обучения и коммуникации. Тем не менее будущие мультимедийные приложения потребуют еще более высоких вычислительных характеристик. В результате современный опыт в области персональных компьютеров будет еще более обогащен за счет аудиовизуальных эффектов, а также за счет большей простоты использования, и что еще более важно, вычисления будут интегрироваться с коммуникациями.

Соответственно, отображение изображений, а также воспроизведение аудио- и видеоданных, которые совместно определяются термином «контент» (информационное содержимое), становятся все более популярными приложениями для современных вычислительных устройств. Операции фильтрации и свертки являются некоторыми из наиболее общих операций, выполняемых над данными контента, такими как аудиоданные и видеоданные изображений. Такие операции являются интенсивными в вычислительном смысле, но обеспечивают высокий уровень параллелизма данных, который может быть использован посредством эффективной реализации с использованием различных устройств хранения данных, таких как, например, регистры с одним потоком команд и множеством потоков данных (SIMD-регистры). Ряд современных архитектур также требуют ненужных изменений типов данных, что минимизирует пропускную способность инструкции и значительно увеличивает число тактовых циклов, требуемых для упорядочения данных для арифметических операций.

Краткое описание чертежей

Настоящее изобретение иллюстрируется для примера, но не в качестве ограничения, на чертежах, на которых одинаковые ссылочные позиции обозначают сходные элементы и на которых представлено следующее:

Фиг.1А - блок-схема компьютерной системы, образованной процессором, который включает в себя исполнительные модули для исполнения инструкции тасования данных в соответствии с вариантом осуществления настоящего изобретения.

Фиг.1В - блок-схема другой приведенной для примера компьютерной системы в соответствии с вариантом осуществления настоящего изобретения.

Фиг.1С - блок-схема еще одной приведенной для примера компьютерной системы в соответствии с альтернативным вариантом осуществления настоящего изобретения.

Фиг.2 - блок-схема микроархитектуры для процессора в одном варианте осуществления, который включает в себя логические схемы для выполнения операций тасования данных в соответствии с настоящим изобретением.

Фиг.3А-С - иллюстрации масок тасования согласно различным вариантам осуществления настоящего изобретения.

Фиг.4А - иллюстрация представлений различных типов пакетных данных в мультимедийных регистрах в соответствии с вариантом осуществления настоящего изобретения.

Фиг.4В - иллюстрация типов пакетных данных в соответствии с альтернативным вариантом осуществления настоящего изобретения.

Фиг.4С - вариант осуществления формата кодирования операции (кода операции) для инструкции тасования.

Фиг.4D - иллюстрация альтернативного формата кодирования операции.

Фиг.4Е - иллюстрация другого альтернативного формата кодирования операции.

Фиг.5 - блок-схема варианта осуществления логики для выполнения операции тасования над операндом данных на основе маски тасования в соответствии с настоящим изобретением.

Фиг.6 - блок-схема варианта осуществления схемы для выполнения операции тасования данных в соответствии с настоящим изобретением.

Фиг.7 - иллюстрация операции тасования данных над элементами данных байтовой длины в соответствии с вариантом осуществления настоящего изобретения.

Фиг.8 - иллюстрация операции тасования данных над элементами данных с длиной слова в соответствии с другим вариантом осуществления настоящего изобретения.

Фиг.9 - блок-схема варианта осуществления способа тасования данных.

Фиг.10А-Н - иллюстрация операции алгоритма параллельного табличного преобразования с использованием SIMD-инструкций.

Фиг.11 - блок-схема варианта осуществления способа выполнения табличного преобразования с использованием SIMD-инструкций.

Фиг.12 - блок-схема другого варианта осуществления способа выполнения табличного преобразования.

Фиг.13А-С - иллюстрация алгоритма переупорядочения данных между множеством регистров.

Фиг.14 - блок-схема, иллюстрирующая вариант осуществления способа переупорядочения данных между множеством регистров.

Фиг.15А-К - иллюстрация алгоритма тасования данных между множеством регистров для генерирования перемеженных данных.

Фиг.16 - блок-схема, иллюстрирующая вариант осуществления способа тасования данных между множеством регистров для генерирования перемеженных данных.

Детальное описание

Раскрыты способ и устройство для тасования данных. Также описаны способ и устройство для параллельного табличного преобразования с использованием SIMD-инструкций. Также раскрыты способ и устройство для переупорядочения данных между множеством регистров. Представленные варианты осуществления описаны в контексте микропроцессора, но не ограничены этим. Хотя последующие варианты осуществления описаны со ссылкой на процессор, другие варианты осуществления применимы к другим типам интегральных схем и логических устройств. Те же методы и решения, соответствующие настоящему изобретению, могут быть легко применены к другим типам схем или полупроводниковых устройств, которые могут получать выгоду от более высокой пропускной способности конвейерной обработки и улучшенной производительности. Решения, согласно настоящему изобретению, применимы к любому процессору или машине, которая выполняет обработку данных. Однако настоящее изобретение не ограничивается процессорами или машинами, которые выполняют 256-битовые, 128-битовые, 64-битовые, 32-битовые или 16-битовые операции над данными, и может быть применено к любому процессору и машине, где требуется тасование данных.

В последующем описании в целях пояснения приводятся различные конкретные детали, чтобы более глубоко вникнуть в настоящее изобретение. Специалисту в данной области техники, однако, должно быть понятно, что эти конкретные детали не обязательны для реализации настоящего изобретения. В других случаях хорошо известные электрические структуры и схемы не раскрываются подробно, чтобы не затенять сущность изобретения несущественными деталями. Кроме того, в последующем описании приводятся примеры и на чертежах показываются различные примеры в целях иллюстрации. Однако эти примеры не должны толковаться в ограничительном смысле, поскольку они предназначены только для обеспечения примеров настоящего изобретения, но не представляют исчерпывающий перечень возможных вариантов реализации настоящего изобретения.

В варианте осуществления способы, соответствующие настоящему изобретению, воплощены в машиноисполняемых инструкциях. Инструкции могут использоваться для обеспечения того, чтобы универсальный или специализированный процессор, который запрограммирован этими инструкциями, выполнял этапы настоящего изобретения. Альтернативно, этапы настоящего изобретения могут выполняться конкретными компонентами аппаратных средств, которые содержат аппаратные логические средства для выполнения этих этапов, или любой комбинацией программируемых компьютерных компонентов и настраиваемых компонентов аппаратных средств.

Хотя приведенные ниже примеры описывают обработку и распределение инструкций в контексте исполнительных модулей и логических схем, друге варианты осуществления настоящего изобретения могут быть выполнены с помощью программного обеспечения. Настоящее изобретение может быть обеспечено как компьютерный программный продукт или программное обеспечение, что может включать в себя машину или машиночитаемый носитель с сохраненными на нем инструкциями, которые могут быть использованы для программирования компьютера (или иных электронных приборов) для выполнения процесса, соответствующего настоящему изобретению. Такое программное обеспечение может быть сохранено в памяти в системе. Аналогичным образом код может распространяться по сети или с помощью другого машиночитаемого носителя. Таким образом, машиночитаемый носитель может включать в себя любой механизм для хранения или передачи информации в форме, обеспечивающей возможность считывания машиной (например, компьютером), включая, без ограничения указанным, гибкие диски, оптические диски, компакт-диски (CD), ПЗУ на компакт-дисках (CD-ROM), магнитооптические диски, ПЗУ, ОЗУ, стираемое программируемое ПЗУ (СППЗУ), электронно-стираемое программируемое ПЗУ (ЭСППЗУ), магнитные или оптические карты, флэш-память, передачу через Интернет, электрическую, оптическую, акустическую или другие формы распространяющихся сигналов (например, несущие волны, инфракрасные сигналы, цифровые сигналы и т.д.) и тому подобное.

Соответственно, машиночитаемый носитель включает в себя любой тип среды передачи/машиночитаемого носителя, подходящий для хранения или передачи электронных инструкций или информации в форме, считываемой машиной (например, компьютером). Более того, настоящее изобретение может также предусматривать загрузку в виде компьютерного программного продукта. Как таковая программа может переноситься с удаленного компьютера (например, сервера) на запрашивающий компьютер (например, клиент). Перенос программы может осуществляться с помощью электрических, оптических, акустических или других форм распространяющихся сигналов, воплощенных в несущем колебании или другой среде распространения в коммуникационном канале (например, модем, сетевое соединение и тому подобное).

Кроме того, варианты осуществления структур интегральных схем в соответствии с настоящими изобретениями могут быть переданы или перенесены в электронной форме как база данных на магнитной ленте или ином машиночитаемом носителе. Например, электронная форма структуры интегральной схемы процессора в одном варианте осуществления может обрабатываться или изготавливаться на производстве для получения компьютерного компонента. В другом случае структура интегральной схемы в электронной форме может обрабатываться машиной для моделирования компьютерного компонента. Таким образом, топологии схем и/или структуры процессоров в некоторых вариантах осуществления могут распространяться посредством машиночитаемых носителей или воплощаться на них для изготовления схем или для моделирования интегральной схемы, модель которой при обработке машиной моделирует процессор. Машиночитаемый носитель также может хранить данные, представляющие предварительно заданные функции, в соответствии с настоящим изобретением в других вариантах осуществления.

В современных процессорах используется ряд различных исполнительных модулей для обработки и исполнения разнообразных кодов и инструкций. Не все инструкции создаются одинаковыми, так как некоторые обладают более высоким быстродействием выполнения, в то время как другие требуют огромного числа тактовых циклов. Чем более высокой является пропускная способность инструкций, тем лучше показатели процессора в целом. Таким образом, было бы предпочтительным, чтобы максимально больше инструкций имели максимально возможное быстродействие. Однако имеются некоторые инструкции, которые имеют более высокую сложность и требуют большего времени исполнения и больших ресурсов процессора. Например, имеются инструкции с плавающей запятой, операции загрузки/сохранения, перемещения данных и т.д.

По мере того как все больше компьютерных систем используется в Интернете и мультимедийных приложениях, со временем вводится дополнительная поддержка процессора. Например, целочисленные/с плавающей запятой SIMD-инструкции и потоковые SIMD-инструкции (SSE) представляют собой инструкции, которые сокращают общее число инструкций, требуемых для выполнения конкретной программной задачи. Эти инструкции могут повышать быстродействие выполнения программного обеспечения за счет параллельного осуществления операций над множеством элементов данных. В результате может быть обеспечен выигрыш по показателям в широком диапазоне приложений, включая обработку видео, речи, изображений/фотоснимков. Реализация SIMD-инструкций в микропроцессорах и аналогичных типах логических схем обычно связана с рядом вопросов. Кроме того, сложность SIMD-операций часто приводит к необходимости введения дополнительных схем для корректной обработки и манипулирования данными.

Варианты осуществления настоящего изобретения обеспечивают способ реализации упакованных байтовых инструкций тасования с возможностью сброса в нуль в качестве алгоритма, который использует SIMD-ориентированные аппаратные средства. В одном варианте осуществления алгоритм основан на принципе тасования данных из конкретного регистра или ячейки памяти на основе значений управляющей маски для каждой позиции элемента данных. Варианты осуществления упакованного байтового тасования могут использоваться для сокращения числа инструкций, требуемых во многих различных приложениях, которые предусматривают переупорядочение данных. Упакованные байтовые инструкции тасования могут также использоваться для любого приложения с не выровненными нагрузками. Варианты осуществления такой инструкции тасования могут быть использованы для фильтрации, чтобы упорядочить данные для обеспечения эффективных операций умножения-сложения. Аналогичным образом, упакованные инструкции тасования могу быть использованы в видео приложениях и в приложениях шифрования для упорядочения данных и малых таблиц преобразования. Такая инструкция может быть использована для смешивания данных из двух или более регистров. Таким образом, варианты осуществления упакованного тасования в соответствии с алгоритмом сброса в нуль, согласно настоящему изобретению, могут быть реализованы в процессе для поддержки SIMD-операций эффективным образом, без заметного ухудшения показателей в целом.

Варианты осуществления настоящего изобретения обеспечивают инструкцию тасования упакованных данных (PSHUFB) с возможностью сброса в нуль, для эффективного упорядочения и расположения данных любого размера. В одном варианте осуществления данные перетасовываются или переупорядочиваются в регистре с битовой гранулярностью. Операция битового тасования упорядочивает размеры данных, которые превышают байты, за счет поддержания относительного положения байтов в данных большего размера в процессе операции тасования. Кроме того, операция байтового тасования может изменить относительное положение данных в SIMD-регистре и может также дублировать данные. Эта PSHUFB-инструкция перетасовывает байты из первого регистра источника в соответствии с содержимым байтов управления тасованием во втором регистре источника. Хотя инструкция осуществляет перестановку данных, маска тасования не подвергается воздействию и остается неизменной в течение этой операции тасования в данном варианте осуществления. Мнемоника для одной реализации представляет следующее: «PSHUFB-регистр 1, регистр 2/память», при этом первый и второй операнды являются SIMD-регистрами. Однако регистр второго операнда может также быть заменен ячейкой памяти. Первый операнд включает в себя источник данных для тасования. Для этого варианта осуществления регистр для первого операнда также является регистром адресата. Варианты осуществления в соответствии с настоящим изобретением также включают в себя возможность установки выбранных байтов на нуль, в дополнение к изменению их позиции.

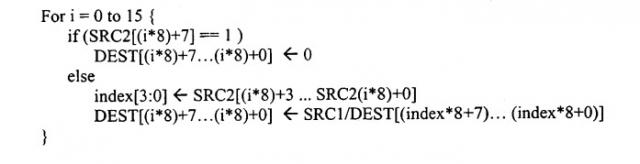

Второй операнд включает в себя набор байтов маски управления тасованием для обозначения шаблона тасования. Число битов, используемых для выбора элемента данных источника, равно логарифму по основанию два от числа элементов данных в операнде источника. Например, число байтов в варианте осуществления с 128-битовым регистром равно шестнадцати. Log216=4. То есть требуется четыре бита или полубайт. Индекс [3:0] в коде, представленном ниже, относится к четырем битам. Если старший бит (MSB), бит 7 в данном варианте осуществления, байта управления тасованием установлен, то постоянный нуль записывается в байт результата. Если младший полубайт байта I второго операнда, набор маски, содержит целое число J, то инструкция тасования обеспечивает то, что J-й байт первого регистра источника копируется в позицию I-го байта регистра адресата. Ниже приведен пример псевдокода для варианта осуществления упакованной операции байтового тасования над 128-битовыми операндами:

Аналогично, ниже приведен пример псевдокода для другого варианта осуществления упакованной операции байтового тасования над 64-битовыми операндами:

Заметим, что в этом варианте осуществления 64-битового регистра используются младшие три бита маски, так как имеется восемь байтов в 64-битовом регистре. Log28=3. Индекс [2:0] в коде, представленном выше, относится к трем битам. В альтернативных вариантах число битов в маске может изменяться для соответствия числу элементов данных, имеющихся в данных источника. Например, маска с младшими пятью битами необходима для выбора элемента данных в 256-битовом регистре.

В настоящее время является несколько затруднительным и трудоемким переупорядочивать данные в SIMD-регистре. Некоторые алгоритмы требуют больше инструкций для упорядочения данных для арифметических операций, чем действительное число инструкций для исполнения этих операций. Путем реализации вариантов осуществления упакованной инструкции байтового тасования в соответствии с настоящим изобретением можно существенным образом уменьшить число инструкций, требуемых для осуществления переупорядочивания данных. Например, один вариант осуществления упакованной инструкции байтового тасования может транслировать байт данных во все позиции 128-битового регистра. Трансляция данных в регистр часто используется в приложениях фильтрации, где один элемент данных умножается на много коэффициентов. Без такой инструкции байт данных должен был бы фильтроваться из его источника и сдвигаться в низшую байтовую позицию. Затем этот один байт должен был бы дублироваться сначала как байт, затем эти два байта должны дублироваться вновь для формирования двойного слова, и затем двойное слово должно дублироваться для формирования в итоге квадраслова. Все эти операции могут быть заменены одной упакованной инструкцией тасования.

Аналогичным образом реверсирование всех байтов в 128-битовом регистре, такое как переход между большим конечным и малым конечным форматами, может легко выполняться с помощью упакованной инструкции байтового тасования. В то время как даже эти довольно простые шаблоны требуют некоторого количества инструкций, если бы не использовалась упакованная инструкция тасования, комплексные или случайные шаблоны требуют намного больше неэффективных процедур инструкций. Наиболее простое решение для переупорядочения случайных байтов в SIMD-регистре заключается в записи их в буфер и затем использовании целочисленных байтовых считываний/записей для переупорядочения их и затем считывания их назад в SIMD-регистр. Вся эта обработка данных потребует длинной кодовой последовательности, в то время как может быть достаточной единственная упакованная инструкция тасования. Путем уменьшения требуемого числа инструкций можно значительно уменьшить число тактовых циклов, требуемых для формирования того же самого результата. Варианты осуществления настоящего изобретения также используют инструкции тасования для доступа к множеству значений в таблице с SIMD-инструкциями. Даже в случае, когда таблица имеет в два раза больший размер по сравнению с регистром, алгоритмы, соответствующие настоящему изобретению, позволяют осуществить доступ к элементам данных с более высокой скоростью, чем в случае одного элемента данных на инструкцию, как при целочисленных операциях.

На фиг.1А показана блок-схема примерной компьютерной системы с процессором, который содержит исполнительные модули для исполнения инструкции для тасования данных в соответствии с одним вариантом осуществления настоящего изобретения. Система 100 содержит компонент, такой как процессор 102, для использования исполнительных модулей, включая логику для выполнения алгоритмов тасования данных, в соответствии с настоящим изобретением, как в описанном варианте осуществления. Система 100 представляет системы обработки на основе микропроцессоров Pentium® III, Pentium® 4, Celeron®, XeonTM, Itanium®, XScaleTM и/или StrongARMTM, поставляемых компанией Intel Corporation (Santa Clara, California), хотя и другие системы (включая РС с другими микропроцессорами, рабочие станции, приставки и т.д.) также могут использоваться. В одном варианте осуществления приведенная в качестве образца система 100 может исполнять версию операционной системы WINDOWSTM, поставляемой компанией Microsoft Corporation (Redmond, Washington), хотя могут использоваться и другие операционные системы (например, UNIX, Linux), встроенное программное обеспечение и/или графические пользовательские интерфейсы. Таким образом, настоящее изобретение не ограничено какой-либо конкретной комбинацией схем аппаратных средств и программного обеспечения.

Настоящее изобретение не ограничено компьютерными системами. Альтернативные варианты осуществления настоящего изобретения могут использоваться в других устройствах, таких как портативные устройства и встроенные приложения. Некоторые примеры портативных устройств включают в себя сотовые телефоны, устройства Интернет-протокола, цифровые камеры, персональные цифровые помощники (PDA) и карманные РС. Встроенные приложения могут включать в себя микроконтроллер, цифровой процессор сигналов (DSP), систему на микросхеме, сетевые компьютеры (NetPC), приставки, сетевые концентраторы, коммутаторы глобальной сети (WAN) или любую другую систему, которая выполняет целочисленные операции тасования над операндами. Кроме того, некоторые архитектуры реализованы для обеспечения возможности инструкциям работать над различными данными одновременно, чтобы улучшить эффективность мультимедийных приложений. По мере того как число типов и объем данных увеличиваются, компьютеры и их процессоры должны совершенствоваться, чтобы манипулировать данными более эффективными методами.

На фиг.1А показана блок-схема компьютерной системы 100, образованной процессором 102, который включает в себя один или более исполнительных модулей 108 для выполнения алгоритма тасования данных в соответствии с настоящим изобретением. Представленный вариант осуществления описан в контексте однопроцессорной системы рабочего стола или серверной системы, но альтернативные варианты осуществления могут быть включены в многопроцессорную систему. Система 100 является примером архитектуры концентратора. Компьютерная система 100 содержит процессор 102 для обработки сигналов данных. Процессор 102 может быть микропроцессором компьютера с полным набором команд (CICS), микропроцессором компьютера с сокращенным набором команд (RICS), микропроцессором с командными словами сверхбольшой длины (VLIW), процессором, реализующим комбинацию наборов инструкций, или любым другим процессорным устройством, например, таким как цифровой процессор сигналов. Процессор 102 связан с шиной 110 процессора, которая может передавать сигналы данных между процессором 102 и другими компонентами в системе 100. Элементы системы 100 выполняют свои обычные функции, хорошо известные специалистам в данной области техники.

В одном варианте осуществления процессор 102 содержит внутреннюю кэш-память 104 уровня 1 (L1). В зависимости от архитектуры процессор 102 может иметь один внутренний кэш или множество уровней внутреннего кэша. Альтернативно, в другом варианте осуществления кэш-память может содержаться вне процессора 102. Другие варианты осуществления могут также содержать комбинацию внутренних и внешних кэшей, в зависимости от конкретной реализации и потребностей. Регистровый файл 106 может сохранять различные типы данных в разных регистрах, включая целочисленные регистры, регистры с плавающей запятой, регистры статуса и регистры указателя инструкции.

Исполнительный модуль 108, включающий в себя логику для выполнения целочисленных операций и операций с числами с плавающей запятой, также содержится в процессоре 102. Процессор 102 также содержит ПЗУ микрокода (ucode), которое хранит микрокод для определенных макроинструкций. В этом варианте осуществления исполнительный модуль 108 содержит логику для обработки набора 109 упакованных инструкций. В одном варианте осуществления набор 109 упакованных инструкций включает в себя упакованную инструкцию тасования для организации данных. Путем включения набора 109 упакованных инструкций в набор инструкций универсального процессора 102 вместе со связанными схемами для исполнения инструкций операции, используемые множеством мультимедийных приложений, могут выполняться с использованием упакованных данных в универсальном процессоре 102. Таким образом, многие мультимедийные приложения могут выполняться с ускорением и более эффективно за счет использования полной ширины шины данных процессора для выполнения операций над упакованными данными. Это может исключить потребность в переносе малых блоков данных по шине данных процессора для выполнения одной или более операций над одним элементом данных в каждый данный момент времени.

Альтернативные варианты осуществления исполнительного модуля 108 также могут быть использованы в микроконтроллерах, встроенных процессорах, графических устройствах, DSP и логических схемах других типов. Система 100 содержит память 120. Память 120 может представлять собой динамическое ОЗУ (DRAM), статическое ОЗУ (SRAM), флэш-память или иное запоминающее устройство. Память 120 может сохранять инструкции и/или данные, представленные сигналами данных, которые могут исполняться процессором 102.

Микросхема 116 системной логики связана с процессорной шиной 110 и памятью 120. Микросхема 116 системной логики в представленном варианте осуществления представляет собой концентратор контроллера памяти (МСН). Процессор 102 может осуществлять информационный обмен с МСН 116 через процессорную шину 110. МСН 116 обеспечивает канал 118 памяти с большой шириной полосы для памяти 120 для хранения инструкций и данных и для хранения команд, данных и текстур графики. МСН 116 предназначен для направления сигналов данных между процессором 102, памятью 120 и другими компонентами в системе 100 и для переноса сигналов данных между процессорной шиной 110, памятью 120 и системой ввода/вывода (I/O) 122. В некоторых вариантах осуществления микросхема 116 системной логики может обеспечивать графический порт для связи с графическим контроллером 112. МСН 116 связан с памятью 120 через интерфейс 118 памяти. Графическая карта 112 связана с МСН 116 через межсоединение 114 ускоренного графического порта (AGP).

Система 100 использует специализированную шину 122 интерфейса концентратора для связи МСН 116 с концентратором контроллера I/O (ICH) 130. ICH 130 обеспечивает непосредственные соединения с некоторыми устройствами ввода/вывода через локальную шину ввода/вывода. Локальная шина ввода/вывода является высокоскоростной шиной ввода/вывода для соединения периферийных устройств с памятью 120, набором микросхем и процессором 102. Некоторыми примерами также являются аудио контроллер, концентратор программно-аппаратных средств (флэш-BIOS) 128, беспроводный приемопередатчик 126, память 124 данных, традиционный контроллер ввода/вывода, содержащий интерфейсы пользовательского ввода и клавиатуры, последовательный порт расширения, такой как порт универсальной последовательной шины (BUS), и сетевой контроллер 134. Устройство 124 хранения данных может содержать накопитель на жестком диске, накопитель на гибких дисках, устройство CD-ROM, устройство флэш-памяти или другие устройства массовой памяти.

В другом варианте осуществления системы исполнительный модуль для исполнения алгоритма с инструкцией тасования может использоваться с системой на микросхеме. Один вариант осуществления системы на микросхеме содержит процессор и память. Памятью для одной такой системы является флэш-память. Флэш-память может находиться на том же самом кристалле, что и процессор и другие системные компоненты. Дополнительно другие логические блоки, такие как контроллер памяти или графический контроллер, также могут находиться в системе на микросхеме.

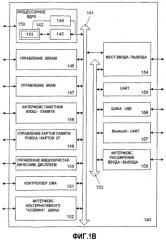

На фиг.1В показан альтернативный вариант осуществления системы 140 обработки данных, которая реализует принципы настоящего изобретения. Один вариант осуществления системы 140 обработки данных представляет собой процессор приложений Intel®PCA (Архитектура персонального Интернет-клиента Intel®) с технологией IntelXScaleТМ, как представлено во Всемирной паутине по адресу developer.intel.com). Специалистам в данной области техники должно быть понятно, что описанные варианты осуществления могут быть использованы с альтернативными системами обработки без отклонения от объема изобретения.

Компьютерная система 140 содержит процессорное ядро 159, имеющее возможность выполнения SIMD-операций, включая тасование. В одном варианте осуществления процессорное ядро 159 представляет собой блок обработки с архитектурой любого типа, включая, без ограничения указанным, архитектуру типа SISC, RISC, VLIW. Процессорное ядро 159 содержит исполнительный блок 142, набор файловых регистров 145 и декодер 144. Процессорное ядро 159 также включает в себя дополнительные схемы (не показаны), которые не являются необходимыми для понимания настоящего изобретения. Исполнительный блок 142 используется для исполнения инструкций, принимаемых процессорным ядром 159. В дополнение к распознаванию типовых процессорных инструкций исполнительный блок 142 может распознавать инструкции в наборе 143 упакованных инструкций для выполнения операций над упакованными форматами данных. Набор 143 упакованных инструкций включает в себя инструкции для поддержки операций тасования, но может также включать в себя и другие упакованные инструкции. Исполнительный блок 142 связан с регистровым файлом 145 посредством внутренней шины. Регистровый файл 145 представляет область памяти на процессорном ядре 159 для хранения информации, включая данные. Как упомянуто выше, понятно, что область памяти, используемая для хранения пакетных данных, не является критичной. Исполнительный блок 142 связан с декодером 144. Декодер 144 используется для декодирования инструкций, принятых процессорным ядром 159, в управляющие сигналы и/или точки ввода в микрокод. В ответ на эти управляющие сигналы и/или точки ввода в микрокод исполнительный блок 142 выполняет соответствующие операции.

Процессорное ядро 159 связано с шиной 141 для информационного обмена с множеством других устройств системы, которые могут включать в себя, без ограничения указанным, например, управление синхронным динамическим ОЗУ (SDRAM), управление 147 статическим ОЗУ (SRAM), интерфейс 148 пакетной флэш-памяти, управление 149 картой памяти PCMCIA (Международной Ассоциацией производителей карт памяти для персональных компьютеров)/картой компактной флэш-памяти (CF), управление 150 жидкокристаллическим дисплеем, контроллер 151 прямого доступа к памяти (DMA), интерфейс 152 альтернативного "хозяина" шины (устройства управления передачей данных по шине). В одном варианте осуществления система 140 обработки данных может также содержать мост 154 ввода/вывода для коммуникации с различными устройствами ввода/вывода через шину 153 ввода/вывода. Такие устройства ввода/вывода могут включать в себя, без ограничения указанным, например, универсальный асинхронный приемник/передатчик (UART) 155, универсальную последовательную шину (USB) 156, беспроводный Bluetooth-UART 157 и интерфейс 158 расширения ввода/вывода.

Один вариант осуществления системы 140 обработки данных обеспечивает мобильные, сетевые и/или беспроводные коммуникации и процессорное ядро 159, имеющее возможность выполнения SIMD-операций, включая операцию тасования. Процессорное ядро 159 может быть запрограммировано в соответствии с различными алгоритмами обработки аудио, видео, формирования изображений и коммуникации, включая дискретные преобразования, такие как преобразования Уолша-Адамара, быстрое преобразование Фурье (БПФ) и дискретное косинусное преобразование (ДКП), и соответствующие им инверсные преобразования; методы сжатия/декомпрессии, такие как преобразование цветового пространства, оценивание движения в кодированном видео или компенсация движения в декодированном видео; функции модуляции/демодуляции, такие как импульсно-кодовая модуляция.

На фиг.1С показан еще один вариант осуществления системы обработки данных, обеспечивающий выполнение SIMD-операций тасования. В соответствии с другим вариантом осуществления система 160 обработки данных может содержать основной процессор 166, SIMD-сопроцессор 161, кэш-память 167 и систему 168 ввода/вывода. Система 168 ввода/вывода может быть дополнительно связана с беспроводным интерфейсом 169. SIMD-сопроцессор 161 может выполнять SIMD-операции, включая тасование данных. Процессорное ядро 170 может подходить для изготовления в одном или более технологических процессах, а также путем представления на машиночитаемом носителе с достаточной детализацией может способствовать облегчению изготовления всей или части системы 160 обработки, содержащей процессорное ядро 17