Устройство активной защиты и обеспечения технической готовности элементов распределенной локальной вычислительной сети в условиях внешних деструктивных воздействий

Иллюстрации

Показать всеИзобретение относится к контрольно-измерительной технике, позволяющей осуществлять постоянный мониторинг и диагностирование электромагнитной обстановки (ЭМО), существенной для работы ЭВМ в составе распределенной локальной вычислительной сети (ЛВС), и, опираясь на результаты прогнозирования, осуществлять заблаговременное переключение пользователей на ЭВМ, не подверженные воздействию электромагнитного импульса (ЭМИ). Техническим результатом является расширение класса решаемых задач и обеспечение непрерывности предоставления информационных услуг абонентам распределенной ЛВС. Устройство содержит анализатор параметрических отказов и сбоев, измеритель напряженности поля и управляющую плату с внешним запуском, состоящую из блока коммутации, перепрограммируемого ПЗУ и устройства вероятностного прогнозирования. 6 ил.

Реферат

Изобретение относится к контрольно-измерительной технике, позволяющей осуществлять постоянный мониторинг электромагнитной обстановки (ЭМО), оказывающей влияние на работоспособность элементов распределенной локальной вычислительной сети (ЛВС), и, опираясь на результаты прогнозирования, осуществлять заблаговременное отключение элементов распределенной ЛВС (ЭВМ), подвергающихся воздействию электромагнитного импульса (ЭМИ), от пользователей и подключение резервных ЭВМ, не подверженных данному виду воздействия, к пользователям.

Существует устройство, позволяющее определять параметрические отказы технических устройств [1]. Однако данное устройство не позволяет выявлять причину возникновения параметрических отказов, которые могут возникнуть из-за внешних воздействий или эксплуатационных факторов. Наиболее близким по технической сущности является устройство, основной особенностью которого является способность идентифицировать факт отказа технических устройств по заданному количеству сбоев за выбранный интервал времени. Данное устройство выбрано в качестве прототипа [2].

Устройство-прототип содержит пороговые блоки, формирователь импульса, элементы задержки, инверторы, элементы И, элемент ИЛИ, дифференцирующий элемент, триггеры, формирователь паузы, счетчики, генератор импульсов, делители частоты, переключатель, регистр, формирователь импульса, регистр, блок контроля постепенных отказов, генератор тактовых импульсов, счетчик импульсов по модулю N, блок ячеек памяти, табло отображения, селектор данных, вычитатель.

Блок ячеек памяти анализатора параметрических отказов и сбоев предназначен для записи информации о: количестве отказов контролируемых объектов, суммарной длительности отказов, количестве сбоев контролируемого изделия, суммарной продолжительности сбоев, наработке на сбой за требуемый период времени.

Недостатком данного устройства является невозможность его использования для обеспечения активной защиты и требуемой технической готовности элементов распределенной ЛВС, в условиях электромагнитных воздействий, из-за того, что это устройство фиксирует только факт наличия параметрического отказа или сбоя, не определяя при этом причину их возникновения.

Техническим результатом является расширение класса решаемых задач и обеспечение непрерывности предоставления информационных услуг абонентам распределенной ЛВС за счет снижения времени отключения пользователей ЛВС от ЭВМ.

Этот результат достигается тем, что в устройство-прототип, содержащее первый пороговый блок, формирователь импульса, первый элемент задержки, первый инвертор, первый элемент И, второй элемент ИЛИ, дифференцирующий элемент, четвертый элемент И, первый триггер, третий элемент И, второй инвертор, второй элемент задержки, формирователь паузы, шестой элемент И, третий триггер, четвертый триггер, второй счетчик, генератор импульсов, первый делитель частоты, второй элемент И, первый элемент ИЛИ, первый счетчик, переключатель, регистр, пятый элемент И, третий счетчик, второй триггер, седьмой элемент И, пятый триггер, восьмой элемент И, четвертый счетчик, при этом вход первого порогового блока является информационным входом анализатора, а выход первого порогового блока соединен с единичным входом третьего триггера, входом первого элемента задержки, нулевым входом первого триггера, третьим входом третьего элемента И, входом сброса формирователя пауз, входом второго инвертора и входом запуска формирователя импульса, выход которого соединен с входом первого инвертора, выход которого подключен к входу дифференцирующего элемента, первому входу седьмого элемента И, входу сброса четвертого счетчика и второму входу первого элемента И, первый вход которого соединен с выходом первого элемента задержки, а выход - со вторым входом второго элемента ИЛИ, выход которого подключен к единичному входу четвертого триггера, инверсный выход которого связан с третьим входом восьмого элемента И, а прямой выход соединен с первым входом пятого элемента ИЛИ, выход которого подключен к счетному входу второго счетчика и второму входу второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к суммирующему входу первого счетчика, выход генератора импульсов соединен с входом первого делителя частоты, выход которого соединен с первым входом второго элемента И и вторым входом седьмого элемента И, выход которого соединен с входом сложения четвертого счетчика, выход которого соединен с нулевым входом пятого триггера, единичный вход которого соединен с первым входом второго элемента ИЛИ и выходом третьего элемента И, второй вход которого, а также нулевой вход четвертого триггера и вход сброса формирователя импульса связаны с прямым выходом третьего триггера, нулевой вход которого подключен к выходу шестого элемента И, первый и второй входы которого подключены к выходам второго элемента задержки и формирователя паузы соответственно, первый вход третьего элемента И соединен с прямым выходом первого триггера, единичный вход которого подключен к выходу четвертого элемента И, первый вход которого связан с выходом дифференцирующего элемента, а второй вход четвертого элемента И, а также вход второго элемента задержки и вход запуска формирователя паузы соединены с выходом второго инвертора, первый и второй информационные выходы переключателя связаны с вторым выходом первого элемента ИЛИ и выходом вычитания первого счетчика, а информационный вход переключателя - с выходом пятого элемента И, третий вход первого элемента ИЛИ и вход вычитания четвертого счетчика соединены с выходом восьмого элемента И, первый вход которого подключен к прямому выходу пятого триггера, а второй вход подключен к инверсному выходу второго триггера, первый установочный вход третьего счетчика связан с выходом регистра, выход обнуления третьего счетчика соединен с входом считывания регистра и с нулевым входом второго триггера, прямой выход второго триггера подключен к входу пятого элемента И, генератор тактовых импульсов, подключен к суммирующему входу пятого счетчика импульсов, выход которого подключен к первому входу третьего элемента ИЛИ, входу четвертого элемента задержки и первому входу четвертого элемента ИЛИ, выход которого соединен со входом счетчика импульсов по модулю N, выход которого соединен с управляющим входом блока ячеек памяти, выход которого соединен с табло отображения, селектор данных, выход которого соединен со входом первого порогового блока, второго порогового блока, выход которого соединен с входом третьего инвертора, выход которого соединен с входом третьего элемента задержки, выход которого соединен с первым входом девятого элемента И, второй вход которого связан с выходом четвертого элемента задержки, а выход девятого элемента И подключен к второму входу четвертого элемента ИЛИ и второму входу третьего элемента ИЛИ, выход которого соединен с управляющим входом селектора данных, информационные входы блока ячеек памяти соединены с первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым счетчиками импульсов, регистром, первым, вторым, третьим, четвертым, пятым триггерами, формирователя паузы, формирователя импульсов, второй делитель частоты, вход которого соединен с выходом первого порогового блока, а выход с первым входом десятого элемента И, второй вход которого соединен с выходом первого порогового блока и суммирующим входом седьмого счетчика, выход десятого элемента И связан с суммирующим входом шестого счетчика, выход которого соединен с первым входом первого вычитателя, второй вход которого соединен с выходом первого счетчика, а выход с суммирующим входом восьмого счетчика, выход обнуления седьмого счетчика соединен с первым входом второго вычитателя, второй вход которого подключен к выходу обнуления второго счетчика, а выход второго вычитателя связан с суммирующим входом девятого счетчика, выход которого подключен к первому входу одиннадцатого элемента И, также выход девятого счетчика подключен к суммирующему входу десятого счетчика, выход которого соединен с вторым входом пятого элемента ИЛИ, формирователь импульса, выход которого соединен с входом третьего делителя частоты, выход которого связан с суммирующим входом одиннадцатого счетчика импульсов, выход которого подключен к обнуляющему входу двенадцатого счетчика импульсов и входу четвертого инвертора, выход которого соединен со вторым входом одиннадцатого элемента И, введены измеритель напряженности поля (ИНП), управляющая плата с внешним запуском (УПВЗ), состоящая из блока коммутации (БК), электронно-перепрограммируемого постоянного запоминающего устройства (ЭППЗУ), устройства вероятностного прогнозирования (УВП), при этом выход ИНП соединен с первым входом БК, второй выход которого соединен с первым входом ЭППЗУ, второй выход которого соединен с первым входом УВП, четвертый вход БК соединен с выходом УВП, третий вход/выход ЭППЗУ соединен с блоком ячеек памяти анализатора параметрических отказов и сбоев, пользователь соединен с шестым вход/выходом БК, выходы которого (от седьмого...до N-го) соединены с входами ЭВМ распределенной ЛВС соответственно, выходы каждой из ЭВМ распределенной ЛВС соединены с 1 по N входами анализатора параметрических отказов и сбоев.

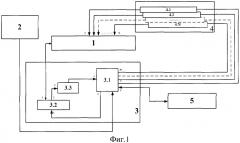

Заявленное устройство поясняется чертежами, на которых показаны:

Фиг.1 - устройство активной защиты и обеспечения технической готовности элементов распределенной локальной вычислительной сети в условиях внешних деструктивных воздействий;

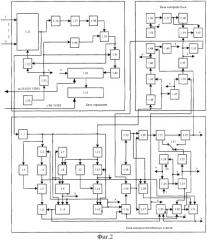

Фиг.2 - анализатор параметрических отказов и сбоев;

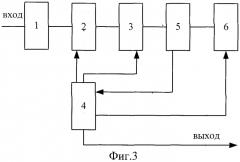

Фиг.3 - вариант структурной схемы измерителя напряженности поля;

Фиг.4 - вариант структурной схемы блока коммутации;

Фиг.5 - вариант структурной схемы электронно-перепрограммируемого постоянного запоминающего устройства;

Фиг.6 - вариант структурной схемы устройства вероятностного прогнозирования.

Устройство активной защиты и обеспечения технической готовности элементов распределенной локальной вычислительной сети в условиях внешних деструктивных воздействий, показанное на Фиг.1, содержит: анализатор параметрических отказов и сбоев 1, измеритель напряженности поля 2, управляющая плата с внешним запуском 3, состоящая из блока коммутации (БК) 3.1, электронно-перепрограммируемого постоянного запоминающего устройства (ЭППЗУ) 3.2, устройства вероятностного прогнозирования (УВП) 3.3.

На фиг.1 обозначено:

1. Анализатор параметрических отказов и сбоев;

2. Измеритель напряженности поля (ИНП);

3. Управляющая плата с внешним запуском (УПВЗ):

3.1. Блок коммутации (БК);

3.2. Электронно-перепрограммируемое постоянное запоминающее устройство (ЭППЗУ);

3.3. Устройство вероятностного прогнозирования.

4. Распределенная ЛВС:

4.1...4.N. ЭВМ

5. Пользователь.

Анализатор параметрических отказов и сбоев представлен на Фиг.2,где обозначено:

1.1 Первый пороговый блок;

1.2 Формирователь импульса;

1.3 Первый элемент задержки;

1.4 Первый инвертор;

1.5 Первый элемент И;

1.6 Второй элемент ИЛИ;

1.7 Дифференцирующий элемент;

1.8 Четвертый элемент И;

1.9 Первый триггер;

1.10 Третий элемент И;

1.11 Второй инвертор;

1.12 Второй элемент задержки;

1.13 Формирователь паузы;

1.14 Шестой элемент И;

1.15 Третий триггер;

1.16 Четвертый триггер;

1.17 Второй счетчик;

1.18 Генератор импульсов;

1.19 Первый делитель частоты;

1.20 Второй элемент И;

1.21 Первый элемент ИЛИ;

1.22 Первый счетчик;

1.23 Переключатель;

1.24 Регистр;

1.25 Пятый элемент И;

1.26 Третий счетчик;

1.27 Второй триггер;

1.28 Седьмой элемент И;

1.29 Пятый триггер;

1.30 Восьмой элемент И;

1.31 Четвертый счетчик;

1.32 Селектор данных;

1.33 Третий элемент ИЛИ;

1.34 Генератор тактовых импульсов;

1.35 Пятый счетчик;

1.36 Второй пороговый блок;

1.37 Третий инвертор;

1.38 Третий элемент задержки;

1.39 Девятый элемент И;

1.40 Четвертый элемент задержки;

1.41 Четвертый элемент ИЛИ;

1.42 Счетчик импульсов по модулю N;

1.43 Блок ячеек памяти;

1.44 Второй делитель частоты;

1.45 Десятый элемент И;

1.46 Шестой счетчик импульсов;

1.47 Седьмой счетчик импульсов;

1.48 Первый вычитатель;

1.49 Восьмой счетчик импульсов;

1.50 Второй вычитатель;

1.51 Девятый счетчик импульсов;

1.52 Табло отображения;

1.53 Десятый счетчик импульсов;

1.54 Пятый элемент ИЛИ;

1.55 Формирователь импульсов;

1.56 Третий делитель частоты;

1.57 Одиннадцатый счетчик импульсов;

1.58 Четвертый инвертор;

1.59 Одиннадцатый элемент И;

1.60 Двенадцатый счетчик импульсов.

Измеритель напряженности поля (ИНП) 2 - известное устройство и предназначено для измерения среднеквадратических значений напряженности электрической и магнитной составляющих электромагнитного поля (ЭМП) сверхвысокой частоты (СВЧ) в дальней зоне источников излучения в режимах непрерывной генерации, амплитудной, частотной и импульсной модуляции. Как вариант может быть выполнен на базе ИНП П3-21 по схеме, представленной на Фиг 3. Более подробно состав и принцип действия ИНП П3-21 описан в [4] (стр.14-17, 45-48, 55).

На фиг.3 обозначены:

2.1 Антенна-преобразователь;

2.2 Фильтр нижних частот;

2.3 Преобразователь аналого-цифровой;

2.4 Устройство управления;

2.5 Счетчик электрической величины;

2.6 Индикатор.

Блок коммутации 3.1 - известное устройство и предназначено для заблаговременного переключения пользователя на ЭВМ, не подвергающуюся воздействию. Он также обеспечивает соединение измерителя напряженности поля с ЭППЗУ. Как вариант может быть выполнен на базе коммутатора KVM-1600 по схеме, представленной на Фиг.4. Более подробно состав и принцип действия KVM-1600 описан в [5].

На фиг.4 обозначены:

3.1.1 Конвертор интерфейса;

3.1.2 Сетевая карта;

3.1.3 Кнопочный переключатель;

3.1.4 Микроконтроллер;

3.1.5 Дешифратор;

3.1.6 Кросскоммутирующая матрица.

Электронно-перепрограммируемое постоянное запоминающее устройство 3.2 известное устройство [6] (стр.255-259) и предназначено для хранения опорных эталонных значений напряженности электрического поля, а также напряженности электрического поля, приводящее к сбою и отказам ЭВМ. Как вариант может быть выполнено на базе микросхемы AT28BV64B [7] (стр.(1-17)), представленной на Фиг.5.

Устройство вероятностного прогнозирования 3.3 - известное устройство [8] (стр.158-159 рис.17) и предназначено для определения и сигнализации вероятности выхода (невыхода) диагностического параметра за допустимые пределы в определенный (заданный) момент времени, а также сигнализации работающей (основной или резервной) в данный момент времени ЭВМ. Как вариант, УВП может быть выполнен по схеме, представленной на Фиг.6. Включает в себя блок коммутации и измерения (БКИ) 3.3.1, блок памяти (БП) 3.3.2, блок весовых коэффициентов (БВК) 3.3.3, блок вычисления вероятностных характеристик априорной информации (БВ1) 3.3.4, блок вычисления условных апостериорных вероятностей (БВ2) 3.3.5, блок коррекции результатов (БКР) 3.3.6, блоки индикации (БИ) 3.3.7 и управления (БУ) 3.3.8.

Введение в прототип новых отличительных признаков позволяет устройству расширить класс решаемых задач и обеспечить непрерывность предоставления информационных услуг абонентам ЛВС за счет мониторинга электромагнитной обстановки и определения причин возникновения отказов и сбоев.

Проведенный анализ уровня техники позволил установить, что аналоги, тождественные признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна». Введенные отличительные признаки - ИНП и УПВЗ в них не встречаются. Следовательно, заявляемое устройство удовлетворяет критерию «изобретательский уровень». Промышленная применимость введенных элементов обусловлена наличием элементной базы, на основе которой они могут быть выполнены.

Устройство активной защиты и обеспечения технической готовности элементов распределенной локальной вычислительной сети в условиях внешних деструктивных воздействий работает следующим образом.

С выхода ИНП мгновенное значение напряженности электрического поля в цифровом виде поступает на вход БК управляющей платы с внешним запуском. С выхода БК сигнал поступает на ЭППЗУ, где записывается в таблицу в виде 4-разрядного двузначного кода в качестве опорного эталонного значения Еэт, при котором функционирование ЭВМ и ЛВС осуществляется в режиме, не приводящем к сбоям и отказам. Таким образом, в ЭППЗУ в качестве эталонного значения напряженности электромагнитного поля записывается первое измеренное значение напряженности электромагнитного поля, не приводящее к сбоям и отказам. В таблице ЭППЗУ также хранятся заранее заданные расчетные первые минимальные значения напряженности электрического поля Emin, при которых отказы и сбои на ЭВМ и ЛВС не возникают и первые максимальные значения напряженности Emax, при которых возникают отказы и сбои. Со второго выхода ЭППЗУ значение опорного эталонного Еэт и последующие измеренные значения напряженности электрического поля Еизм поступают на первый вход УВП. ЭППЗУ связан с блоком ячеек памяти анализатора параметрических отказов и сбоев. В случае возникновения отказа сигнал об отказе с блока ячеек памяти анализатора параметрических отказов и сбоев поступает в ЭППЗУ. С ЭППЗУ сигнал об отказе поступает на вход блока управления БУ 3.3.8 через блок коммутации и измерения БКИ 3.3.1. Измерив значение напряженности электромагнитного поля, получив информацию, что это отказ и напряженность критическая Екр для работы системы, БКИ коммутирует ее на вход БУ 3.3.8, после чего БУ 3.3.8 дает команду на считывание и запись Екр в блок памяти БП 3.3.2 УВП реальной величины напряженности электрического поля, приводящей к отказам и сбоям ЭВМ.

Таким образом, осуществляется постоянный мониторинг электромагнитной обстановки и определение возможности возникновения отказов. Со второго выхода ЭППЗУ значение опорного эталонного Еэт и последующие измеренные значения напряженности электрического поля Еизм поступают на первый вход УВП.

Устройство вероятностного прогнозирования 3.3 непрерывно оценивает изменяющиеся параметры. На первом этапе работы УВП 3.3 в блок памяти, в котором также хранится значение напряженности электрического поля, приводящее к отказу ЭВМ, с ЭППЗУ поступает и записывается опорное эталонное значение напряженности электрического поля Еэт. Блок памяти 3.3.2 с помощью блока коммутации и измерения 3.3.1 сравнивает значение напряженности электрического поля, поступающее с ЭППЗУ, с заранее заданным расчетным первым минимальным значением напряженности электрического поля Emin, не приводящим к отказам и сбоям ЭВМ и первым максимальным значением напряженности Еmax, приводящим к отказам и сбоям. Полученные значения поступают в ячейки памяти блока памяти 3.3.2, а также умножаются на коэффициенты веса блока 3.3.3. Далее с помощью блоков вычисления вероятностных характеристик априорной информации БВ1 3.3.4 и блока вычисления условных апостериорных вероятностей БВ2 3.3.5 оценивается техническое состояние и осуществляется прогнозирование времени возникновения отказа в ЭВМ, т.е. время (tупрежд) с заданной вероятностью, в течение которого ЭВМ будет находиться в работоспособном состоянии. Если значение электрической напряженности электромагнитного поля стремится к величине, превышающей допустимые пределы (Екр>1,5 В/м), то блок индикации 3.3.7 выдает сигнализацию о вероятности появления отказа в ЭВМ и минимальное время (Tmin) сохранения им работоспособности, которое соответствует отрезку времени до первого достижения границы допуска измеряемым параметром. При этом блок управления 3.3.8 с выхода 3 устройства вероятностного прогнозирования 3.3 выдает управляющий сигнал «УПР-1» на БК для переключения пользователя с подвергающейся воздействию ЭВМ в составе распределенной ЛВС на ЭВМ, не подверженную воздействию. Одновременно блок индикации 3.3.7 включает сигнализацию, а на передней панели блока коммутации УПВЗ появляется световая сигнализация о регистрации произошедших переключений.

Если уровень напряженности электрического поля остается между заранее заданными первым минимальным Еmin и первым максимальным значениями Еmax, наступает второй этап работы. УВП 3.3 сравнивает мгновенное значение напряженности электрического поля, выдаваемое ИНП, с заранее заданным вторым минимальным значением Еmin2, соответствующим значению напряженности электрического поля, при котором осуществляется нормальное функционирование ЭВМ, и заранее заданным вторым максимальным значением Еmax2, соответствующим значению напряженности электрического поля, при котором происходит отказ или сбой. Соответственно оценка технического состояния и прогнозирование появления отказа ЭВМ осуществляется аналогично предыдущему этапу. В случае, если устройство вероятностного прогнозирования 3.3 определяет вероятность выхода в определенный момент времени мгновенного значения напряженности электрического поля за допустимые пределы, т.е. ниже заранее заданного второго минимального значения или выше заранее заданного второго максимального значения, вначале выдается управляющий сигнал с выхода на БК о сигнализации возможного отказа ЭВМ, а затем по окончании времени Тmin блок коммутации 3.1 с помощью блока управления 3.3.8 УВП также осуществляет переключение на ЭВМ, не подверженную воздействию. Кроме этого, аналогично первому этапу работы, блок индикации 3.3.7 включает сигнализацию, а блок коммутации УПВЗ выдает управляющий сигнал на табло отображения анализатора параметрических отказов и сбоев о регистрации произошедших переключений.

При соответствии на данном этапе диагностируемых параметров норме блок индикации и табло отображения выдают информацию о сохранении локально-вычислительной сетью работоспособного состояния, а блок управления 3.3.8 вновь переводит устройство вероятностного прогнозирования 3.3 на первый этап работы. Конец работы.

В ходе работы данного устройства осуществляется процесс диагностирования технического состояния ЭВМ в составе распределенной ЛВС. УПВЗ осуществляет постоянный опрос анализатора параметрических отказов о состоянии диагностируемой аппаратуры. В случае отказа сигнал об его возникновении с блока ячеек памяти анализатора параметрических отказов поступает на ЭППЗУ, который дает команду на запись Екр в блок памяти УВП.

Таким образом осуществляется постоянный мониторинг электромагнитной обстановкой и возможности возникновения отказов, а также постоянная адаптация предлагаемого устройства к изменению электромагнитной обстановки. Применение разработанного устройства позволит обеспечить непрерывность предоставления информационных услуг абонентам распределенной ЛВС.

Оценка эффективности проведена путем сравнения минимально допустимого времени переключения пользователя на ЭВМ, не подвергающейся воздействию электромагнитного импульса, по отношению к времени отключения пользователя от ЭВМ, подвергающейся данному воздействию. В ситуации выхода из строя ЭВМ, подверженной воздействию ЭМИ, время переключения пользователя на другую ЭВМ будет равняться сумме временных интервалов воздействия ЭМИ на ЭВМ, определения выхода ЭВМ из строя и переключения пользователя на другую ЭВМ.

Время отключения пользователя от ЭВМ, подвергающейся воздействию ЭМИ, получаемое при применении предлагаемого устройства будет равняться времени переключения пользователя на ЭВМ, не подвергающейся данному воздействию. Таким образом, выигрыш по времени при применении предлагаемого устройства составит величину, равную сумме временных интервалов воздействия ЭМИ на ЭВМ и определения выхода ЭВМ из строя, при условии равенства времен переключения пользователя на ЭВМ, не подвергающейся воздействию электромагнитного импульса для предлагаемого и существующего устройств.

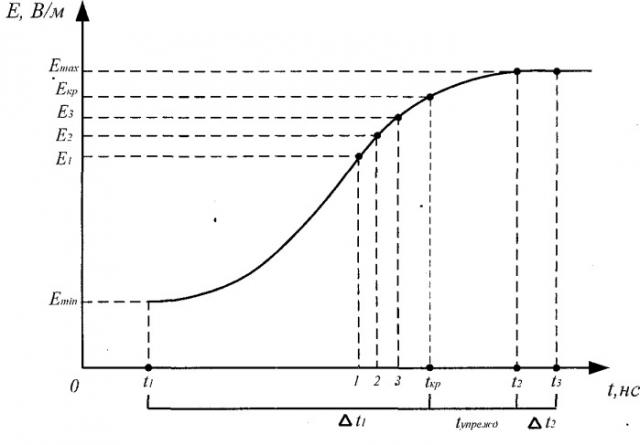

Оценку эффективности проведем, используя временную модель данного воздействия, которая поясняется графиком нарастания напряженности электрического поля ЭМИ, представленном на рисунке 1 [9].

Рисунок 1 - График нарастания напряженности электрического поля ЭМИ

На графике введены следующие обозначения:

Δt1=t2-t1 - интервал нарастания амплитуды Е электрической напряженности ЭМИ (нс);

Δt2=t3-t2 - интервал воздействия ЭМИ на ЭВМ (нс);

Таким образом, при применении прототипа время отключения пользователя от ЭВМ будет рассчитываться по следующей формуле:

где Δt3 - время определения выхода из строя ЭВМ (определяется справочными данными по времени возникновения отказа полупроводниковых элементов и интегральных микросхем при воздействии ЭМИ наносекундной длительности [9];

Δt4 - время переключения пользователя на ЭВМ, не подвергающуюся воздействию электромагнитного импульса (определяется справочными данными по времени переключения конкретного типа блока коммутации [5]).

При применении предлагаемого устройства время отключения пользователя от ЭВМ, подвергающейся воздействию ЭМИ, будет равняться времени переключения пользователя на ЭВМ, не подвергающейся данному воздействию по следующим причинам. На интервале Δt1(t1, t2, t3) устройством вероятностного прогнозирования 3.3 по точкам осуществляется прогнозирование нарастания амплитуды электрического поля ЭМИ до критического значения Екр и определение времени упреждения tупрежд. (рисунок 1). Данные прогнозирования в УВП сравниваются с Екр и при Е≥Екр блок коммутации 3.1 осуществляет переключение абонента на ЭВМ, не подвергающуюся воздействию, то есть

Таким образом, эффективность применения предлагаемого устройства вычисляется следующим образом

Оценку эффективности проведем для одного из типичных вариантов воздействия ЭМИ на ЭВМ [8] со следующими исходными данными [10, 11]:

Δt2=5нс

Δt3=18 мкс

Δt4=10 мкс

Проведя соответствующие расчеты в программе MathCAD эффективность применения предлагаемого устройства будет равна:

Источники информации

1. Анализатор параметрических отказов. Патент SU 1405075 A1, G06F 15/46, 23.06.88 г.

2. Положительное решение о выдаче патента на изобретение «Анализатор параметрических отказов и сбоев», №2004104978 от 9.09.2005 г.

3. Шубинский И.Б. и др. Активная защита от отказов управляющих модульных вычислительных систем. - С.-Пб.: Наука, 1993. - 284 с.

4. Измеритель напряженности поля ПЗ-21. Техническое описание и инструкция по эксплуатации 2.741.010 ТО.

5. PLANET Technology Corp. KVM-1600 16-port KVM Switch with OSD and Daisy Chain., Min Chuan Road, Hsin Tien, Taipei, Taiwan, R.O.C. 11F, No.96. http://www.planet.com.tw.

6. Токхейм Р. Основы цифровой электроники. Пер. с англ. - М.: Мир, 1988. - 392 с.

7. Atmel Corporation. AT28BV64B 64 К (8К×8) Battery-Voltage Parallel EEPROM with Page Write and Software Data Protection. 2005 www.atmel.com/literature.

8. Технические средства диагностирования: Справочник / В.В.Клюев и др. Под общ. ред. В.В.Клюева. - М.: Машиностроение, 1989. - 672 с, ил.

9. Иванов В.А., Двилянский А.А. Обоснование критерия и показателей функционального поражения ЭВМ. - М.: Телекоммуникации, №3, 2005.- С.3-8.

10. Цифровые и аналоговые интегральные микросхемы: Справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред. С.В.Якубовского. - М.: Радио и связь, 1990. - 496 с. ил.

11. Терещук Р.М., Терещук К.М., Седов С.А. Полупроводниковые приемно-усилительные устройства: Справочник радиолюбителя. - 4-е изд. - Киев: Наукова думка, 1989. - С.800.

Устройство обеспечения активной защиты и технической готовности элементов распределенной локальной вычислительной сети (ЛВС) в условиях внешних деструктивных воздействий (электромагнитного импульса), состоящее из анализатора параметрических отказов и сбоев, который содержит первый пороговый блок, формирователь импульса, первый элемент задержки, первый инвертор, первый элемент И, второй элемент ИЛИ, дифференцирующий элемент, четвертый элемент И, первый триггер, третий элемент И, второй инвертор, второй элемент задержки, формирователь паузы, шестой элемент И, третий триггер, четвертый триггер, второй счетчик, генератор импульсов, первый делитель частоты, второй элемент И, первый элемент ИЛИ, первый счетчик, переключатель, регистр, пятый элемент И, третий счетчик, второй триггер, седьмой элемент И, пятый триггер, восьмой элемент И, четвертый счетчик, при этом вход первого порогового блока является информационным входом анализатора, а выход порогового блока соединен с единичным входом третьего триггера, входом первого элемента задержки, нулевым входом первого триггера, третьим входом третьего элемента И, входом сброса формирователя пауз, входом второго инвертора и входом запуска формирователя импульса, выход которого соединен с входом первого инвертора, выход которого подключен к входу дифференцирующего элемента, первому входу седьмого элемента И, входу сброса четвертого счетчика и второму входу первого элемента И, первый вход которого соединен с выходом первого элемента задержки, а выход - со вторым входом второго элемента ИЛИ, выход которого подключен к единичному входу четвертого триггера, инверсный выход которого связан с третьим входом восьмого элемента И, а прямой выход соединен с первым входом пятого элемента ИЛИ, выход которого подключен к счетному входу второго счетчика и второму входу второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к суммирующему входу первого счетчика, выход генератора импульсов соединен с входом первого делителя частоты, выход которого соединен с первым входом второго элемента И и вторым входом седьмого элемента И, выход которого соединен с входом сложения четвертого счетчика, выход которого соединен с нулевым входом пятого триггера, единичный вход которого соединен с первым входом второго элемента ИЛИ и выходом третьего элемента И, второй вход которого, а также нулевой вход четвертого триггера и вход сброса формирователя импульса связаны с прямым выходом третьего триггера, нулевой вход которого подключен к выходу шестого элемента И, первый и второй входы которого подключены к выходам второго элемента задержки и формирователя паузы соответственно, первый вход третьего элемента И соединен с прямым выходом первого триггера, единичный вход которого подключен к выходу четвертого элемента И, первый вход которого связан с выходом дифференцирующего элемента, а второй вход четвертого элемента И, а также вход второго элемента задержки и вход запуска формирователя паузы соединены с выходом второго инвертора, первый и второй информационные выходы переключателя связаны с вторым выходом первого элемента ИЛИ и выходом вычитания первого счетчика, а информационный вход переключателя - с выходом пятого элемента И, третий выход первого элемента ИЛИ и вход вычитания четвертого счетчика соединены с выходом восьмого элемента И, первый вход которого подключен к прямому выходу пятого триггера, а второй вход подключен к инверсному выходу второго триггера, первый установочный вход третьего счетчика связан с выходом регистра, выход обнуления третьего счетчика соединен с входом считывания регистра и с нулевым входом второго триггера, прямой выход второго триггера подключен к входу пятого элемента И, генератор тактовых импульсов подключен к суммирующему входу пятого счетчика импульсов, выход которого подключен к первому входу третьего элемента ИЛИ, входу четвертого элемента задержки и первому входу четвертого элемента ИЛИ, выход которого соединен со входом счетчика импульсов по модулю N, выход которого соединен с управляющим входом блока ячеек памяти, выход которого соединен с табло отображения, селектор данных, выход которого соединен со входом первого порогового блока, второго порогового блока, выход которого соединен с входом третьего инвертора, выход которого соединен с входом третьего элемента задержки, выход которого соединен с первым входом девятого элемента И, второй вход которого связан с выходом четвертого элемента задержки, а выход девятого элемента И соединен со вторым входом четвертого элемента ИЛИ и вторым входом третьего элемента ИЛИ, выход которого соединен с управляющим входом селектора данных, информационные входы блока ячеек памяти соединены с первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым счетчиками импульсов, регистром, первым, вторым, третьим, четвертым, пятым триггерами, формирователем паузы, формирователем импульсов, второй делитель частоты, вход которого соединен с выходом первого порогового блока, а выход с первым входом десятого элемента И, второй вход которого соединен с выходом первого порогового блока и суммирующим входом седьмого счетчика, выход десятого элемента И связан с суммирующим входом шестого счетчика, выход которого соединен с первым входом первого вычитателя, второй вход которого соединен с выходом первого счетчика, а выход с суммирующим входом восьмого счетчика, выход обнуления седьмого счетчика соединен с первым входом второго вычитателя, второй вход которого подключен к выходу обнуления второго счетчика, а выход второго вычитателя связан с суммирующим входом девятого счетчика, выход которого подключен к первому входу одиннадцатого элемента И и суммирующему входу десятого счетчика, выход которого соединен с вторым входом пятого элемента ИЛИ, формирователь импульсов, выход которого соединен с входом третьего делителя частоты, выход которого связан с суммирующим входом одиннадцатого счетчика импульсов, выход которого подключен к обнуляющему входу двенадцатого счетчика импульсов и входу четвертого инвертора, выход которого соединен со вторым входом одиннадцатого элемента И, отличающийся тем, что в него введены измеритель напряженности поля (ИНП), управляющая плата с внешним запуском (УПВЗ), состоящая из блока коммутации (БК), электронно-перепрограммируемого постоянного запоминающего устройства (ЭППЗУ), устройства вероятностного прогнозирования (УВП), при этом выход ИНП соединен с первым входом БК, второй выход которого соединен с первым входом ЭППЗУ, второй выход которого соединен с первым входом УВП, четвертый вход БК соединен с выходом УВП, третий вход/выход ЭППЗУ соединен с блоком ячеек памяти анализатора параметрических отказов и сбоев, пользователь соединен с шестым вход/выходом БК, выходы которого (от седьмого...до N-го) соединены с входами ЭВМ распределенной ЛВС соответственно, выходы каждой из ЭВМ распределенной ЛВС соединены со входами анализатора параметрических отказов и сбоев.