Способ и устройство обработки сигналов линий связи по модели сигнала и перепрограммируемым электрическим схемам

Иллюстрации

Показать всеИзобретение относится к области радиотехники, цифровой и вычислительной техники и может быть использовано при приеме, демодуляции и обработке сигналов спутниковых и радиорелейных линий связи. Техническим результатом является расширение функциональных возможностей. Для этого сигнал принимают, демодулируют, преобразуют в цифровую форму, синтезируют модель обрабатываемого сигнала, выбирают номенклатуру и ресурс программируемых логических интегральных схем (ПЛИС), ПЗУ, ОЗУ, контроллеров, микропроцессоров, средств вычислительной техники, других перепрограммируемых или программно-управляемых электрорадиоизделий (ЭРИ) и создают схему соединений; конфигурируют ЭРИ по выполняемым функциям в сигнале, создают загрузочный модуль контролируемого сигнала, проверяют работоспособность полученной схемы методом моделирования или на реальном сигнале, в случае неудачи определяют локальный неработоспособный участок перепрограммируемых ЭРИ и корректируют программно схему, в случае успеха - заносят программу в банк электрических схем, по каждому новому сигналу повторяют вышеуказанные операции и формируют банк загрузочных модулей под различные сигналы, что позволяет автоматически настраиваться на любой сигнал при повторном выходе на него. Для обработки любого сигнала, имеющегося в банке загрузочных модулей, достаточно выбрать нужный загрузочный модуль и запрограммировать ЭРИ. Двухканальное приемно-демодулирующее устройство содержит последовательно соединенные радиоприемное устройство, блок аналого-цифрового преобразования, набор N-когерентных цифровых демодуляторов помехоустойчивые декодеры, а также интерфейс шины VME, контроллер и персональную электронно-вычислительную машину. Все устройства кроме персональной электронно-вычислительной машины комплексируются в конструктиве типа Евроблок - выполнены на перепрограммируемых или электронно-управляемых электрорадиоизделиях. 2 н.п. ф-лы, 3 ил.

Реферат

Изобретение относится к области радиотехники, цифровой и вычислительной техники и может быть использовано при приеме, демодуляции и обработке сигналов спутниковых и радиорелейных линий связи.

Бурное развитие цифровых методов передачи информации в спутниковых и радиорелейных линиях связи привело к многообразию преобразований сигналов на передающей стороне, таких как:

- поэтапное формирование групповых потоков различного уровня иерархического уплотнения, начиная от телеграфных, факсимильных передач до IV уровня иерархического уплотнения [Л.С. Левин и др. «Цифровые системы передачи информации», М.: Радио и связь, 1982 - 1],

- помехоустойчивое кодирование систематическими, несистематическими сверточными кодами и турбокодами;

- аддитивное и мультипликативное скремблирование;

- дифференциальное кодирование;

- перемежение цифровых потоков;

- кодирование кодами Рида-Соломона;

- фазовая модуляция с различными видами (ФМ2, ФМ4, ФМ4С, ФМ8, КАМ16, КАМ32, КАМ64, КАМ128, КАМ256);

- различные промежуточные частоты;

- различные высокие частоты по восходящей и нисходящей линиям. Каждое из этих преобразований имеет несколько степеней свободы, преобразования могут выполняться в различной последовательности, отдельные преобразования могут отсутствовать, что подтверждается многообразием рекомендаций МККТТ и ITU.

До недавних пор под каждую рекомендацию МККТТ и ITU разрабатывалась своя специализированная аппаратура [1, стр.185-200].

Появление в массовом производстве перепрограммируемых логических интегральных схем (ПЛИС) позволило строить аппаратуру обработки цифровых сигналов по моделям сигнала и перепрограммируемым схемам электрическим.

Так в [патент №2220498 от 27.12.2004 г. «Способ обработки цифровых потоков по модели сигнала и перепрограммируемым схемам электрическим» - 2] предложен способ, взятый за прототип, при котором сигнал демодулируют, преобразуют в цифровой поток и синтезируют модель сигнала, по модели сигнала создают электрическую схему устройства обработки цифровых потоков и определяют ресурс и номенклатуру перепрограммируемых логических интегральных схем, необходимых для ее реализации, создают загрузочный модуль под контролируемый сигнал, проверяют работоспособность полученной схемы методом моделирования или на реальном сигнале в случае создания макета, при этом в случае неудачи определяют локальный неработоспособный фрагмент перепрограммируемых логических интегральных схем и корректируют программно схему и загрузочный модуль, а в случае успеха заносят программу в банк электрических схем, выполненных в виде загрузочных модулей, причем по каждому новому сигналу повторяют вышеуказанные операции и формируют банк загрузочных модулей под различные сигналы.

Большим недостатком способа является возможность создания ограниченного круга устройств по обработке только цифровых потоков, в пределах возможностей ПЛИС, т.к. на них можно строить элементы цифровых схем.

В [патент на полезную модель №41217 от 10.10.2004 г. «Многоканальное приемно-демодулирующее устройство фазоманипулированных сигналов и сигналов квадратурной амплитудной манипуляции - 3] приведено приемно-демодулирующее устройство, принятое за прототип, содержащее последовательно соединенные радиоприемное устройство (РПУ), блок аналого-цифрового преобразования и набор N-цифровых демодулирующих устройств, входы которых подключены к выходу блока аналого-цифрового преобразователя.

Недостатками этого устройства являются малые функциональные возможности, в частности отсутствие средств помехоустойчивого декодирования, дескремблирования, деперемежения, декодирования кодов Рида-Соломона, отсутствие функций управления и взаимодействия.

Целью изобретения является расширение функциональных возможностей способа и устройства за счет расширения номенклатуры используемых перепрограммируемых микросхем и средств вычислительной техники.

Основанием для этого является появление помимо ПЛИС широкого круга перепрограммируемых или программно перестраиваемых электрорадиоизделий (ЭРИ), таких как:

- перепрограммируемые постоянные запоминающие устройства (ПЗУ);

- оперативные запоминающие устройства (ОЗУ);

- контроллеры;

- микропроцессоры;

- синтезаторы частоты;

- управляемые гетеродины;

- средства вычислительной техники, в том числе и персональные электронно-вычислительные машины.

Для достижения указанной цели предлагается способ, при котором сигнал принимают, демодулируют, преобразуют в цифровой поток и синтезируют модель сигнала.

Согласно изобретению по модели сигнала создают электрическую схему устройства обработки сигналов и определяют ресурс и номенклатуру перепрограммируемых логических интегральных схем, ОЗУ, ПЗУ, микропроцессоров, контроллеров, средств вычислительной техники и других перепрограммируемых или программно-управляемых электрорадиоизделий, необходимых для ее реализации, создают загрузочный модуль под контролируемый сигнал с выполнением операций от приема сигнала до выделения канальной информации, проверяют работоспособность полученной схемы обработки сигналов линий связи в тракте от приема до выделения канальной информации методом моделирования или на реальном сигнале в случае создания макета, при этом в случае неудачи определяют локальный неработоспособный фрагмент перепрограммируемых или программно-управляемых ЭРИ и корректируют программно схему и загрузочный модуль, а в случае успеха заносят программу обработки сигналов линий связи в банк электрических схем, выполненных в виде загрузочных модулей, причем по каждому новому сигналу повторяют вышеуказанные операции и формируют банк загрузочных модулей под различные сигналы, что позволяет автоматически настраиваться на сигнал при повторном выходе на него, в котором дополнительно при создании электрических схем устройств обработки сигналов определяют ресурс, помимо ПЛИС, также перепрограммируемых ПЗУ, ОЗУ, микропроцессоров, контроллеров, средств вычислительной техники и других перепрограммируемых или программно-управляемых ЭРИ.

Устройство содержит последовательно соединенные радиоприемное устройство и блок аналого-цифрового преобразования и набор N-когерентных цифровых демодуляторов, входы которых подключены к выходам блока аналого-цифрового преобразования. Согласно изобретению в каждое демодулирующее устройство введены мезонин помехоустойчивого декодирования, включающий в свой состав последовательно соединенные помехоустойчивый декодер, дескремблер, деперемежитель, декодер кодов Рида-Соломона и дескремблер аддитивный, а также интерфейс шины VME, контроллер типа MVME 2700, и персональная электронно-вычислительная машина с блоком программного обеспечения, при этом входы мезонина помехоустойчивого декодирования подключены к выходам когерентного цифрового демодулятора, а входы/выходы приемно-демодулирующего модуля, контроллера типа MVME 2700, интерфейса шины VME подключены к шине VME, вторые входы/выходы контроллера типа MVME 2700 подключены к выходам/входам персональной электронно-вычислительной машины. При этом все устройства кроме персональной электронно-вычислительной машины комплексируются в конструктиве Евроблок (крейт).

Сочетание отличительных признаков и свойства предлагаемого способа и устройства соответствует критерию новизны и изобретательского уровня.

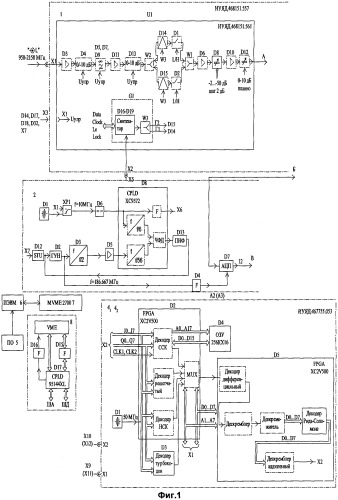

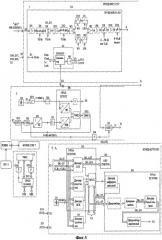

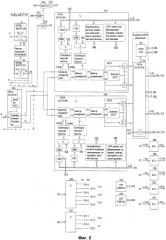

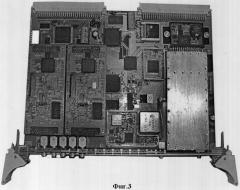

На фиг.1 и 2 приведена функциональная схема одного из устройств (двухканальное приемно-демодулирующее устройство - ПДМ-2К), реализующих предлагаемый способ, на фиг.3 - фотография макета ПДМ-2К.

По предлагаемому способу осуществляют следующую последовательность операций:

- сигнал принимают и преобразуют в промежуточную частоту, определяют частоту настройки гетеродина РПУ;

- определяют параметры сигнала по промежуточной частоте, такие как полоса частот, скорость передачи информации, вид фазовой модуляции;

- по этим данным сигнал демодулируют, преобразуют в цифровой поток;

- синтезируют модель сигнала (определяют местоположение и структуру синхросигналов, длительность кадра-суперкадра, тип помехоустойчивого кода, скремблера, перемежителя, местоположение служебных и компонентных потоков и их количество, команды стаффинга и бит стаффинга, вид импульсной модуляции, при этом, если имеется спецификация на данный сигнал, то он и являются моделью сигнала, если спецификации нет, то данные о сигнале формируются по результатам анализа сигнала);

- определяют номенклатуру и ресурс необходимых для всех контролируемых сигналов перепрограммируемых или программно-управляемых ЭРИ (ПЛИС, ОЗУ, ПЗУ, контроллеров, микропроцессоров, средств вычислительной техники и др. перепрограммируемых или программно-управляемых ЭРИ) и создают электрическую схему их соединений;

- по модели сигнала программируют ЭРИ по выполняемым функциям в контролируемом сигнале, т.е. создают загрузочный модуль под обрабатываемый сигнал с выполнением операций от приема сигнала до выделения канальной информации;

- проверяют работоспособность полученной схемы обработки сигналов линий связи в тракте от приема до выделения канальной информации методом моделирования или по реальному сигналу при создании макета, в случае неудачи определяют локальный неработоспособный участок перепрограммируемых или программно-управляемых ЭРИ и корректируют программно схему и загрузочный модуль, а в случае успеха заносят программу обработки сигналов линий связи в банк электрических схем под данный сигнал в виде загрузочного модуля;

- по каждому новому сигналу повторяют вышеуказанные операции и создают банк электрических схем под каждую модель сигнала, что позволяет автоматически настраиваться на сигнал при повторном выходе на него.

Использование предлагаемого способа с широкой номенклатурой перепрограммируемых или программно-управляемых ЭРИ позволяет создать перепрограммируемые или программно-управляемые электрические схемы целого ряда устройств; РПУ; демодуляторов ФМ и КАМ сигналов; помехоустойчивых декодеров практически всех существующих систематических и несистематических декодеров, декодеров турбокодов; дескремблеров; деперемежителей; декодеров кодов Рида-Соломона, демультиплексоров сигналов различного уровня иерархического уплотнения; каналовыделяющих устройств; устройств обработки каналов индивидуальной и общей сигнализации; устройств отбора информации по техническим признакам; устройств внутриканальной демодуляции, а также устройств анализа системных и структурных параметров контролируемых сигналов.

При этом эти устройства позволяют программно адаптироваться к изменяющейся сигнальной среде и появлению сигналов с новой структурой без физического изменения схем электрических в пределах заложенного ресурса перепрограммируемых ЭРИ.

Предлагаемое устройство (ПДМ-2К) содержит последовательно соединенные РПУ ПД-140-1 и блок аналого-цифрового преобразования 2, к выходам которого подключены два когерентных цифровых демодулятора 31, 32, выходы которых подключены к соответствующим входам мезонинов помехоустойчивого (ПУ) декодирования 41, 42, включающих в свой состав помимо ПУ декодера последовательно соединенные дескремблер, деперемежитель, декодер кода Рида-Соломона и дескремблер аддитивный, а также последовательно соединенные блок программного обеспечения 5, ПЭВМ 6 и контроллер типа MVME 2700 7, при этом модуль ПДМ-2К, контроллер типа MVME 2700 7 через интерфейс шины VME 8 и шину VME объединены в единую систему управления и взаимодействия.

Загрузочный модуль (ПО 5) через ПЭВМ 6, контроллер MVME 2700 7, шину VME и интерфейс шины VME 8 заносится во все составные части ПДМ-2К.

Устройство работает следующим образом.

Входной сигнал диапазона (950-2150) МГц подается на вход приемника ПД140 1, в котором осуществляется перенос группового сигнала на промежуточную частоту (ПЧ) 140 МГц и его предварительная фильтрация, а также регулировка усиления для обеспечения требуемого уровня сигнала на входе блока аналого-цифрового преобразования (АЦП) 2.

В состав устройства 1 входят:

- преобразователь ПД140 ИУЯД.468151.561 (U1);

- усилители ИУЯД.468732.280 (А1), ИУЯД.468732.281 (А2);

- фильтр на поверхностных акустических волнах (ПАВ) 140-48 (Z1).

Преобразователь U1 работает следующим образом. Входные сигналы в диапазоне частот 950-2150 МГц подаются на усилитель на микросхеме D3 с параметрами, обеспечивающими необходимый коэффициент шума ПД140. Далее по тракту расположены аттенюаторы 0/-10дБ на микросхемах D4 и D13, предназначенные для расширения динамического диапазона преобразователя и совместно с дискретным аттенюатором D8 и плавным D12 обеспечивают необходимую регулировку коэффициента передачи преобразователя. После аттенюатора D4 сигнал поступает на преселектор D5, D7, D9, предназначенный для предварительной фильтрации входных сигналов и обеспечивающий подавление побочных каналов приема. В связи с тем, что преобразователь разработан с одним преобразованием частоты, для дополнительного подавления зеркального канала использован фазовый метод, для чего в преобразователе использованы делитель мощности W2, два смесителя D14 и D15, квадратурные делители мощности W1 по ПЧ и W3 по гетеродину.

Для формирования частот гетеродина, необходимых для преобразования сигналов входного диапазона в диапазон ПЧ, в состав преобразователя входит синтезатор G1 (D16-D19). Для установки частоты настройки преобразователя на синтезатор G1 подается код загрузки от управляющей ПЭВМ 6 по шине VME через интерфейс 8.

Нижнее значение частоты первого гетеродина составляет 1190 МГц при настройке преобразователя на частоту 950 МГц. Верхнее значение частоты гетеродина составляет 2190 МГц при настройке преобразователя на частоту 2050 МГц. Переход с верхней настройки гетеродина на нижнюю происходит на частоте 2050 МГц. Перестройка гетеродина по частоте осуществляется в синтезаторе G1 (D16-D19). При переходе с верхней частоты настройки на нижнюю переключаются выходы смесителей D14 и D15 на квадратурный делитель мощности W1 коммутаторами D1 и D2. Усилители D6, D10, D11 обеспечивают нужный уровень выходного сигнала преобразователя. Управляющее напряжение на преселектор D5, D7, D9, управление аттенюаторами D4, D13, переключение верхней/нижней боковой, управление синтезатором G1 (D16-D19) осуществляются через разъем X1 устройства U1

С целью обеспечения высоких параметров по избирательности в качестве фильтра основной селекции по ПЧ 140 МГц применен фильтр на ПАВ Z1 c полосой 48 МГц. Для обеспечения заданного коэффициента передачи и оптимального согласования фильтра Z1 использованы усилители: А1 - эмиттерный повторитель на входе фильтра Z1 и А2 на выходе фильтра Z1 - усилитель на полевом транзисторе с низким коэффициентом шума. На выходе усилителя А2 установлен согласующий дифференциальный трансформатор, с выхода которого высокочастотный (ВЧ) сигнал подается непосредственно на АЦП 2 (D7) через разъем Х4.

Синтезатор тактовой частоты для АЦП 2 выполнен на микросхемах D1, D6, D8, D12, D13. Частота дискретизации сигнала аналого-цифровым преобразователем 2 составляет 186.667 МГц. Сигнал этой частоты формируется генератором управляемого напряжением (ГУН) D2 и через формирователь парафазного сигнала D4 подается на второй вход АЦП (D7), первый вход которого является входом АЦП 2. Сигнал с D2 через делитель частоты на два D3 и усилитель D5 подается также на микросхему D8. В то же время на D8 через компаратор D6 поступает сигнал опорного генератора D1 с частотой 10 МГц. В ПЛИС D8 реализованы алгоритмы деления частоты на 6 и 56 для сигналов опорного генератора и ГУН D2, соответственно, а также частотно-фазовый дискриминатор (ЧФД). Если частота ГУН D2 не равна в точности 186.667 МГц, то на выходе ЧФД появляется управляющее напряжение, призванное скомпенсировать имеющуюся расстройку по частоте. Сигнал с выхода ЧФД подается на пропорционально-интегрирующий фильтр (ПИФ), выполненный на операционном усилителе (ОУ) D13. Выходной сигнал ОУ суммируется с постоянным напряжением с выхода стабилизатора D12 (для обеспечения требуемого диапазона управляющего напряжения) и подается на управляющий вход ГУН D2.

В схеме АЦП 2 предусмотрена возможность использования внешнего опорного генератора D1, сигнал с которого подается на ПЛИС D8 через разъем X1 и компаратор D6. При этом необходимо выставить джампер ХР1 в соответствующее положение.

С выхода АЦП D7 оцифрованный сигнал в виде 12-разрядных отсчетов поступает на ПЛИС D18, реализующей в себе преобразователь Гильберта и детектор первой АРУ1. С выхода АРУ1 сигнал управления через цифроаналоговый преобразователь (ЦАП) D25 подается на разъем Х3. После преобразователя Гильберта отсчеты синфазного и квадратурного подканалов подаются на два канала цифровой обработки сигнала - демодуляторы 31, 32, выполненные на ПЛИС D19 и D20. ПЛИС D18 выдает также код напряжения преселлектора D5, D7, D9 приемника 1, который загружается в ЦАП D10. Управляющее напряжение преселлектора с ЦАП D10 через ОУ D14 поступает на разъем Х3. Микросхема REF (D11) является источником высокостабильного опорного напряжения для ЦАП D10 и ЦАП D25.

Каждый демодулятор 31, 32 включает в себя квадратурный детектор, полифазный (ПФФ) и оптимальный фильтры, схемы восстановления несущей (СВН) и тактовой частот (СВТ), АРУ2. После квадратурного переноса сигнала на нулевую частоту сигнал поступает в ПФФ. Он позволяет получить требуемую для дальнейшей обработки частоту дискретизации сигнала. После ПФФ сигнал фильтруется в оптимальной полосе. Маска фильтра может перегружаться из внешнего файла. Отфильтрованный сигнал поступает на схему АРУ2, сужающую динамический диапазон сигналов на входе СВН. С выхода АРУ2 сигналы обоих каналов подаются на корректор амплитудно-частотной характеристики (АЧХ) и группового времени запаздывания (ГВЗ), реализованный в ПЛИС D21. Для вычисления и перезагрузки коэффициентов фильтров корректора к нему подключен сигнальный процессор D22. Алгоритм восстановления несущей частоты загружается в ОЗУ D23 и D24.

Откорректированный сигнал каждого канала подается на соответствующий ему модуль декодирования, выполненный в виде мезонина. На выходе каждого декодера 41, 42 формируются сигналы в сопровождении тактовой частоты, которые поступают на ПЛИС D21. Отсюда сигналы подаются либо через формирователи D26, D27 на разъемы передней панели Х14...X18, либо в дифференциальной форме на разъем Х13.

Интерфейс шины VME 8 выполнен на ПЛИС D17 и формирователях D15, D16, обеспечивающих совместимость параметров сигналов, выдаваемых ПЛИС D17, с требованиями шины VME.

На микросхемах D28, D31, D32 выполнены линейные стабилизаторы для питания аналоговых цепей модуля. Импульсные стабилизаторы D29, D30 служат для формирования напряжений питания цифровых цепей схемы.

Мезонин помехоустойчивого декодера 41, 42 ИУЯД. 467755.053 (в дальнейшем - декодер) предназначен для помехоустойчивого декодирования несистематических сверточных кодов, систематических сверточных кодов, решетчатых кодов, кодов Рида-Соломона, блочных турбокодов, а также деперемежения, дифференциального декодирования и дескремблирования.

Декодеры 41, 42 выполнены в виде модулей, устанавливаемых на плату модуля, и выполняют функции:

- декодера несистематических сверточных кодов по алгоритму Витерби;

-декодера систематических сверточных кодов по последовательному алгоритму;

- декодера решетчатых кодов;

- декодера блочных турбокодов;

- дифференциального декодера;

- деперемежителя;

- декодера кодов Рида-Соломона;

- дескремблеров V.35, V.35C и аддитивного.

С выхода демодулятора 31, 32 8-битные мягкие решения синфазного и квадратурного каналов в сопровождении канальной тактовой частоты и удвоенной канальной тактовой частоты через разъем Х2 поступают на ПЛИС ПУ декодера D2. В ПЛИС D2 реализованы декодер несистематических сверточных кодов по алгоритму Витерби, декодер систематических сверточных кодов по последовательному алгоритму, декодер решетчатых кодов, а также мультиплексор. Декодер турбокодов реализован на специализированной микросхеме D3. Тактовую частоту 50 МГц для последовательного декодера и для декодера турбокодов обеспечивает тактовый генератор, реализованы на микросхеме D1. Микросхема статического ОЗУ D4 с организацией 256К×16 используется для хранения таблицы преобразования отсчетов квадратурных каналов в метрики для Trellis декодера. Также микросхема D4 используется для накопления сигнала при автоматическом анализе параметров ПУ кодирования принимаемого сигнала. Выбор нужного декодера и настройка его параметров осуществляется управляющей ЭВМ 6 через контроллер MVME 2700 7 по шине VME 8 и по внутренней шине адреса и данных демодулятора 31, 32 через разъем X1. С выхода ПЛИС D2 декодированный сигнал поступает на ПЛИС D5. В ПЛИС D5 сигнал подвергается дифференциальному декодированию, дескремблированию (V35 или 3.20С), а затем поступает на деперемежитель. Там осуществляется кадровая и суперкадровая синхронизация принимаемого сигнала, а также байтовое деперемежение на глубину 4, 8, 12 или 16 строк. Далее сигнал после деперемежения поступает на декодер кодов Рида-Соломона, также реализованный на ПЛИС D5. Выходной сигнал с декодера Рида-Соломона при необходимости подвергается аддитивному дескремблированию и через разъем Х2 поступает на выход модуля. Напряжения питания декодера +3,3 В и +1,5 В поступают с платы ПДМ-2К через разъем X1.

Построение ПДМ-2К по предлагаемому способу обеспечивает:

- прием сигналов в диапазоне частот 950-2150 МГц и когерентную демодуляцию двух независимых сигналов в полосе 48 МГц и с видами модуляции: ФМ2, ФМ4, ФМ4С, ФМ8, KAM16 в диапазоне скоростей от 1,5 кбит/с до 10 Мбит/с для ФМ2; от 3,0 кбит/с до 20 Мбит/с для ФМ4, ФМ4С; от 4,5 кбит/с до 30 Мбит/с для ФМ8; от 0 кбит/с до 40 Мбит/с для КАМ16;

- помехоустойчивое декодирование несистематических сверточных кодов (НСК) по алгоритму Витерби с «мягким» решением, образованных на основе базового сверточного кода 1/2 типа (171, 133) методом выкалывания с относительными скоростями 1/2, 2/3, 3/4, 5/6, 7/8 в диапазоне скоростей входных потоков до 10 Мбод в соответствии с рекомендациями IESS 308, 309, 310, 312 для видов модуляции ФМ2, ФМ4, ФМ4С;

- помехоустойчивое декодирование систематических сверточных кодов (ССК) по последовательному алгоритму с кодовыми скоростями 1/2, 3/4, 7/8 и кодовым ограничением до 104, в том числе по рекомендации IESS 309 (REV 7), в диапазоне скоростей входных потоков до 10 Мбит/с для видов модуляции ФМ2, ФМ4, ФМ4С;

- помехоустойчивое декодирование турбокодов с относительной скоростью 3/4, 21/44, 5/16 для видов модуляции ФМ2, ФМ4, ФМ4С, ФМ8, КАМ16;

- декодирование каскадных ПУ кодов с перемежением и блоковым кодированием в последовательности (ССК/НСК → перемежитель → блоковый код)

- декодирование каскадных ПУ кодов НСК 1/2, НСК 2/3, НСК 3/4, НСК 5/6, НСК 7/8 с перемежением и блоковым кодированием Рида-Соломона (204,188) с глубиной перемежения 12 по спецификации EN300421;

- декодирование решетчатых кодов (Trellis) с относительными скоростями 2/3,5/6 и 8/9 для сигналов ФМ8 со скоростью до 10 Мбод

- декодирование решетчатых кодов (Trellis) с относительными скоростями 3/4 и 7/8 для сигналов КАМ16 со скоростью до 10 Мбод;

- цифровую фильтрацию сигналов в соответствии со спецификациями IESS 309, IESS 310, EN300421, EN300429;

- коррекцию АЧХ и ГВЗ с глубиной коррекции ±4 символа;

- автоматический и ручной поиск несущей и тактовой частот принимаемых сигналов с программируемым диапазоном и шагом (для тактовой частоты - ТЧ) поиска;

- измерение частоты сигналов восстоновленной несущей и тактовой с точностью не хуже 5·10-5;

- измерение ОСШ и отношения Eb/NO сигналов;

- работоспособность при уровне входного сигнала от минус 50 до минус 100 дБ/Вт;

- формирование сигналов на выходах «С1», «С2», «С3», «С4», «Т» амплитудой не менее 2.4В (ТТЛ) на нагрузке 50 Ом при длине кабеля до 3 м;

- выдачу декодированных сигналов на пользовательский ряд разъема Р2 в формате LVDS;

- инверсию информационных сигналов и сигнала тактовой частоты;

- формирование и вывод на экран монитора частотной панорамы в диапазоне частот от 950 до 2150 МГц;

- формирование и вывод на экран монитора спектра первой, второй, четвертой и восьмой гармоник принимаемого сигнала с центральной частотой от 950 до 2150 МГц;

- измерение амплитудных и частотных параметров сигнала и его гармоник. Непрерывное когерентное накопление спектра;

- формирование и вывод на экран монитора векторных диаграмм принимаемого сигнала;

- вывод на экран монитора АЧХ используемого цифрового фильтра в линейном или логарифмическом масштабе;

- автоматическую настройку на сигнал после его кратковременного пропадания;

- ток потребления по цепям электропитания: «+5 В» - не более 2 А, «+12 В» - не более 1 А, «-12 В» - не более 0.3 А.

Работоспособность макета ПДМ-2К проверена от имитационных и реальных сигналов. Результаты положительные.

Разработка и изготовление по предлагаемому способу модулей демультиплексоров, каналовыделяющих устройств и других модулей обработки позволяет скомплексировать в конструктиве Евроблок (крейт) сквозной тракт обработки сигналов от приема до выделения канальной информации.

1. Способ обработки сигналов линий связи по модели сигнала и перепрограммируемым электрическим схемам, при котором сигнал демодулируют, преобразуют в цифровой поток и синтезируют модель сигнала, отличающийся тем, что перед демодуляцией сигнал принимают, по модели сигнала создают электрическую схему устройства обработки сигналов линий связи и определяют номенклатуру и ресурс перепрограммируемых логических интегральных схем, оперативных запоминающих устройств, постоянных запоминающих устройств, микропроцессоров, контроллеров, синтезаторов частот гетеродина, синтезаторов тактовой частоты, аналого-цифровых преобразователей, помехоустойчивых декодеров, цифроаналоговых преобразователей, полифазных фильтров, аттенюаторов, средств вычислительной техники и других перепрограммируемых или программно-управляемых электрорадиоизделий, необходимых для ее реализации, создают загрузочный модуль под контролируемый сигнал, с выполнением операций от приема сигнала до выделения канальной информации, проверяют работоспособность полученной схемы обработки сигналов линий связи в тракте от приема до выделения канальной информации методом моделирования или на реальном сигнале в случае создания макета, при этом в случае неудачи определяют локальный неработоспособный фрагмент перепрограммируемых или программно управляемых электрорадиоизделий и корректируют программно схему и загрузочный модуль, а в случае успеха заносят программу обработки сигналов линий связи в банк электрических схем, причем по каждому новому сигналу повторяют вышеуказанные операции и формируют банк загрузочных модулей под все сигналы, что позволяет автоматически настраиваться на сигнал при повторном выходе на него.

2. Двухканальное приемно-демодулирующее устройство по предлагаемому способу, содержащее последовательно соединенные радиоприемное устройство и блок аналого-цифрового преобразования, к выходу которого подключены входы двух когерентных цифровых демодуляторов, отличающееся тем, что в каждый когерентный цифровой демодулятор введены последовательно соединенные помехоустойчивый декодер, дескремблер, деперемежитель, декодер кодов Рида-Соломона и дескремблер аддитивный, а также интерфейс шины VME, контроллер типа MVME 2700 и персональная электронно-вычислительная машина с блоком программного обеспечения, при этом входы помехоустойчивого декодера подключены к выходам когерентного цифрового демодулятора, а входы/выходы приемно-демодулирующего модуля, контроллера типа MVME 2700, интерфейса шины VME подключены к шине VME, вторые входы/выходы контроллера типа MVME 2700 подключены к выходам/входам персональной электронно-вычислительной машины, при этом все устройства, кроме персональной электронно-вычислительной машины, комплексируются в конструктиве Евроблок - крейт.