Дифференциальный усилитель с повышенным ослаблением синфазного сигнала

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи для усиления разности двух сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов. Дифференциальный усилитель (ДУ) содержит первый входной дифференциальный каскад (ДК) (1) с первым токостабилизирующим двухполюсником (ТД) (2), первый вывод которого соединен с эмиттерами входных n-p-n транзисторов (Т) (3) и (4), базы которых подключены ко входам ДУ (5) и (6), второй входной ДК (7) со вторым ТД (8), первый вывод которого соединен с эмиттерами входных p-n-p Т (9) и (10), базы которых связаны со входами ДУ (5) и (6), выходной каскад на p-n-p (11) и n-p-n (12) выходных Т, коллекторы которых подключены к нагрузке (13), базы - связаны с соответствующими источниками положительного (14) и отрицательного (15) напряжений смещения, причем эмиттер Т (11) связан через двухполюсник (16) с шиной источника питания (ИП) (17) и коллектором Т (4), а эмиттер Т (12) соединен через двухполюсник (18) с шиной ИП (19) и коллектором Т (10). Введены p-n-p (20) и n-p-n (21) составные Т, коллекторы которых подключены к нагрузке (13), базы - к соответствующим источникам (14) и (15) смещения, причем эмиттер Т (20) соединен с шиной ИП (17) через двухполюсник (22) и подключен ко второму выводу ТД (8), а эмиттер второго Т (21) соединен с шиной ИП (19) через двухполюсник (23) и подключен ко второму выводу ТД (2). 1 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления разности двух сигналов в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах).

Известны схемы дифференциальных усилителей (ДУ), реализованных на основе двух параллельно включенных дифференциальных каскадов (ДК) с токостабилизирующими двухполюсниками в эмиттерных цепях входных транзисторов (так называемые «dual input stage») и выходных каскадов, выполненных на транзисторах по схеме с общей базой [1-7]. Это самые широкополосные ДУ. По такой архитектуре, на модификации которой выдано около 100 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм. Причем в качестве токостабилизирующих двухполюсников каждого из параллельно включенных ДК таких ДУ применяются резисторы [8-11] - если усилитель не работает с синфазным сигналом. Последний вариант построения ДУ практически не используется в структуре операционных усилителей и компараторов, т.к. он не дает приемлемых значений коэффициента ослабления входного синфазного сигнала (Кос.сф). Это связано с тем, что для получения больших значений Кос.сф необходимо выбирать сопротивление токостабилизирующих резисторов на уровне сотен килом, что создает проблемы со статическим режимом при низковольтном питании (EП=1,5÷5 В). В технической литературе по аналоговой схемотехнике хорошо известно следующее правило построения ДУ - «в качестве токостабилизирующих двухполюсников ДУ не следует применять резисторы» (Ежков Ю.С. Справочник по схемотехнике усилителей. М.: Радиософт, 2002. - С.81, 3 абзац сверху).

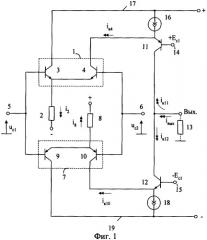

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №5291149, фиг.1, содержащий первый входной дифференциальный каскад 1 с первым токостабилизирующим двухполюсником 2, первый вывод которого соединен с эмиттерами входных n-p-n транзисторов 3 и 4, базы которых подключены ко входам дифференциального усилителя 5 и 6, второй входной дифференциальный каскад 7 со вторым токостабилизирующим двухполюсником 8, первый вывод которого соединен с эмиттерами входных p-n-p транзисторов 9 и 10, базы которых связаны со входами дифференциального усилителя 5 и 6, выходной каскад на первом p-n-p 11 и втором n-p-n 12 выходных транзисторах, коллекторы которых соединены друг с другом и подключены к нагрузке 13, базы - связаны с соответствующими источниками положительного 14 и отрицательного 15 напряжений смещения, причем эмиттер первого выходного p-n-p транзистора 11 связан через первый вспомогательный двухполюсник 16 с шиной положительного источника питания 17 и коллектором входного n-p-n транзистора 4, а эмиттер второго выходного n-p-n транзистора 12 соединен через второй вспомогательный двухполюсник 18 с шиной отрицательного источника питания 19 и коллектором входного p-n-p транзистора 10. В связи с применением «перегнутых» каскодных усилителей такие ДУ обеспечивают предельное значение верхней граничной частоты.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов. Прежде всего, данный недостаток проявляется при использовании в качестве токостабилизирующих двухполюсников 2 и 8 резисторов или простейших источников тока на транзисторах с малым напряжением Эрли, которые при милиамперных токах имеют выходное сопротивление порядка 30-60 кОм.

Определим Кос.сф дифференциального усилителя-прототипа фиг.1. При изменении входного синфазного сигнала uc=uc1=uc2 изменяются токи через двухполюсники 2 и 8

где , - проводимости двухполюсников 2 и 8.

Эти токи делятся пополам в эмиттерных цепях транзисторов 3, 4, 9, 10. Поэтому коллекторные токи транзисторов 4 и 10:

где К3.4≈K4.10≈0,5 - коэффициенты деления токов в общей эмиттерной цепи дифференциальных каскадов 1 и 7;

α4≈4, α10≈1 - коэффициенты усиления по току эмиттера транзисторов 4 и 10.

Причем

где rэ3≈rэ4; rэ9≈rэ10 - сопротивления эмиттерных переходов транзисторов 3, 4 и 9, 10.

В результате ток в нагрузке 13, обусловленный синфазным сигналом uc

Или

Если на вход 5 и 6 ДУ подается дифференциальный сигнал uвх=uc1-uс2, то ток в нагрузке 13, обусловленный этим сигналом

где rэ=rэ3=rэ4=rэ9=rэ10.

По определения Кос.сф может быть рассчитан по формуле:

После преобразований (10) с учетом (8) и (9) при y8=y2 находим

Таким образом при R2=R8=10 кОм и статическом токе эмиттеров Iэ=250 мкА транзисторов 3, 4 и 9, 10: Кос.сф=100 (или 40 дБ).

Эти расчетные данные совпадают с результатами компьютерного моделирования ДУ фиг.5, представленными на чертеже фиг.7.

Таким образом, известный ДУ имеет малый коэффициент ослабления синфазных сигналов.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ДУ при относительно небольших внутренних сопротивлениях токостабилизирующих двухполюсников. При этом в заявляемом ДУ в качестве токостабилизирующих двухполюсников 2 и 8 могут применяться сравнительно низкоомные резисторы.

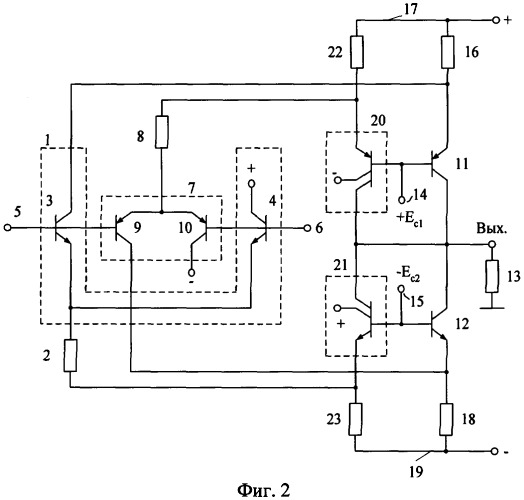

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий первый входной дифференциальный каскад 1 с первым токостабилизирующим двухполюсником 2, первый вывод которого соединен с эмиттерами входных n-p-n транзисторов 3 и 4, базы которых подключены ко входам дифференциального усилителя 5 и 6, второй входной дифференциальный каскад 7 со вторым токостабилизирующим двухполюсником 8, первый вывод которого соединен с эмиттерами входных p-n-p транзисторов 9 и 10, базы которых связаны со входами дифференциального усилителя 5 и 6, выходной каскад на первом p-n-p 11 и втором n-p-n 12 выходных транзисторах, коллекторы которых соединены друг с другом и подключены к нагрузке 13, базы - связаны с соответствующими источниками положительного 14 и отрицательного 15 напряжений смещения, причем эмиттер первого выходного p-n-p транзистора 11 связан через первый вспомогательный двухполюсник 16 с шиной положительного источника питания 17 и коллектором входного n-p-n транзистора 4, а эмиттер второго выходного n-p-n транзистора 12 соединен через второй вспомогательный двухполюсник 18 с шиной отрицательного источника питания 19 и коллектором входного p-n-p транзистора 10, вводятся новые элементы и связи - первый p-n-p 20 и второй n-p-n 21 составные транзисторы, коллекторы которых подключены к нагрузке 13, базы - к соответствующим источникам положительного 14 и отрицательного 15 напряжений смещения, причем эмиттер первого p-n-p составного транзистора 20 соединен с шиной положительного источника питания 17 через первый дополнительный двухполюсник 22 и подключен ко второму выводу второго токостабилизирующего двухполюсника 8, а эмиттер второго составного n-p-n транзистора 21 соединен с шиной отрицательного источника питания 19 через второй дополнительный двухполюсник 23 и подключен ко второму выводу первого токостабилизирующего двухполюсника 2.

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на чертеже фиг.2.

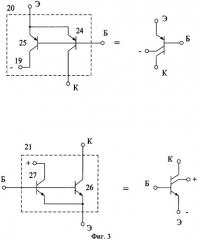

На чертеже фиг.3 показана схемотехника составного p-n-p 20 и n-p-n 21 транзисторов ДУ фиг.2.

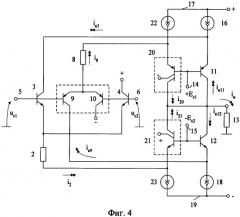

Переменные токи и напряжения в заявляемом ДУ фиг.2 при воздействии на его входы 5 и 6 синфазного сигнала uc1=uc2=uc показаны на чертеже фиг.4.

На чертеже фиг.5 изображена схема ДУ-прототипа фиг.1, которая исследовалась авторами в среде PSpice на степень ослабления синфазных сигналов. На чертеже фиг.6 показана схема заявляемого ДУ (при воздействии на его входы синфазного сигнала uc) на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На чертеже фиг.7 показаны результаты компьютерного моделирования схем ДУ фиг.5 и фиг.6 - зависимость их коэффициентов ослабления входных синфазных сигналов (Кос.сф) от частоты.

Дифференциальный усилитель фиг.2 содержит первый входной дифференциальный каскад 1 с первым токостабилизирующим двухполюсником 2, первый вывод которого соединен с эмиттерами входных n-p-n транзисторов 3 и 4, базы которых подключены ко входам дифференциального усилителя 5 и 6, второй входной дифференциальный каскад 7 со вторым токостабилизирующим двухполюсником 8, первый вывод которого соединен с эмиттерами входных p-n-p транзисторов 9 и 10, базы которых связаны со входами дифференциального усилителя 5 и 6, выходной каскад на первом p-n-p 11 и втором n-p-n 12 выходных транзисторах, коллекторы которых соединены друг с другом и подключены к нагрузке 13, базы - связаны с соответствующими источниками положительного 14 и отрицательного 15 напряжений смещения, причем эмиттер первого выходного p-n-p транзистора 11 связан через первый вспомогательный двухполюсник 16 с шиной положительного источника питания 17 и коллектором входного n-p-n транзистора 4, а эмиттер второго выходного n-p-n транзистора 12 соединен через второй вспомогательный двухполюсник 18 с шиной отрицательного источника питания 19 и коллектором входного p-n-p транзистора 10. В схему введены первый p-n-p 20 и второй n-p-n 21 составные транзисторы, коллекторы которых подключены к нагрузке 13, базы - к соответствующим источникам положительного 14 и отрицательного 15 напряжений смещения, причем эмиттер первого p-n-p составного транзистора 20 соединен с шиной положительного источника питания 17 через первый дополнительный двухполюсник 22 и подключен ко второму выводу второго токостабилизирующего двухполюсника 8, а эмиттер второго составного n-p-n транзистора 21 соединен с шиной отрицательного источника питания 19 через второй дополнительный двухполюсник 23 и подключен ко второму выводу первого токостабилизирующего двухполюсника 2.

В соответствии с п.2 формулы изобретения (фиг.3) первый составной p-n-p транзистор 20 выполнен в виде первого 24 и второго 25 вспомогательных p-n-p транзисторов, соответствующие эмиттеры и базы которых объединены друг с другом, причем коллектор первого вспомогательного транзистора 24 является коллекторным выводом первого составного p-n-p транзистора 20, а коллектор второго вспомогательного транзистора 25 подключен к шине отрицательного источника питания 19, второй составной n-p-n транзистор 21 выполнен в виде первого 26 и второго 27 вспомогательных n-p-n транзисторов, соответствующие эмиттеры и базы которых объединены друг с другом, причем коллектор первого вспомогательного n-p-n транзистора 26 является коллекторным выводом второго составного n-p-n транзистора 21, а коллектор второго вспомогательного транзистора 27 подключен к шине положительного источника питания 19.

Рассмотрим работу заявляемого ДУ на примере анализа схемы фиг.4.

Изменение входного синфазного напряжения на входах ДУ 5 и 6 на величину uc=uc1=uc2 приводят к изменению токов через двухполюсники 2 и 8:

где y8, y2 - проводимости двухполюсников 2 и 8.

Поэтому коллекторные токи транзисторов 3 и 9, а также 20 и 21, 11 и 12:

где K10.9≈K4.3≈0,5;

α9≈1, α3≈1, α12≈α21≈α20≈1.

Из уравнений (13)-(18) можно найти составляющую тока нагрузки, обусловленную синфазным сигналом на входе ДУ, и коэффициент Ку.сф:

где R13 - сопротивление резистора нагрузки 13.

Аналогично найдем выходной ток и усиление дифференциального сигнала uвх ДУ фиг.4:

Поэтому коэффициент ослабления входных синфазных сигналов

где

Из уравнения (24) следует, что в заявляемом ДУ влияние y8 и y2 на Кос.сф ослабляется в Ni-раз, где

Благодаря попарной идентичности коэффициентов передачи по току, входящих в уравнение (25)-(26), знаменатель формулы (27) близок к нулю. Следовательно, введение новых связей повышает Кос.сф ДУ фиг.4. Компьютерное моделирование (фиг.7) подтверждает данный вывод.

Важнейшее свойство заявляемой схемы ДУ - широкий допустимый диапазон изменения синфазного сигнала (uc.max) - практически равный его напряжению питания (ЕП). Следует обратить внимание, что построение высокоэффективных входных дифференциальных каскадов с uc.max≈±EП относится к числу плохо решенных проблем современной аналоговой микросхемотехники.

Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г. Москва) (фиг.7).

Источники информации

1. Патент США №5291149, фиг.1.

2. Патент РФ №2193273, H03F 3/45.

3. Справочник: операционные усилители и компараторы (Авербух В. Д. и др.). - М.: Изд-во «Додэка-XXI», 2001, с.122 (НА 2539).

4. Патент США №4600893, фиг.3.

5. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989, стр.103, рис.6. 11 (ОУ HAS 190).

6. Патент США №4837522, фиг.1.

7. Ежков Ю.С. Справочник по схемотехнике усилителей. - М.: Радио-Софт, 2002, с.87, рис.5.21.

8. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983. - 216 с. - стр.156, рис.4.25.

9. Патент США №4131809, H03F 3/45.

10. Патент США №3323070, H03F 3/45.

11. Патент ЕР №1351381 A1, H03F 3/30.

1. Дифференциальный усилитель с повышенным ослаблением синфазного сигнала, содержащий первый входной дифференциальный каскад (1) с первым токостабилизирующим двухполюсником (2), первый вывод которого соединен с эмиттерами входных n-p-n транзисторов (3) и (4), базы которых подключены ко входам дифференциального усилителя (5) и (6), второй входной дифференциальный каскад (7) со вторым токостабилизирующим двухполюсником (8), первый вывод которого соединен с эмиттерами входных p-n-p транзисторов (9) и (10), базы которых связаны со входами дифференциального усилителя (5) и (6), выходной каскад на первом p-n-p (11) и втором n-p-n (12) выходных транзисторах, коллекторы которых соединены друг с другом и подключены к нагрузке (13), базы - связаны с соответствующими источниками положительного (14) и отрицательного (15) напряжений смещения, причем эмиттер первого выходного p-n-p транзистора (11) связан через первый вспомогательный двухполюсник (16) с шиной положительного источника питания (17) и коллектором входного n-p-n транзистора (4), а эмиттер второго выходного n-p-n транзистора (12) соединен через второй вспомогательный двухполюсник (18) с шиной отрицательного источника питания (19) и коллектором входного p-n-p транзистора (10), отличающийся тем, что в схему введены первый p-n-p (20) и второй n-p-n (21) составные транзисторы, коллекторы которых подключены к нагрузке (13), базы - к соответствующим источникам положительного (14) и отрицательного (15) напряжений смещения, причем эмиттер первого p-n-p составного транзистора (20) соединен с шиной положительного источника питания (17) через первый дополнительный двухполюсник (22) и подключен ко второму выводу второго токостабилизирующего двухполюсника (8), а эмиттер второго составного n-p-n транзистора (21) соединен с шиной отрицательного источника питания (19) через второй дополнительный двухполюсник (23) и подключен ко второму выводу первого токостабилизирующего двухполюсника.

2. Устройство по п.1, отличающееся тем, что первый составной p-n-p транзистор (20) выполнен в виде первого (24) и второго (25) вспомогательных p-n-p транзисторов, соответствующие эмиттеры и базы которых объединены друг с другом, причем коллектор первого вспомогательного транзистора (24) является коллекторным выводом первого составного p-n-p транзистора (20), а коллектор второго вспомогательного транзистора (25) подключен к шине отрицательного источника питания (19), второй составной n-p-n транзистор (21) выполнен в виде первого (26) и второго (27) вспомогательных n-p-n транзисторов, соответствующие эмиттеры и базы которых объединены друг с другом, причем коллектор первого вспомогательного n-p-n транзистора (26) является коллекторным выводом второго составного n-p-n транзистора (21), а коллектор второго вспомогательного транзистора (27) подключен к шине положительного источника питания (19).