Дифференциальный усилитель с низковольтным питанием

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ), компараторах и т.п.). Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов ДУ и коэффициента подавления помехи по питанию. Дифференциальный усилитель (ДУ) с низковольтным питанием содержит входной параллельно-балансный каскад (ПБК) (1) на n-p-n транзисторах (Т) (2) и (3), объединенные эмиттеры которых соединены с первым выводом токостабилизирующего двухполюсника (ТД) (4), ПБК (5) на p-n-p Т (6) и (7), объединенные эмиттеры которых соединены с первым выводом ТД (8), причем синфазные входы ПБК (1) и (5) объединены друг с другом и соединены со входами ДУ (9) и (10), выход (11) ПБК (1) связан со входом (12) токового зеркала (ТЗ) (13), согласованного с шиной положительного источника питания (ИП) (14), выход (15) ПБК (5) связан со входом (16) ТЗ (17), согласованного с шиной отрицательного ИП (18), коллекторный выход которого соединен с выходом ДУ (19) и коллекторным выходом ТЗ (13). В схему введены дополнительные ТЗ (20) и (21) на комплементарных Т, коллекторные выходы которых соединены с выходом ДУ, причем вход ТЗ (20) соединен со вторым выводом ТД (8), а вход второго ТЗ (21) соединен со вторым выводом ТД (4). 1 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ), компараторах и т.п.).

Известны схемы дифференциальных усилителей (ДУ) на основе двух параллельно-включенных дифференциальных каскадов (ДК) с токостабилизирующими двухполюсниками в эмиттерных цепях входных транзисторов (так называемые «dual input stage») и выходных каскадов, выполненных на повторителях тока. ДУ с такой архитектурой стали основой построения многих современных операционных усилителей [1-17], в т.ч. ОУ с опцией rail-to-rail (имеющих максимальную амплитуду выходного напряжения, близкую к напряжению питания). Однако такие ДУ имеют недостаточно высокое ослабление синфазных сигналов и помех по питанию при использовании в качестве токостабилизирующих двухполюсников пассивных элементов (резисторов), что отрицательно сказывается на точности аналоговых интерфейсов с их использованием. Это связано с тем, что для получения больших значений Кос.сф необходимо выбирать сопротивление токостабилизирующих резисторов на уровне сотен килоом, что создает проблемы со статическим режимом при низковольтном питании (ЕП=1,5÷5 В).

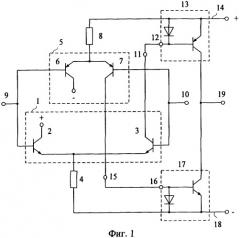

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №5.291.149, содержащий первый входной параллельно-балансный каскад 1 на n-p-n транзисторах 2 и 3, объединенные эмиттеры которых соединены с первым выводом первого токостабилизирующего двухполюсника 4, второй входной параллельно-балансный каскад 5 на p-n-p транзисторах 6 и 7, объединенные эмиттеры которых соединены с первым выводом второго токостабилизирующего двухполюсника 8, причем синфазные входы первого 1 и второго 5 входных параллельно-балансных каскадов (базы транзисторов 6 и 2, 3 и 7) объединены друг с другом и соединены со входами дифференциального усилителя 9 и 10, выход 11 первого входного параллельно-балансного каскада 1 на n-p-n транзисторах связан со входом 12 первого токового зеркала 13, согласованного с шиной положительного источника питания 14, выход 15 второго входного параллельно-балансного каскада 5 на p-n-p транзисторах связан со входом 16 второго токового зеркала 17, согласованного с шиной отрицательного источника питания 18, коллекторный выход которого соединен с выходом дифференциального усилителя 19 и коллекторным выходом первого токового зеркала 13.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов, а также помех по питанию. Прежде всего, данный недостаток проявляется при использовании в качестве токостабилизирующих двухполюсников 4 и 8 резисторов или простейших источников тока на транзисторах с малым напряжением Эрли, которые при милиамперных токах имеют небольшое выходное сопротивление (порядка 30-60 КОм).

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ДУ (Кос.сф) и коэффициента подавления помехи по питанию (Кпп) при относительно небольших внутренних сопротивлениях токостабилизирующих двухполюсников 4 и 8. При этом в заявляемом ДУ в качестве токостабилизирующих двухполюсников 4 и 8 при низковольтном питании могут применяться сравнительно низкоомные резисторы (единицы килоом). Тем не менее это несущественно сказывается на численных значениях Кос.сф и Кпп.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый входной параллельно-балансный каскад 1 на n-p-n транзисторах 2 и 3, объединенные эмиттеры которых соединены с первым выводом первого токостабилизирующего двухполюсника 4, второй входной параллельно-балансный каскад 5 на p-n-p транзисторах 6 и 7, объединенные эмиттеры которых соединены с первым выводом второго токостабилизирующего двухполюсника 8, причем синфазные входы первого 1 и второго 5 входных параллельно-балансных каскадов объединены друг с другом и соединены со входами дифференциального усилителя 9 и 10, выход 11 первого входного параллельно-балансного каскада 1 на n-p-n транзисторах связан со входом 12 первого токового зеркала 13, согласованного с шиной положительного источника питания 14, выход 15 второго входного параллельно-балансного каскада 5 на p-n-p транзисторах связан со входом 16 второго токового зеркала 17, согласованного с шиной отрицательного источника питания 18, коллекторный выход которого соединен с выходом дифференциального усилителя 19 и коллекторным выходом первого токового зеркала 13, предусмотрены новые элементы и связи - вводятся первое 20 и второе 21 дополнительные токовые зеркала на комплементарных транзисторах, коллекторные выходы которых соединены с выходом дифференциального усилителя, причем вход первого дополнительного токового зеркала 20 соединен со вторым входом второго токостабилизирующего двухполюсника 8, а вход второго дополнительного токового зеркала 21 соединен со вторым выводом первого токостабилизирующего двухполюсника 4.

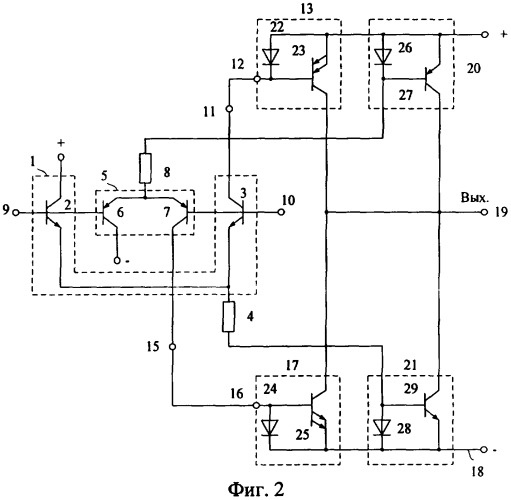

Схема заявляемого устройства показана на фиг.2. При этом в соответствии с п.2 формулы изобретения коэффициенты передачи по току первого 20 (Ki20) и второго 21 (Ki21) дополнительных токовых зеркал в данной схеме в два раза меньше, чем коэффициенты передачи по току первого 13 (Кi13) и второго 17 (Кi17) токовых зеркал. Этот режим обеспечивается соответствующим выбором площадей эмиттерных переходов транзисторов 23, 25, входящих в токовые зеркала 13 и 17.

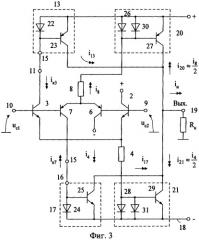

На фиг.3 показан другой вариант построения ДУ фиг.2, у которого коэффициенты передачи дополнительных токовых зеркал 20 и 21 также в 2 раза меньше коэффициентов передачи токовых зеркал 13 и 17. Однако этот режим обеспечивается за счет параллельного включения во входной цепи данных токовых зеркал двух p-n переходов 26, 30 (28, 31).

Переменные токи и напряжения в заявляемом ДУ при воздействии на его входы 9 и 10 синфазного сигнала uc1=uc2=uc показаны на фиг.3.

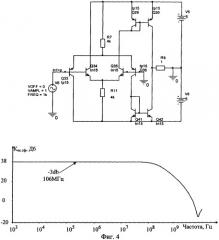

На фиг.4 изображена схема ДУ-прототипа фиг.1, которая исследовалась авторами в среде PSpice на степень ослабления входных синфазных сигналов uc1=uc2=uc. Здесь же приведена частотная зависимость его коэффициента ослабления входного синфазного сигнала (Кос.сф).

На фиг.5 показана схема заявляемого ДУ фиг.2 (при воздействии на его входы синфазного сигнала Uс) на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.6 показана другая модификация заявляемого ДУ - схема фиг.3 (при воздействии на его входы синфазного сигнала uc) на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Дифференциальный усилитель фиг.2 содержит первый входной параллельно-балансный каскад 1 на n-p-n транзисторах 2 и 3, объединенные эмиттеры которых соединены с первым выводом первого токостабилизирующего двухполюсника 4, второй входной параллельно-балансный каскад 5 на p-n-p транзисторах 6 и 7, объединенные эмиттеры которых соединены с первым выводом второго токостабилизирующего двухполюсника 8, причем синфазные входы первого 1 и второго 5 входных параллельно-балансных каскадов (базы транзисторов 6 и 2, 3 и 7) объединены друг с другом и соединены со входами дифференциального усилителя 9 и 10, выход 11 первого входного параллельно-балансного каскада 1 на n-p-n транзисторах связан со входом 12 первого токового зеркала 13, согласованного с шиной положительного источника питания 14, выход 15 второго входного параллельно-балансного каскада 5 на p-n-p транзисторах связан со входом 16 второго токового зеркала 17, согласованного с шиной отрицательного источника питания 18, коллекторный выход которого соединен с выходом дифференциального усилителя 19 и коллекторным выходом первого токового зеркала 13. В схему введены первое 20 и второе 21 дополнительные токовые зеркала на комплементарных транзисторах, коллекторные выходы которых соединены с выходом дифференциального усилителя 19, причем вход первого дополнительного токового зеркала 20 соединен со вторым входом второго токостабилизирующего двухполюсника 8, а вход второго дополнительного токового зеркала 21 соединен со вторым выводом первого токостабилизирующего двухполюсника 4.

Для реализации в практических схемах п.2 формулы изобретения - обеспечение условий, при которых коэффициенты передачи по току дополнительных токовых зеркал 20-21 в два раза меньше, чем коэффициент передачи по току первого 13 и второго 17 токовых зеркал, в схеме фиг.2 применяются транзисторы 23 и 25 с удвоенной площадью эмиттерных p-n переходов.

В другом частном случае (фиг.3) за счет параллельного включения во входной цепи двух p-n переходов 26, 30 и 28, 31 токовые зеркала 20 и 21 также имеют коэффициент передачи по току в 2 раза меньше, чем токовые зеркала 13 и 17.

Рассмотрим работу заявляемого ДУ на примере анализа схемы фиг.3.

Изменение входного синфазного напряжения на входах ДУ 9 и 10 на величину uc=uc1=uc2 приводит к изменению токов через двухполюсники 8 и 4:

где y8, y4 - проводимости двухполюсников 8 и 4.

Поэтому коллекторные токи транзисторов 7 и 3:

где K6.7(K2.3)≈0,5 - коэффициент деления тока i8 (i4) между эмиттерами транзисторов VT6, VT7 (VT2, VT3);

α7≈1, α3≈1 - коэффициенты передачи по току эмиттеров транзисторов VT7, VT3.

Коллекторные токи транзисторов 3 и 7 ik3, ik7 передаются через токовые зеркала 13 и 17 на выход ДУ 19 и создают две составляющие тока нагрузки iн:

С другой стороны токи двухполюсников 8 (i8) и 4 (i4) поступают на входы дополнительных токовых зеркал 20 и 21 и также создают в нагрузке две другие составляющие тока iн:

Причем направления этих токов противоположны направлению токов i13 и i17. Поэтому в выходном узле ДУ происходит попарная взаимная компенсация синфазных составляющих ошибки

С учетом (5) и (8) формулу (9) можно представить в виде

где - коэффициент неидентичности токовых зеркал 21 и 13. (11)

- коэффициент неидентичности токовых зеркал 20 и 17. (12)

Так как коэффициенты Кi20=0,5Ki17, К2.3=0,5, Ki21=0,5Ki13, K6.7=0,5, то из (10) следует, что в заявляемом ДУ существенно уменьшается эффект «прохождения» входного синфазного сигнала uc на выход ДУ.

Так, в сравнении с прототипом фиг.1 коэффициент передачи uc на выход ДУ уменьшается в Ас-раз, где

где - коэффициент передачи входного синфазного сигнала Uc ДУ-прототипа;

Kсф.з - коэффициент передачи входного синфазного сигнала заявляемого ДУ.

Аналогично можно показать, что по сравнению с прототипом, в схемах фиг.2 - фиг.3 уменьшается и коэффициент влияния нестабильности напряжения питания на э.д.с. смещения нуля (Кпп).

Полученные выше выводы подтверждаются результатами моделирования предлагаемых рассматриваемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г.Москва) (фиг.5, фиг.6) - заявляемый ДУ имеет более чем на порядок лучшие значения коэффициента ослабления входных синфазных сигналов (24-27 дБ).

Литература

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - Рис.6.11.

2. Двухтактный операционный усилитель. Патент РФ №2193273, Н03f 3/45.

3. Дифференциальный усилитель. Патент США №4649352, кл. 330-261.

4. Операционные усилители с непосредственной связью каскадов / В.И.Анисимов, М.В.Капитонов, Н.Н.Прокопенко, Ю.М.Соколов. - Л., 1979.

5. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983. - 216 с.

6. Патент США №5.291.149, Н03f 3/48 (прототип).

7. Патент США №6.268.769, Н03f 3/45 (фиг.3) (прототип 2).

8. Патент США №3.974.455, Н03f 3/45 (фиг.7, фиг.9).

9. Патент США №3.968.451, Н03f 3/45

10. Патент Японии 981(5)А332 №53-25232, Н03f 3/26

11. Патент США №4.783.637, Н03f 3/45

12. Патент США №4.146.845, кл. 330/225

13. Патент США №4.595.883, кл. 330/255

14. Патент США №4.636.743, кл. 330/295

15. Патент США №5.515.005, Н03f 3/45

16. Патент США №4.600.893, Н03f 3/45

17. Журнал «Радио» №1, 1980 г. стр.44, рис.2

1. Дифференциальный усилитель с низковольтным питанием, содержащий первый входной параллельно-балансный каскад (1) на n-p-n транзисторах (2) и (3), объединенные эмиттеры которых соединены с первым выводом первого токостабилизирующего двухполюсника (4), второй входной параллельно-балансный каскад (5) на p-n-p транзисторах (6) и (7), объединенные эмиттеры которых соединены с первым выводом второго токостабилизирующего двухполюсника (8), причем синфазные входы первого (1) и второго (5) входных параллельно-балансных каскадов объединены друг с другом и соединены со входами дифференциального усилителя (9) и (10), выход (11) первого входного параллельно-балансного каскада (1) на n-p-n транзисторах связан со входом (12) первого токового зеркала (13), согласованного с шиной положительного источника питания (14), выход (15) второго входного параллельно-балансного каскада (5) на p-n-p транзисторах связан со входом (16) второго токового зеркала (17), согласованного с шиной отрицательного источника питания (18), коллекторный выход которого соединен с выходом дифференциального усилителя (19) и коллекторным выходом первого токового зеркала (13), отличающийся тем, что в схему введены первое (20) и второе (21) дополнительные токовые зеркала на разнотипных комплементарных транзисторах, коллекторные выходы которых соединены с выходом дифференциального усилителя, причем вход первого дополнительного токового зеркала (20) соединен со вторым выводом второго токостабилизирующего двухполюсника (8), а вход второго дополнительного токового зеркала (21) соединен со вторым выводом первого токостабилизирующего двухполюсника (4).

2. Устройство по п.1, отличающееся тем, что коэффициенты передачи по току дополнительных токовых зеркал (20) и (21) в два раза меньше, чем коэффициенты передачи по току первого (13) и второго (17) токовых зеркал.