Каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Каскодный дифференциальный усилитель (КДУ) содержит входной параллельно-балансный каскад (1) на транзисторах (Т) (2) и (3), базы которых являются входами (4 и 5) КДУ, а эмиттеры связаны с источником опорного тока (ИОТ) (6), базы Т (7, 8, 9 и 10) объединены и подключены к источнику напряжения смещения (11), причем объединенные эмиттеры Т (7 и 8) соединены с первым выходом (12) каскада (1) и через первый токостабилизирующий двухполюсник (ТД) (13) соединены с шиной первого источника питания (ИП) (14), объединенные эмиттеры Т (9 и 10) соединены со вторым выходом (15) каскада (1) и через второй ТД (16) связаны с шиной первого (14) ИП. Для повышения коэффициента ослабления входного синфазного сигнала ИОТ (6) реализован на вспомогательном транзисторе (21), включенном по схеме с общим эмиттером, эмиттер которого соединен с шиной второго ИП (19), а база соединена с объединенными коллекторами Т (7) и Т (10). 2 з.п. ф-лы, 9 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах).

Известны схемы так называемых "перегнутых" каскадных дифференциальных усилителей (ДУ) на n-p-n и p-n-р транзисторах [1-36], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УД3 и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 200 патентов для ведущих производителей микроэлектронных изделий. Предполагаемое изобретение относится к данному подклассу устройств.

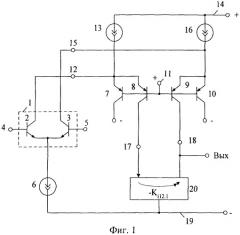

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный дифференциальный усилитель (КДУ), описанный в патенте США №4390850, содержащий входной параллельно-балансный каскад 1 на первом 2 и втором 3 входных транзисторах, базы которых являются входами 4 и 5 каскодного дифференциального усилителя, а эмиттеры связаны с источником опорного тока 6, первый 7, второй 8, третий 9 и четвертый 10 выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения 11, причем объединенные эмиттеры первого 7 и второго 8 выходных транзисторов соединены с первым выходом 12 входного параллельно-балансного каскада 1 и через первый токостабилизирующий двухполюсник 13 соединены с шиной первого источника питания 14, объединенные эмиттеры третьего 9 и четвертого 10 выходных транзисторов соединены со вторым выходом 15 входного параллельно-балансного каскада 1 и через второй токостабилизирующий двухполюсник 16 связаны с шиной первого 14 источника питания, причем между коллекторами 17 и 18 второго 8 и третьего 9 выходных транзисторов и шиной второго источника питания 19 включена цепь нагрузки 20.

Существенный недостаток известного КДУ (фиг.1) состоит в том, что он имеет сравнительно небольшой коэффициент ослабления входного синфазного сигнала (Кос.сф), что отрицательно сказывается на погрешностях неинвертирующих решающих усилителей и компараторов на его основе.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входного синфазного сигнала.

Поставленная цель достигается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем входной параллельно-балансный каскад 1 на первом 2 и втором 3 входных транзисторах, базы которых являются входами 4 и 5 каскодного дифференциального усилителя, а эмиттеры связаны с источником опорного тока 6, первый 7, второй 8, третий 9 и четвертый 10 выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения 11, причем объединенные эмиттеры первого 7 и второго 8 выходных транзисторов соединены с первым выходом 12 входного параллельно-балансного каскада 1 и через первый токостабилизирующий двухполюсник 13 соединены с шиной первого источника питания 14, объединенные эмиттеры третьего 9 и четвертого 10 выходных транзисторов соединены со вторым выходом 15 входного параллельно-балансного каскада 1 и через второй токостабилизирующий двухполюсник 16 связаны с шиной первого 14 источника питания, причем между коллекторами 17 и 18 второго 8 и третьего 9 выходных транзисторов и шиной второго источника питания 19 включена цепь нагрузки 20, предусмотрены новые связи - источник опорного тока 6 реализован на вспомогательном транзисторе 21, включенном по схеме с общим эмиттером, эмиттер которого соединен с шиной второго источника питания 19, а база соединена с объединенными коллекторами первого 7 и четвертого 10 выходных транзисторов.

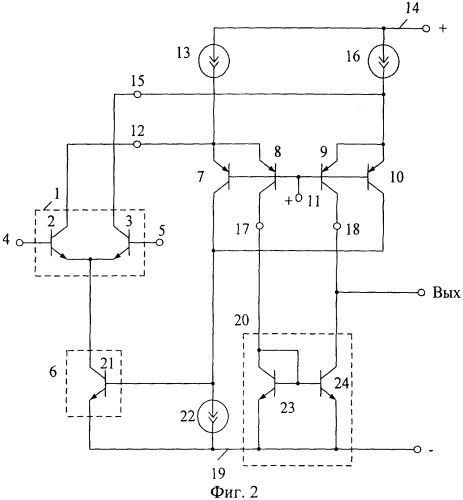

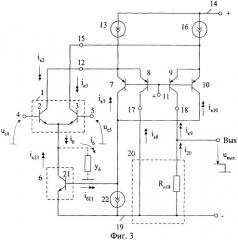

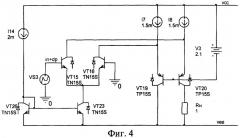

Схема усилителя-прототипа представлена на чертеже фиг.1. На чертежах фиг.2, фиг.3 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения. Причем двухполюсник 22 и цепь нагрузки 20 в КДУ фиг.2 соответствуют п.2 и п.3 формулы изобретения. На чертежах фиг.4, фиг.5 показаны схемы заявляемого (фиг.5) и известного (фиг.4) устройств в среде компьютерного моделирования PSpice, а на чертеже фиг.6 - частотная зависимость коэффициента ослабления входных синфазных сигналов Кос.сф сравниваемых КДУ. Следует заметить, что в схемах фиг.4 фиг.5 используется частный вариант активной нагрузки 20, выполненной в виде резистора Rн 18. Экспериментальные исследования сравниваемых КДУ для других типов цепи нагрузки 20 (с токовым зеркалом на элементах 23, 24, фиг.2) показан на чертеже фиг.7 (прототип) и фиг.8 (заявляемое устройство). На чертеже фиг.9 изображены зависимости Кос.сф для этих вариантов сравниваемых усилителей.

Дифференциальный усилитель, фиг.2, содержит входной параллельно-балансный каскад 1 на первом 2 и втором 3 входных транзисторах, базы которых являются входами 4 и 5 каскодного дифференциального усилителя, а эмиттеры связаны с источником опорного тока 6, первый 7, второй 8, третий 9 и четвертый 10 выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения 11, причем объединенные эмиттеры первого 7 и второго 8 выходных транзисторов соединены с первым выходом 12 входного параллельно-балансного каскада 1 и через первый токостабилизирующий двухполюсник 13 соединены с шиной первого источника питания 14, объединенные эмиттеры третьего 9 и четвертого 10 выходных транзисторов соединены со вторым выходом 15 входного параллельно-балансного каскада 1 и через второй токостабилизирующий двухполюсник 16 связаны с шиной первого 14 источника питания, причем между коллекторами 17 и 18 второго 8 и третьего 9 выходных транзисторов и шиной второго источника питания 19 включена цепь нагрузки 20. Источник опорного тока 6 реализован на вспомогательном транзисторе 21, включенном по схеме с общим эмиттером, эмиттер которого соединен с шиной второго источника питания 19, а база соединена с объединенными коллекторами первого 7 и четвертого 10 выходных транзисторов.

В частных случаях (фиг.2) между базой вспомогательного транзистора 21 и шиной второго 19 источника питания включен двухполюсник 22, а нагрузка 20 выполнена по классической схеме - в виде токового зеркала на транзисторах 23 и 24.

Рассмотрим работу заявляемого каскодного дифференциального усилителя на примере анализа схемы фиг.3.

Существенный недостаток известных КДУ - недостаточно высокое ослабление синфазных сигналов, которое существенно зависит от величины выходной проводимости (у6) источников опорного тока 6 (ИОТ). Для биполярных транзисторов выходная проводимость у6 зависит от напряжения Эрли (Uэ) и статического тока коллектора (Iк21) транзистора 21 следующим образом

Для современных интегральных транзисторов Uэ=20÷40 В, то есть при миллиамперных токах (Iк21=1 мА) численные значения выходного сопротивления ИОТ что отрицательно сказывается на ослаблении синфазных сигналов.

В заявляемом устройстве при наличии синфазной составляющей сигналов uc4=uc5=uc изменяется ток через у6:

Для эмиттерной цепи входного каскада 1 при идентичных транзисторах 2, 3 можно составить следующую систему уравнений

Токи iк2, iк3 делятся между эмиттерами транзисторов 7 и 8, 9 и 10:

Причем сумма токов iк7, iк10 равна току базы транзистора 21

который в β1 раз меньше, чем ток коллектора транзистора 21, входящего в источник опорного тока 6:

где β21 - коэффициент усиления тока базы транзистора 21.

С учетом (1)-(9) можно найти, что в заявляемой схеме

Поэтому с учетом (7) и (8) токи в нагрузке 20

Следовательно, при использовании в качестве нагрузки 20 резистора Rн18 (фиг.3) коэффициент передачи по синфазному сигналу КДУ равен

Следует заметить, что в ДУ-прототипе

Так как коэффициент усиления по дифференциальному сигналу сравниваемых КДУ одинаков (Ку), то из этого следует, что в предлагаемой схеме Кос.сф улучшается в Nc раз, где

При β21≈50 выигрыш по Кос.сф получается значительным (более 20). Эти теоретические выводы подтверждают результаты компьютерного моделирования сравниваемых КДУ как для резистивной нагрузки (фиг.6), так и для активной нагрузки в виде токовых зеркал (фиг.9).

Существенное достоинство заявляемого устройства состоит также в том, что в нем обеспечивается повышение Кос.сф при выполнении входного каскада 1 по другим многочисленным модифицированным схемам параллельно-балансных усилителей.

Литература

1. Матавкин В.В. Быстродействующие операционные усилители. - М. Радио и связь, 1989. - с.74, рис.4.15, стр.98, рис.6.7.

2. Патент США №6218900, фиг.1.

3. Патентная заявка US 2002/0196079.

4. Патент США №6788143.

5. Патент США №3644838, фиг.2.

6. Патент США Re 30587.

7. Патент ЕР 1227580.

8. Патент США №6714076.

9. Патент США №5786729.

10. Патент США №5327100.

11. Патентная заявка US 2004/0090268 A1.

12. Патент США №4274061.

13. Патент США №5422600, фиг.2.

14. Патент США №6788143, фиг.2.

15. Патент США №4959622, фиг.1.

16. Патент США №4406990, фиг.4.

17. Патент США №5418491.

18. Патент США №6018268.

19. Патент США №5952882.

20. Патент США №4723111.

21. Патент США №4293824.

22. Патент США №6580325.

23. Патент США №6965266.

24. Патент США №6867643.

25. Патент США №6236270.

26. Патент США №5323121.

27. Патент США №6229394.

28. Патент США №5734296.

29. Патент США №5477190.

30. Патент США №5091701.

31. Патент США №6717474.

32. Патент США №6084475.

33. Патент США №3733559.

34. Патентная заявка US 2005/0001682 А1.

35. Патент США №6300831.

1. Каскодный дифференциальный усилитель, содержащий входной параллельно-балансный каскад (1) на первом (2) и втором (3) входных транзисторах, базы которых являются входами (4) и (5) каскодного дифференциального усилителя, а эмиттеры - связаны с источником опорного тока (6), первый (7), второй (8), третий (9) и четвертый (10) выходные транзисторы, базы которых объединены и подключены к источнику напряжения смещения (11), причем объединенные эмиттеры первого (7) и второго (8) выходных транзисторов соединены с первым выходом (12) входного параллельно-балансного каскада (1) и через первый токостабилизирующий двухполюсник (13) соединены с шиной первого источника питания (14), объединенные эмиттеры третьего (9) и четвертого (10) выходных транзисторов соединены со вторым выходом (15) входного параллельно-балансного каскада (1) и через второй токостабилизирующий двухполюсник (16) связаны с шиной первого (14) источника питания, причем между коллекторами (17) и (18) второго (8) и третьего (9) выходных транзисторов и шиной второго источника питания (19) включена цепь нагрузки (20), отличающийся тем, что источник опорного тока (6) реализован на вспомогательном транзисторе (21), включенном по схеме с общим эмиттером, эмиттер которого соединен с шиной второго источника питания (19), а база - соединена с объединенными коллекторами первого (7) и четвертого (10) выходных транзисторов.

2. Устройство по п.1, отличающееся тем, что между базой вспомогательного транзистора (21) и шиной второго (19) источника питания включен двухполюсник (22).

3. Устройство по п.1, отличающееся тем, что нагрузка (20) выполнена в виде токового зеркала на транзисторах (23) и (24).