Каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях с малыми значениями эдс смещения нуля (ОУ)). Каскодный дифференциальный усилитель (КДУ) содержит входной дифференциальный каскад (ДК) (1), транзисторы (Т) (2) и (3) промежуточного каскада, базы которых подключены к источнику напряжения смещения (4), а эмиттеры соединены с выходами (5) и (6) ДК (1) и через первый (7) и второй (8) токостабилизирующие двухполюсники связаны с шиной первого (9) источника питания (ИП), причем коллектор Т (3) промежуточного каскада (ПК) соединен со входом (10) буферного усилителя (11) и коллектором Т (12) ПК, эмиттер которого соединен с эмиттером Т (13) ПК и шиной второго ИП (14), а база подключена к базе Т (13) и коллектору Т (2). В схему введен дополнительный Т (15), база которого соединена с общей шиной первого (9) и второго (14) ИП, коллектор подключен к эмиттеру Т (2), а эмиттер - соединен с коллектором Т (13), что уменьшает эдс смещения нуля КДУ за счет одинакового смещения входных характеристик Т (13) и (12), обусловленные влиянием эффекта Эрли. 1 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях с малыми значениями эдс смещения нуля (ОУ)).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах [1-36], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УДЗ и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ, на их модификации выдано более 200 патентов. Предлагаемое изобретение относится к данному подклассу устройств.

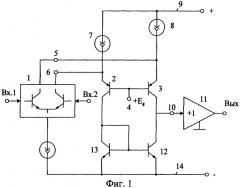

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный дифференциальный усилитель (КДУ), описанный в патенте США №6696888, содержащий входной дифференциальный каскад 1, первый 2 и второй 3 выходные транзисторы промежуточного каскада, базы которых подключены к источнику напряжения смещения 4, а эмиттеры соединены с выходами 5 и 6 входного дифференциального каскада 1 и через первый 7 и второй 8 токостабилизирующие двухполюсники связаны с шиной первого 9 источника питания, причем коллектор второго выходного транзистора 3 промежуточного каскада соединен со входом 10 буферного усилителя 11 и коллектором третьего выходного транзистора 12 промежуточного каскада, эмиттер которого соединен с эмиттером четвертого 13 выходного транзистора промежуточного каскада и шиной второго источника питания 14, а база подключена к базе четвертого 13 выходного транзистора промежуточного каскада и коллектору первого 2 выходного транзистора промежуточного каскада.

Существенный недостаток известного КДУ (фиг.1) состоит в том, что он имеет сравнительно большое значение эдс смещения нуля, что отрицательно сказывается на статических параметрах различных аналоговых устройств на его основе.

Основная цель предлагаемого изобретения состоит в уменьшении эдс смещения нуля.

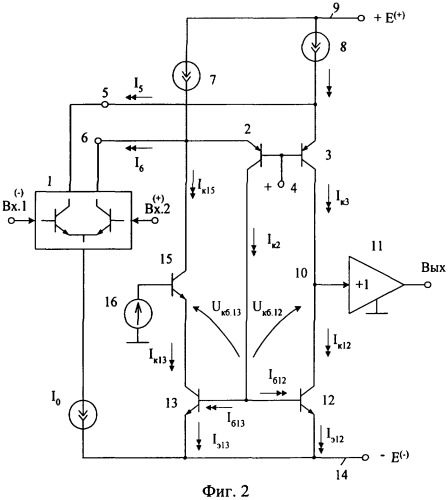

Поставленная цель достигается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1, первый 2 и второй 3 выходные транзисторы промежуточного каскада, базы которых подключены к источнику напряжения смещения 4, а эмиттеры соединены с выходами 5 и 6 входного дифференциального каскада 1 и через первый 7 и второй 8 токостабилизирующие двухполюсники связаны с шиной первого 9 источника питания, причем коллектор второго выходного транзистора 3 промежуточного каскада соединен со входом 10 буферного усилителя 11 и коллектором третьего выходного транзистора 12 промежуточного каскада, эмиттер которого соединен с эмиттером четвертого 13 выходного транзистора промежуточного каскада и шиной второго источника питания 14, а база подключена к базе четвертого 13 выходного транзистора промежуточного каскада и коллектору первого 2 выходного транзистора промежуточного каскада, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор 15, база которого соединена с общей шиной первого 9 и второго 14 источников питания, коллектор подключен к эмиттеру первого 2 выходного транзистора промежуточного каскада, а эмиттер - соединен с коллектором четвертого 13 выходного транзистора промежуточного каскада.

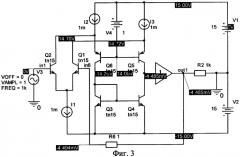

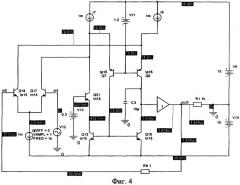

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения. На фиг.3 и фиг.4 показаны схемы известного (фиг.3) и заявляемого (фиг.4) устройств в среде компьютерного моделирования PSpice, а на фиг.5, фиг.6 - зависимость эдс смещения нуля КДУ фиг.4 от напряжения дополнительного источника смещения 16 в крупном (фиг.5) и мелком (фиг.6) масштабах.

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1, первый 2 и второй 3 выходные транзисторы промежуточного каскада, базы которых подключены к источнику напряжения смещения 4, а эмиттеры соединены с выходами 5 и 6 входного дифференциального каскада 1 и через первый 7 и второй 8 токостабилизирующие двухполюсники связаны с шиной первого 9 источника питания, причем коллектор второго выходного транзистора 3 промежуточного каскада соединен со входом 10 буферного усилителя 11 и коллектором третьего выходного транзистора 12 промежуточного каскада, эмиттер которого соединен с эмиттером четвертого 13 выходного транзистора промежуточного каскада и шиной второго источника питания 14, а база подключена к базе четвертого 13 выходного транзистора промежуточного каскада и коллектору первого 2 выходного транзистора промежуточного каскада. В схему введен дополнительный транзистор 15, база которого соединена с общей шиной первого 9 и второго 14 источников питания, коллектор подключен к эмиттеру первого 2 выходного транзистора промежуточного каскада, а эмиттер - соединен с коллектором четвертого 13 выходного транзистора промежуточного каскада.

В частном случае база дополнительного транзистора 15 может быть соединена с общей шиной источников питания 9 и 14 через дополнительный источник напряжения смещения 16 (фиг.2).

Рассмотрим работу заявляемого каскодного дифференциального усилителя на примере анализа схемы фиг.2.

Статический режим по току КДУ фиг.2 устанавливается источником опорного тока I0 в эмиттерной цепи входного дифференциального каскада 1 и токостабилизирующими двухполюсниками 7 и 8. При этом токи в элементах схемы, соответствующие обозначениям на чертеже фиг.2, представляют собой следующее:

где Iкij - коллекторные токи транзисторов;

I5, I6 - статические токи выходов 5 и 6 КДУ;

I0 - статический ток общей эмиттерной цепи входного дифференциального каскада 1;

β13≈β12 - статические коэффициенты передачи по току базы транзисторов 13 и 12.

Если β13=β12>>1, то в

Статический режим по напряжению коллектор-база транзисторов 13 и 12 (при введении 100%-ной обратной связи с выхода буферного усилителя 11 на инвертирующий вход Вх.1(-)) зависит от напряжения на базе транзистора 15

где Е(-) - напряжение источника питания 14.

Таким образом, за счет соответствующего выбора напряжения дополнительного источника смещения E16 на уровне Е16≈Uэб.15 можно получить одинаковые напряжения Uкб.13≈Uкб.12. Это позволяет обеспечить одинаковые смещения входных характеристик транзисторов 13 и 12, обусловленные влиянием эффекта Эрли и, как следствие, устранить одну из основных причин появления напряжения смещения нуля КДУ (Есм).

Компьютерное моделирование показывает, что в схеме КДУ-прототипа систематическая составляющая эдс смещения нуля принимает достаточно большое значение: Есм.п=4,4 мВ (фиг.4).

В заявляемом устройстве численные значения Есм зависят от напряжения E16 (фиг.5, фиг.6). Если E16=0, то Eсм.3=-103,7 мкВ. При Есм.3=0,7 В, Есм.3=+133 мкВ. Наименьшие значения Есм.3=1,6 мкВ получены при Е16=0,3 В. Следовательно, в схеме фиг.2 созданы условия, при которых устраняется систематическая ошибка усиления сигналов постоянного тока, обусловленная структурными особенностями КДУ. Это позволяет рекомендовать заявляемую схему для применения в составе прецизионных интерфейсов. За счет выбора величины напряжения E16 можно в широких пределах регулировать эдс смещения нуля КДУ.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - с.74, рис.4.15, стр.98, рис.6.7.

2. Патент США №6218900, фиг.1.

3. Патентная заявка US 2002/0196079.

4. Патент США №6788143.

5. Патент США №3644838, фиг.2.

6. Патент США Re 30587.

7. Патент ЕР 1227580.

8. Патент США №6714076.

9. Патент США №5786729.

10. Патент США №5327100.

11. Патентная заявка US 2004/0090268 A1.

12. Патент США №4274061.

13. Патент США №5422600, фиг.2.

14. Патент США №6788143, фиг.2.

15. Патент США №4959622, фиг.1.

16. Патент США №4406990, фиг.4.

17. Патент США №5418491.

18. Патент США №6018268.

19. Патент США №5952882.

20. Патент США №4723111.

21. Патент США №4293824.

22. Патент США №6580325.

23. Патент США №6965266.

24. Патент США №6867643.

25. Патент США №6236270.

26. Патент США №5323121.

27. Патент США №6229394.

28. Патент США №5734296.

29. Патент США №5477190.

30. Патент США №5091701.

31. Патент США №6717474.

32. Патент США №6084475.

33. Патент США №3733559.

34. Патентная заявка US 2005/0001682 А1.

35. Патент США №6300831.

1. Каскодный дифференциальный усилитель, содержащий входной дифференциальный каскад (1), первый (2) и второй (3) выходные транзисторы промежуточного каскада, базы которых подключены к источнику напряжения смещения (4), а эмиттеры соединены с выходами (5) и (6) входного дифференциального каскада (1) и через первый (7) и второй (8) токостабилизирующие двухполюсники связаны с шиной первого (9) источника питания, причем коллектор второго выходного транзистора (3) промежуточного каскада соединен со входом (10) буферного усилителя (11) и коллектором третьего выходного транзистора (12) промежуточного каскада, эмиттер которого соединен с эмиттером четвертого (13) выходного транзистора промежуточного каскада и шиной второго источника питания (14), а база подключена к базе четвертого (13) выходного транзистора промежуточного каскада и коллектору первого (2) выходного транзистора промежуточного каскада, отличающийся тем, что в схему введен дополнительный транзистор (15), база которого соединена с общей шиной первого (9) и второго (14) источников питания, коллектор подключен к эмиттеру первого (2) выходного транзистора промежуточного каскада, а эмиттер - соединен с коллектором четвертого (13) выходного транзистора промежуточного каскада.

2. Устройство по п.1, отличающееся тем, что база дополнительного транзистора (15) соединена с общей шиной источников питания (9) и (14) через дополнительный источник напряжения смещения (16).