Каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)). Каскодный дифференциальный усилитель (КДУ) содержит входной параллельно-балансный каскад (1) на входных транзисторах (Т) (2 и 3), базы которых являются входами (4 и 5) КДУ, а эмиттеры связаны с источником опорного тока (ИОТ) (6), эмиттеры Т (7, 8 и 9) с объединенными базами соединены через токостабилизирующие двухполюсники (ТД) (10, 11 и 12) с шиной первого (13) источника питания (ИП), причем эмиттер Т (7) соединен с коллектором Т (2), эмиттер Т (8) соединен с коллектором Т (3), а коллекторы Т (7 и 8) являются первым (14) и вторым (15) выходами КДУ. В схему для повышения коэффициента ослабления входного синфазного сигнала введены дополнительные Т (16) и (17), базы которых соединены с соответствующими базами Т (2) и Т (3), коллекторы подключены к эмиттеру Т (9), эмиттеры связаны с ИОТ (6). Причем ИОТ (6) выполнен на Т (18), эмиттер которого соединен с шиной второго ИП (19), база подключена к коллектору Т (9), а объединенные базы Т (7, 8 и 9) соединены с дополнительным источником напряжения смещения (20). 1 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах [1-35], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УД3 и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 200 патентов. Предлагаемое изобретение относится к данному подклассу устройств.

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный дифференциальный усилитель (КДУ), описанный в патенте США №6456162 (фиг.3), содержащий входной параллельно-балансный каскад 1 на первом 2 и втором 3 входных транзисторах, базы которых являются входами 4 и 5 каскодного дифференциального усилителя, а эмиттеры связаны с источником опорного тока 6, первый 7, второй 8 и третий 9 выходные транзисторы с объединенными базами, эмиттеры которых соединены через первый 10, второй 11 и третий 12 токостабилизирующие двухполюсники с шиной первого 13 источника питания, причем эмиттер первого выходного транзистора 7 соединен с коллектором первого входного транзистора 2, эмиттер второго выходного транзистора 8 соединен с коллектором второго входного транзистора 3, а коллекторы первого 7 и второго 8 выходных транзисторов являются первым 14 и вторым 15 выходами каскодного дифференциального усилителя.

Существенный недостаток известного КДУ (фиг.1) состоит в том, что он имеет сравнительно небольшой коэффициент ослабления входного синфазного сигнала (Кос.сф), что отрицательно сказывается на погрешностях неинвертирующих решающих усилителей и компараторов на его основе.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входного синфазного сигнала.

Поставленная цель достигается тем, что в каскодном дифференциальном усилителе (фиг.1), содержащем входной параллельно-балансный каскад 1 на первом 2 и втором 3 входных транзисторах, базы которых являются входами 4 и 5 каскодного дифференциального усилителя, а эмиттеры связаны с источником опорного тока 6, первый 7, второй 8 и третий 9 выходные транзисторы с объединенными базами, эмиттеры которых соединены через первый 10, второй 11 и третий 12 токостабилизирующие двухполюсники с шиной первого 13 источника питания, причем эмиттер первого выходного транзистора 7 соединен с коллектором первого входного транзистора 2, эмиттер второго выходного транзистора 8 соединен с коллектором второго входного транзистора 3, а коллекторы первого 7 и второго 8 выходных транзисторов являются первым 14 и вторым 15 выходами каскодного дифференциального усилителя, предусмотрены новые элементы и связи - в схему введены первый 16 и второй 17 дополнительные транзисторы, базы которых соединены с соответствующими базами первого 2 и второго 3 входных транзисторов, коллекторы подключены к эмиттеру третьего выходного транзистора 9, эмиттеры связаны с источником опорного тока 6, причем источник опорного тока 6 выполнен на вспомогательном транзисторе 18, эмиттер которого соединен с шиной второго источника питания 19, база подключена к коллектору третьего 9 выходного транзистора, а объединенные базы первого 7, второго 8 и третьего 9 выходных транзисторов соединены с дополнительным источником напряжения смещения 20.

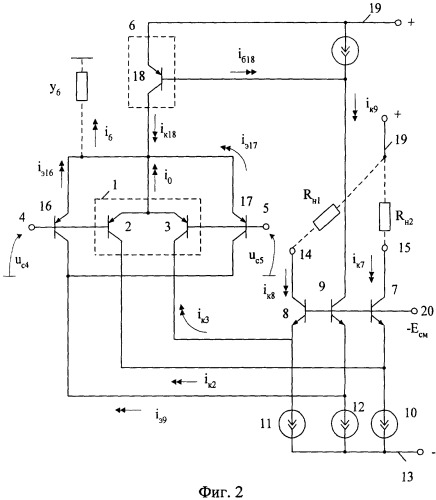

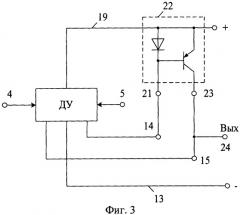

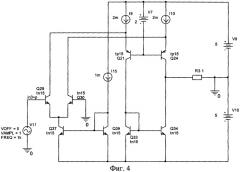

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения. На фиг.3 показана схема каскодного дифференциального усилителя, соответствующая п.2 формулы изобретения. На фиг.4 и 5 показаны схемы заявляемого (фиг.5) и известного (фиг.4) устройств в среде компьютерного моделирования PSpice, а на фиг.6 - частотные зависимости коэффициента ослабления синфазных сигналов сравниваемых КДУ.

Дифференциальный усилитель (фиг.2) содержит входной параллельно-балансный каскад 1 на первом 2 и втором 3 входных транзисторах, базы которых являются входами 4 и 5 каскодного дифференциального усилителя, а эмиттеры связаны с источником опорного тока 6, первый 7, второй 8 и третий 9 выходные транзисторы с объединенными базами, эмиттеры которых соединены через первый 10, второй 11 и третий 12 токостабилизирующие двухполюсники с шиной первого 13 источника питания, причем эмиттер первого выходного транзистора 7 соединен с коллектором первого входного транзистора 2, эмиттер второго выходного транзистора 8 соединен с коллектором второго входного транзистора 3, а коллекторы первого 7 и второго 8 выходных транзисторов являются первым 14 и вторым 15 выходами каскодного дифференциального усилителя. В схему введены первый 16 и второй 17 дополнительные транзисторы, базы которых соединены с соответствующими базами первого 2 и второго 3 входных транзисторов, коллекторы подключены к эмиттеру третьего выходного транзистора 9, эмиттеры связаны с источником опорного тока 6, причем источник опорного тока 6 выполнен на вспомогательном транзисторе 18, эмиттер которого соединен с шиной второго источника питания 19, база подключена к коллектору третьего 9 выходного транзистора, а объединенные базы первого 7, второго 8 и третьего 9 выходных транзисторов соединены с дополнительным источником напряжения смещения 20.

В частном случае первый выход 14 каскодного дифференциального усилителя (фиг.3) соединен со входом 21 токового зеркала 22, коллекторный выход которого 23 связан со вторым 15 выходом каскодного дифференциального усилителя и является основным выходом 24 каскодного дифференциального усилителя.

Рассмотрим работу заявляемого каскодного дифференциального усилителя на примере анализа схемы фиг.2.

Существенный недостаток известных КДУ - недостаточно высокое ослабление синфазных сигналов, которое существенно зависит от величины выходной проводимости (у6) источников опорного тока 6 (ИОТ). Для биполярных транзисторов выходная проводимость у6 зависит от напряжения Эрли (Uэ) и статического тока коллектора (Iк18) транзистора 18 следующим образом

Для современных интегральных транзисторов Uэ=20÷40 В, то есть при миллиамперных токах (Iк18=1 мА) численные значения выходного сопротивления ИОТ не велики (Rвых.6=у6≈20÷40 кОм), что отрицательно сказывается на ослаблении синфазных сигналов.

В заявляемом устройстве при наличии синфазной составляющей у двух сигналов uc4=uc5=uс изменяется ток через проводимость у6

Для эмиттерной цепи входного каскада 1 (при идентичных транзисторах 2, 3, 16 и 17) можно составить следующую систему уравнений

где β18 - коэффициент усиления по току базы транзистора 18, входящего в структуру источника опорного тока 6.

Подставляя в уравнение (2) сумму токов (3) можно получить, что приращение суммарного тока эмиттерной цепи входного дифференциального каскада 1

Таким образом в схеме фиг.2 создаются условия, при которых выходные токи КДУ iк8(iк7), обусловленные синфазным сигналом, существенно ослабляются

Поэтому выходное напряжение КДУ, обусловленное входным синфазным сигналом, выделяемое, например, на нагрузке Rн1, будет мало

Следовательно, коэффициент передачи синфазного сигнала со входа КДУ на выход 14 в заявляемой схеме существенно уменьшается

Так как при идентичных статических токах эмиттера транзисторов 2 и 3 в заявляемом и известном КДУ коэффициент усиления дифференциального сигнала одинаков, то из этого следует, что Кос.сф в схеме фиг.2 в Nc раз лучше, чем в схеме фиг.4, где Nс≈β18>>1. Данные выводы подтверждаются результатами компьютерного моделирования, которые показывают, что предлагаемое техническое решение улучшает Кос.сф более чем на порядок (28 дБ).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - с.74, рис.4.15, стр.98, рис.6.7.

2. Патент США №6218900, фиг.1.

3. Патентная заявка US 2002/0196079.

4. Патент США №6788143.

5. Патент США №3644838, фиг.2.

6. Патент США Re 30587.

7. Патент ЕР 1227580.

8. Патент США №6714076.

9. Патент США №5786729.

10. Патент США №5327100.

11. Патентная заявка US 2004/0090268 A1.

12. Патент США №4274061.

13. Патент США №5422600, фиг.2.

14. Патент США №6788143, фиг.2.

15. Патент США №4959622, фиг.1.

16. Патент США №4406990, фиг.4.

17. Патент США №5418491.

18. Патент США №6018268.

19. Патент США №5952882.

20. Патент США №4723111.

21. Патент США №4293824.

22. Патент США №6580325.

23. Патент США №6965266.

24. Патент США №6867643.

25. Патент США №6236270.

26. Патент США №5323121.

27. Патент США №6229394.

28. Патент США №5734296.

29. Патент США №5477190.

30. Патент США №5091701.

31. Патент США №6717474.

32. Патент США №6084475.

33. Патент США №3733559.

34. Патентная заявка US 2005/0001682 A1.

35. Патент США №6300831.

1. Каскодный дифференциальный усилитель, содержащий входной параллельно-балансный каскад (1) на первом (2) и втором (3) входных транзисторах, базы которых являются входами (4) и (5) каскодного дифференциального усилителя, а эмиттеры - связаны с источником опорного тока (6), первый (7), второй (8) и третий (9) выходные транзисторы с объединенными базами, эмиттеры которых соединены через первый (10), второй (11) и третий (12) токостабилизирующие двухполюсники с шиной первого (13) источника питания, причем эмиттер первого выходного транзистора (7) соединен с коллектором первого входного транзистора (2), эмиттер второго выходного транзистора (8) соединен с коллектором второго входного транзистора (3), а коллекторы первого (7) и второго (8) выходных транзисторов являются первым (14) и вторым (15) выходами каскодного дифференциального усилителя, отличающийся тем, что в схему введены первый (16) и второй (17) дополнительные транзисторы, базы которых соединены с соответствующими базами первого (2) и второго (3) входных транзисторов, коллекторы подключены к эмиттеру третьего выходного транзистора (9), эмиттеры связаны с источником опорного тока (6), причем источник опорного тока (6) выполнен на вспомогательном транзисторе (18), эмиттер которого соединен с шиной второго источника питания (19), база подключена к коллектору третьего (9) выходного транзистора, а объединенные базы первого (7), второго (8) и третьего (9) выходных транзисторов соединены с дополнительным источником напряжения смещения (20).

2. Устройство по п.1, отличающееся тем, что первый выход (14) каскодного дифференциального усилителя соединен со входом (21) токового зеркала (22), коллекторный выход которого (23) связан со вторым (15) выходом каскодного дифференциального усилителя и является основным выходом (24) каскодного дифференциального усилителя.