Плоскопанельный дисплей

Иллюстрации

Показать всеИзобретение относится к аппаратным средствам персонального компьютера (ПК) и может быть использовано в качестве плоскопанельного дисплея для монитора и телевизора. Технический результат - получение инерционности ячеек отображения менее 1 мс, 256 градаций каждого из основных цветов, увеличение яркости изображения пикселов каждым элементом матрицы экрана и получение разрешения на экране в формате HDTV, достигается введением в каждый элемент матрицы экрана своего сверхъяркого светодиода белого излучения и преобразованием каждой ячейкой матрицы белого излучения светодиода в излучение своего цвета соответственно его 8-разрядному коду восьмью полупрозрачными микрозеркалами, использованием пьезоэлементов в качестве исполнительных элементов, объединением триад ячеек в одном корпусе. 6 ил.

Реферат

Изобретение относится к аппаратным средствам персонального компьютера /ПК/ и может быть использовано в качестве плоскопанельного дисплея для монитора и телевизора. За прототип принят плоскопанельный экран по технологии жидких кристаллов - ЖК-экран [1 c.486-490], представляющий совокупность ЖК-ячеек, каждая из которых не генерирует свет, а лишь управляет интенсивностью проходящего света, поэтому используются постоянно излучающие лампы подсветки. ЖК-ячейки представляют электронно-управляемые светофильтры цветов R, G, В. Принцип действия основан на эффекте поляризации световой волны. При отсутствии внешнего электрического поля поступающий в ЖК-ячейку свет проходит ее, ЖК-ячейка прозрачна. При подаче на подложки ячейки напряжения между ними возникает электрическое поле [2 c.474], молекулы жидкокристаллического вещества располагаются параллельно силовым линиям поля, плоскость поляризации света не совпадает с плоскостью поляризация анализатора, ЖК-ячейка становится непрозрачна. Для получения цветного изображения пиксела ЖК-ячейки объединяются в триады, каждая ячейка снабжается цветным светофильтром одного из цветов R, G, В. Каждый элемент матрицы экрана образован тремя тонкопленочными транзисторами и триадой управляемых ими ЖК-ячеек. Изменяя уровень вправляющего сигнала, подаваемого на транзистор, регулируется яркость выходного излучения с триады ЖК-ячеек. Недостатками прототипа - ЖК-экрана являются: инерционность в управлении ЖК-ячейками до 10 мс [4 с.357, 360], невозможность точно управлять цветопередачей жидкого кристалла, отсюда более узкий цветовой диапазон, воспроизводимый Ж-экраном [3 с.145], ограничение размеров ЖК-экрана из-за сложности технологии их изготовления [2 c.476], "недостаточно черный" черный цвет на экране из-за пропуска ячейками света от ламп подсветки и при закрытых ячейках 5 с.2, 6 с.33], необходимость подстраивать по частоте и фазе сигналы развертки ЖК-экрана каждый раз при подключении к новому ПК [2 c.483], в виду инерционности ячеек частота кадров ограничена частотой 80 Гц [2 с.484].

Цель изобретения - снижение инерционности элементов матрицы экрана, увеличение яркости изображения на экране, достоверная полнота цветопередачи изображения, получение разрешения соответственно формату HDTV.

Техническим результатом являются получение инерционности ячеек менее 1 мс, глубина цветопередачи соответствует 8-разрядным кодам цветовых сигналов /16 миллионов оттенков цветов/, увеличение яркости изображения пикселов каждым элементом матрицы экрана и получение разрешения на экране по формату HDTV /1920×1080/. Результат по увеличению яркости и полноты цветопередачи достигается введением для каждого элемента матрицы экрана своего сверхъяркого светодиода белого излучения и преобразованием каждой ячейкой матрицы белого излучения светодиода в излучение своего цвета соответственно его 8-разрядного коду восьмью полупрозрачными микрозеркалами и суммированием излучений трех цветов от полупрозрачных микрозеркал в изображение пиксела соответствующего цветового тона на экране, снижение инерционности ячеек менее 1 мс достигается использованием пьезоэлементов в качестве исполнительных элементов, получение разрешения в формате HDTV выполняется объединением триад ячеек в одном корпусе. Элемент матрицы /триада ячеек/ включает светодиод белого излучения, три ячейки, объединенные в одном непрозрачном корпусе, каждая из ячеек включает цветной светофильтр, микролинзу, являющуюся микрообъективом, расположенные против микролинзы последовательно друг за другом полупрозрачные микрозеркала по числу разрядов в коде, и общее зеркало, принимающее отраженные от всех полупрозрачных микрозеркал цветовые лучи и направляющее суммарное излучение в выходную микролинзу, формирующую изображение пиксела.

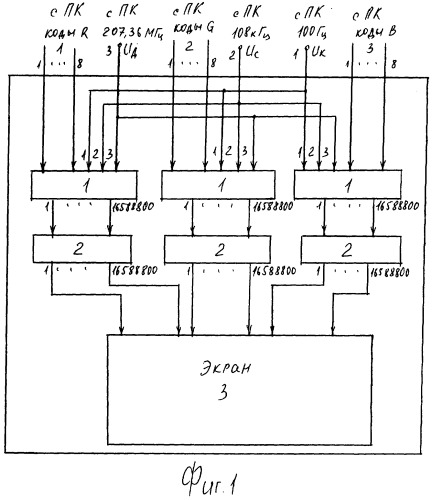

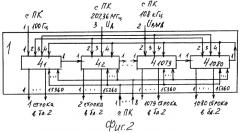

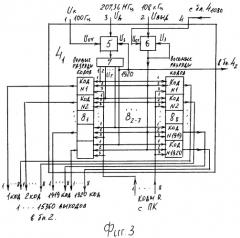

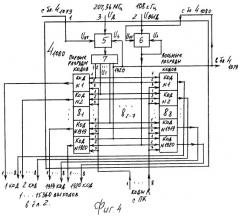

Сущность изобретения в том, что в плоскопанельный дисплей, содержащий плоскопанельный экран из триад ячеек по числу пикселов в экране, введены три канала цветовых сигналов R, G, В, каждый из которых включает последовательно соединенные накопитель кодов кадра и блок формирователей импульсов, выходы которых подключены к соответствующим входам плоскопанельного экрана, каждая триада ячеек включает светодиод белого излучения, три ячейки объединены в одном непрозрачном корпусе, и каждая ячейка включает последовательно расположенные соответствующего цвета светофильтр и микролинзу и расположенные против нее последовательно друг за другом полупрозрачные микрозеркала по числу разрядов в коде, пьезоэлементы по числу полупрозрачных микрозеркал, общее зеркало и выходную микролинзу. Функциональная схема плоскопанельного дисплея показана на фиг.1, накопитель кодов кадра на фиг.2, блок регистров на фиг.3 и 4, элемент матрицы /триада ячеек/ на фиг.5, верхняя ячейка триады на фиг.6 вид сверху.

Плоскопанельный дисплей воспроизводит с видеоадаптера ПК видеорежим 1920×1080×100 Гц. Частота дискретизации кодов цветовых сигналов, поступающая с ПК, составляет:

fД=1920×1080×100 Гц=207,36 МГц

где 1920 - число отсчетов в строке,

1080 - число строк в кадре,

100 Гц - частота кадров.

Частота строк fс=1080×100 Гц=108 кГц,

период строки /длительность строки/ .

Длительность кадра .

Плоскопанельный дисплей включает /фиг.1/ три идентичных канала цветовых сигналов R, G, В, каждый из которых содержит последовательно соединенные накопитель 1 кодов кадра и блок 2 формирователей импульсов, выходы которых подключены к соответствующим входам плоскопанельного экрана 3. Блок 2 формирователей импульсов содержит импульсных усилителей по числу пикселов в экране и по числу разрядов в коде /1920×1080×8/, всего импульсных усилителей 16588800 штук. Накопители 1 кодов кадра /фиг.3/ идентичны, каждый включает блоки 4 регистров по числу строк в кадре: 41-1080. Информационным входом накопителя 1 кодов кадра являются поразрядно объединенные 1-8 входы блоков 41-41080 регистров. Управляющими входами являются: первым - первый управляющий вход Uк 100 Гц блока 41 регистров, вторым - объединенные вторые управляющие входы Uвыд 108 кГц блоков 4 регистров, третьим - третьи объединенные управляющие входы Uд 207,36 МГц блоков 4 регистров. Каждый управляющий выход предыдущего блока 4 регистров является первым управляющим входом последующего блока 4 регистров. Управляющий выход последнего блока 41080 регистров подключен параллельно к четвертым управляющим входам всех блоков регистров. Первым, вторым, третьим информационными входами плоскопанельного дисплея являются информационные входы накопителей 1 кодов кадра, а первым, вторым и третьим управляющими входами дисплея являются объединенные первые управляющие входы накопителей 1 кодов кадра, объединенные вторые управляющие входы их и третьи объединенные управляющие входы накопителей 1 кодов кадра. Блоки регистров 4 идентичны /фиг.4 и 3/, каждый включает первый 5 и второй 6 ключи, распределитель 7 импульсов и восемь регистров 81-8. Информационным входом блока 4 являются поразрядно объединенные третьи входы разрядов восьми регистров 8. Выходами блока 4 являются параллельные выходы всех разрядов восьми регистров 81-8, всего 15360 выходов /1920×8/ с каждого блока 4 регистров. Управляющими входами являются: первым - первый управляющий вход первого ключа 5, вторым - сигнальный вход Uвыд второго ключа 6, третьим - сигнальный вход Uд первого ключа 5, четвертым - первый управляющий вход второго ключа 6, подключенный к управляющему выходу последнего блока 41080 регистров. Последний /1920/ выход распределителя 7 импульсов подключен к второму управляющему входу ключа 5 и является управляющим выходом блока 4 регистров в следующий блок 4, подключен к первому управляющему входу первого ключа 5 в блоке 42. Выход первого ключа 5 подключен к входу распределителя 7 импульсов, выходы которого последовательно с первого по 1920-й подключены к первым управляющим входам разрядов параллельно восьми регистров 81-8. Выход второго ключа 6 подключен параллельно к вторым управляющим входам всех разрядов восьми регистров 8. Блок 2 формирователей импульсов предназначен для формирования параллельно поступающих импульсов разрядов всех кодов кадра по длительности и амплитуде: по длительности импульсы соответствуют длительности кадра 10 мс, по амплитуде соответствуют напряжению для срабатывания пьезоэлементов 19 в ячейках /фиг.6/. Экран 3 представляет совокупность 2073600 триад ячеек. Каждая триада ячеек включает /фиг.5 и 6/ светодиод 9 белого излучения, а три ячейки объединены в одном непрозрачном корпусе 22, имеющем форму прямоугольного параллелепипеда. Каждая ячейка включает последовательно расположенные цветной светофильтр 10 /11, 12/ и микролинзу 13 /14, 15/, являющуюся микрообъективом ячейки, и расположенные против микролинзы последовательно друг за другом полупрозрачные микрозеркала 16 /17, 18/, которых по числу разрядов в коде 8 штук, включает пьезоэлементы 19 /фиг.6/ по числу полупрозрачных микрозеркал /8 штук/. Один торец каждого пьезоэлемента закреплен неподвижно в корпусе триады ячеек и имеет стравляющий вход, второй подвижный торец пьезоэлемента 19 соответствующим образом прикреплен к своему полупрозрачному микрозеркалу 16 /17, 18/. В выходном торце корпуса расположена выходная микролинза 21, в фокальной плоскости которой расположено общее зеркало 20. Каждое полупрозрачное зеркало имеет два фиксированных положения: в первом положении микрозеркала ячейки оптически соединены сквозь друг друга, через свою микролинзу и цветной светофильтр с излучающей стороной светодиода 9, во втором положении каждое полупрозрачное микрозеркало оптически соединяет светодиод с общим зеркалом 20. Принцип действия ячейки основан на том, что каждое впереди расположенное полупрозрачное микрозеркало 16 /17,18/ пропускает на следующее за ним поток излучения, ослабленный в два раза, что соответствует принципу двоичного кода. Для полупрозрачных микрозеркал применяется светоделительное покрытие, выполняющее отношение отраженного потока к пропущенному как 1:0,5, т.е. каждое микрозеркало пропускает поток излучения в 50% от отраженного потока. [7, с.223]. Для исключения посторонних отражений /световых помех/ на общее зеркало 20 стенки корпуса 22 имеют светопоглощающее покрытие. Ячейки в триаде работают идентично, излучающая плоскость светодиода 9 расположена в фокальных плоскостях микролинз 13, 14, 15. Излучение светодиода 9 через цветные светофильтры 10, 11, 12 собираются каждой микролинзой и поступают на первые полупрозрачные микрозеркала 16, 17, 18 /фиг.5/. В отсутствие управляющих сигналов на входах пьезоэлементов 19 микрозеркала находятся в первом фиксированном положении. Поток излучения проходит сквозь все восемь полупрозрачных микрозеркал, но не отражается на общее зеркало 20. Каждое полупрозрачное микрозеркало в ячейке ослабляет проходящий через него поток в 2 раза. После первого микрозеркала поток ослабляется в 2 раза, после второго - в 4 раза, после третьего - в 8 раз, четвертого - в 16 раз, пятого - в 32 раза, шестого - в 64 раза и после седьмого в 128 раз. Выполняется порядок двоичного кода. При поступлении кодов цветовых сигналов с блока 1 импульсы разрядов кодов усиливаются по амплитуде и формируются длительностью в 10 мс и поступают на управляющие входы пьезоэлементов 19 ячеек триады. Исполнительным перемещением пьезоэлемента принимается изгиб. В качестве пьезоэлементов применяются трубчатые пьезоэлементы, работающие на изгиб, их достоинство прочность и надежность [8, c.27]. При изгибе свободный конец пьезоэлемента перемещается на соответствующее число микрометров и переводит свое микрозеркало во второе положение, при котором отраженное излучение с него поступает на общее зеркало 20, а 50% излучения проходит как и прежде сквозь микрозеркало на следующее за ним. Верхняя ячейка выполняет преобразование "код R - яркость красного цвета", средняя ячейка выполняет преобразование "код G - яркость зеленого цвета", нижняя ячейка - ″код В - яркость синего излучения". Микрозеркала трех ячеек, на пьезоэлементы которых поступили управляющие импульсы, переходят во второе положение и направляют отраженное излучение трех цветовых сигналов на общее зеркало 20. Выходная микролинза производит сбор суммарного результирующего излучения с общего зеркала 20 и формирует изображение пиксела на стекле экрана 3. Вариант размеров триады: диаметры микролинз по 0,25 мм, цветных светофильтров по 0,25 мм, размер полупрозрачных микрозеркал 0,2×0,2 мм, общего зеркала 20 0,5×0,5 мм, размер торцов корпуса 0,8×0,8 мм. Длина корпуса 22 определяется расстоянием от последнего полупрозрачного микрозеркала до заднего торца светодиода 9 составит 2...3 см. Исполнение элементов матриц и их юстировка требует высокой точности и методов нанотехнологии, как, например, в [2, с.531].

При размере торцов корпуса триады 0,8×0,8 мм размеры экрана 3 составят: по горизонтали 1920×0,8 мм = 1536 мм,

по вертикали 1080×0,8 мм = 864 мм,

по диагонали 1760 мм или 69 дюймов. Формат кадра 16:9.

С соответствующих информационных выходов видеоадаптера ПК на информационные входы накопителей 1 кодов кадра поступают в параллельном виде 8-разрядные коды цветовых сигналов R, G, В.

С соответствующих выходов видеоадаптера ПК на первый, второй и третий управляющие входы накопителей 1 кодов кадра поступают соответственно синхроимпульсы частоты кадров Uк 100 Гц, частоты строк Uc 108 кГц и частоты дискретизации кодов Uд 207,36 МГц. За время первого периода кадра регистры 8 в блоках 4 /фиг.3, 4/ заполняются кодами первого кадра. Каждый блок 4 регистров сосредотачивает коды одной строки, поэтому их в блоках 1 по 1080 штук. За период кадра в каждом блоке 1 накапливаются по 2073600 кодов. Управляющий импульс, поступающий на четвертые управляющие входы блоков 4 регистров, выдает из них синхронно и параллельно все коды в блоки 2 и обнуляет разряды регистров 8 для приема ими кодов следующего кадра. Импульсы разрядов кодов в блоке 2 формируются по амплитуде и длительности и поступают на управляющие входы пьезоэлементов соответствующих ячеек экрана 3. Триады ячеек формируют цветовой тон и яркость пикселов на экране 3. Увеличение яркости пикселов на экране против прототипа достигается применением для каждой триады ячеек сверхъяркого светодиода белого излучения с силой света 3...10 кд, например L-53MWC фирмы Kingbright [9 с.45]. Число светодиодов равно числу триад в экране, т.е. 2073600. Цветовой тон и яркость пикселов постоянна в течение длительности кадра /10 мс/. В это время идет накопление блоками 1 кодов второго кадра, и процессы повторяются.

Работа блока 4 регистров, фиг.3, 4.

Сигналы разрядов кодов поступают на третьи входы разрядов регистров 81-8 с соответствующего цифрового выхода DVI видеоадаптера ПК. Заполнение регистров 8 кодами строки начинается с открытием импульсом 100 Гц первого ключа 5, который пропускает импульсы Uд 207,36 МГц на вход распределителя 7 импульсов. Тактовый импульсы с выхода блока 7 последовательно поступают параллельно на первые управляющие входы разрядов восьми регистров 8.

Сигналы первых разрядов кодов поступают в разряды первого регистра 81, вторых разрядов кодов поступают в разряды второго регистра 82 и т.д. восьмых разрядов кодов в разряды регистра 88. По заполнении регистров 8 сигнал с последнего /1920/ выхода блока 7 закрывает первый ключ 5 и в качестве управляющего выходного сигнала открывает ключ 5 во втором блоке 42 регистров, регистры которого аналогично заполняются кодами второй строки. Таким образом, последовательно за время кадра 10 мс заполняются регистры 8 всех блоков 41-1080 регистров. По заполнении регистров 8 во всех блоках 4 управляющий выходной сигнал с блока 41080 открывает вторые ключи 6 во всех блоках 4 регистров. Ключи 6 пропускают один импульс Uвыд /108 кГц/, который выдает одновременно и синхронно из всех блоков 4 все коды кадра /2073600/ в блоки 2 формирователей импульсов и обнуляет разряды регистров 8 для приема кодов следующего кадра.

Работа дисплея.

На 1-3 управляющие входы плоскопанельного дисплея с соответствующих выходов видеоадаптера ПК поступают синхроимпульсы Uк кадров /100 Гц/, синхроимпульсы строк Uc /108 кГц/ и импульсы Uд дискретизации /207,36 МГц/. С соответствующих информационных выходов DVI видеоадаптера ПК на 1-3 информационные входы дисплея поступают в параллельном виде 8-разрядные коды сигналов R, G, B.

За первый период кадра накопители 1 кодов производят накопление кодов первого кадра, по окончании которого следует выдача синхронно и параллельно всех кодов кадра в блоки 2 формирователей импульсов, а накопители 1 кодов кадра ведут накопление кодов следующего кадра. Сигналы разрядов первого кадра параллельно поступают в свои формирователи импульсов блока 2, где формируются по амплитуде и длительности и поступают на входы пьезоэлементов 19 ячеек триад. 2073600 триад ячеек образуют на экране 2073600 пикселов, соответствующей яркости и цветового тона, создающих цветное изображение. Ввиду непосредственного преобразования в ячейках 8-разрядного кода в цветовые излучения цветовая передача изображения максимально приближается к расчетному значению 16777216 цветовых оттенков. Идентичность электронных схем в блоках 1 и 2 упрощает выполнение их в интегральном исполнении. Учитывая наличие большого числа соединительных проводов между накопителями 1 кодов кадра, блоками 2 формирователей импульсов и от них к ячейкам триад экрана /16588800×3=49766400/, заявляемый плоскопанельный дисплей для долголетней надежной работы лучше выполнять единой и неразборной конструкцией. В заявляемом плоскопанельном дисплее применением пьезоэлементов в качестве исполнительных элементов достигается снижение инерционности ячеек от 0,1 мс и менее, применением для каждой триады ячеек в качестве источника излучения сверхъяркого светодиода белого свечения достигается увеличение яркости изображения, а полнота цветопередачи осуществляется в ячейках применением преобразования "код - яркость излучения".

Источники информации

1. В.И.Мураховский. Устройство компьютера. М, 2003, с.486-490, прототип.

2. Колесников О.В., Шишигин М.В. Аппаратные средства РС. 5-е изд-е, СПб, 2004, с.474, 476, 477, 478, 483, 484, 531.

3. Энциклопедический справочник: персональный компьютер. М., 2004, с.145.

4. В.Мураховский. Железо ПК. Новые возможности. СПб, 2005, с.357, 360.

5. "Домашний компьютер". М., 2006, с.2.

6. "Домашний компьютер". М., 2006, с.33.

7. Б.Н.Бегунов, Н.П.Заказнов. Теория оптических систем. М., 1973, с.223.

8. А.Ф.Плонский. ВД.Теаро. Пьезоэлектроника. М., 1979, с.26, 27.

9. "Радио" № 2, 2006, с.45.

10. И.В.Фридлянд, В.Г.Сошников. Системы автоматического регулирования в устройствах видеозаписи. М., 1988, с.118, с.122.

Плоскопанельный дисплей, содержащий плоскопанельный экран из триад ячеек по числу пикселов в экране, отличающийся тем, что в него введены три канала цветовых сигналов R, G, В, каждый из которых включает последовательно соединенные накопитель кодов кадра и блок формирователей импульсов, выходы которых подключены к соответствующим входам плоскопанельного экрана, первым, вторым и третьим информационными входами плоскопанельного дисплея являются 1-8 информационные входы накопителей кодов кадра каждого канала цветового сигнала, подключенные к соответствующим информационным выходам видеоадаптера персонального компьютера (ПК), первым, вторым и третьим управляющими входами плоскопанельного дисплея являются объединенные соответственно первые, вторые и третьи управляющие входы накопителей кодов кадра, подключенные соответственно к первому, второму и третьему управляющим выходам видеоадаптера ПК, накопители кодов кадра идентичны, каждый включает блоки регистров по числу строк в кадре, информационным входом каждого накопителя кодов кадра являются поразрядно объединенные 1-8 входы блоков регистров, первым управляющим входом является первый управляющий вход первого блока регистров, вторым - объединенные вторые управляющие входы блоков регистров, третьим - объединенные третьи управляющие входы блоков регистров, каждый управляющий выход предыдущего блока регистров является первым управляющим входом последующего блока регистров, управляющий выход последнего блока регистров подключен параллельно к четвертым управляющим входам всех блоков регистров, выходами накопителя кодов кадра являются выходы всех блоков регистров, блоки регистров идентичны, каждый включает первый и второй ключи, распределитель импульсов и восемь регистров, 1-8 информационными входами блока регистров являются поразрядно объединенные третьи входы разрядов восьми регистров, выходы всех разрядов восьми регистров являются параллельными выходами блока регистров, первым управляющим входом блока регистров является первый управляющий вход первого ключа, вторым управляющим входом является сигнальный вход второго ключа, третьим - сигнальный вход первого ключа, четвертым - первый управляющий вход второго ключа, подключенный к управляющему выходу последнего блока регистров, выход первого ключа подключен к входу распределителя импульсов, выходы которого последовательно с первого по последний подключены к первым управляющим входам разрядов параллельно восьми регистров, последний выход также подключен к второму управляющему входу первого ключа и является управляющим выходом блока регистров, выход второго ключа подключен параллельно к вторым управляющим входам всех разрядов восьми регистров и к второму управляющему входу второго ключа, каждый блок формирователей импульсов включает формирователей импульсов по числу триад ячеек в экране и по числу разрядов в коде, каждая триада ячеек включает светодиод белого излучения, три ячейки объединены в непрозрачном корпусе формой прямоугольного параллелепипеда, и каждая ячейка включает последовательно расположенные цветной светофильтр и микролинзу и расположенные против нее последовательно друг за другом полупрозрачные микрозеркала по числу разрядов в коде, пьезоэлементы по числу полупрозрачных микрозеркал, один торец каждого пьезоэлемента закреплен неподвижно в корпусе триады ячеек и имеет управляющий вход, подключенный к соответствующему выходу в блоке формирователей импульсов, второй подвижный торец соответствующим образом прикреплен к своему полупрозрачному микрозеркалу, в триаду ячеек введены общее зеркало и в выходном торце корпуса выходная микро-линза, в передней фокальной плоскости которой расположено общее зеркало, каждое полупрозрачное микрозеркало имеет два фиксированных положения: в первом положении полупрозрачные микрозеркала ячейки оптически соединены сквозь друг друга через свою микролинзу и цветной светофильтр с излучающей стороной светодиода, во втором положении каждое полупрозрачное микрозеркало оптически соединяет светодиод с общим зеркалом.