Идентификатор частотных характеристик

Иллюстрации

Показать всеИдентификатор частотных характеристик предназначен для экспериментального исследования динамических (частотных) характеристик систем автоматического управления. Техническим результатом изобретения является расширение функциональных возможностей устройства. Идентификатор состоит из генератора импульсов, блока формирования воздействия, в котором происходит изменение периода (частоты), формы, масштабирование и преобразование сигнала; блока коммутации данных, в котором происходит преобразование аналогового сигнала в цифровой, наложение цифровых сигналов и их преобразование в требуемый формат; блока коммутации адреса; оперативного запоминающего устройства данных; блока микропроцессорного вычислителя, в котором выполняется арифметическая и логическая обработка информации по программе, хранящейся в постоянном запоминающем устройстве этого блока; блока преобразования кода и усиления и печатающего устройства. 5 ил.

Реферат

Предлагаемое изобретение относится к области автоматического управления и регулирования и предназначено для экспериментального исследования динамических (частотных) характеристик систем автоматического управления.

Известно устройство для определения частотных характеристик (ЧХ) по переходному процессу, возникшему при действии треугольного зондирующего импульса. Однако это устройство имеет ограниченные функциональные возможности (см., например, авт. св. СССР №287160, кл. G05B 23/02, 1969 г.).

Это устройство не решает задачу определения частотных характеристик для цифровых систем или устройств, а также не позволяет определять ЧХ в условиях больших помех.

Прототипом предлагаемого устройства является устройство (идентификатор) по авт. св. СССР №599255, кл. G05B 23/02, 1975 г.), предназначенное для идентификации динамических (частотных) характеристик при приложении к исследуемой системе или устройству импульсных воздействий, содержащее генератор, печатающее устройство вместе с блоком преобразования кода и усиления.

Однако и это устройство имеет ограниченные функциональные возможности, в частности не решаются задачи определения частотных характеристик цифровых систем или устройств (приборов) и ЧХ в условиях больших помех.

Техническим результатом данного изобретения является расширение функциональных возможностей идентификатора частотных характеристик. Заявленный технический результат достигается тем, что идентификатор частотных характеристик, содержащий генератор, печатающее устройство вместе с блоком преобразования кода и усиления, в соответствии с изобретением дополнительно содержит блок формирования воздействия, вход которого соединен с генератором, а выход соединен с блоком коммутации данных, вход которого используется для подключения к выходу исследуемой системы, вход которой подключается к выходу блока формирования воздействия; блок коммутации адреса и оперативное запоминающее устройство данных, связанные на входе с блоком коммутации данных, а на выходе с блоком микропроцессорного вычислителя, причем между собой блок коммутации адреса и оперативное запоминающее устройство данных соединены последовательно, а также блок микропроцессорного вычислителя с постоянным запоминающим устройством, в котором хранятся сменные программы алгоритмов вычисления, блок микропроцессорного вычислителя, связанный на выходе с блоком преобразования кода и усиления, который в свою очередь связан с входом печатающего устройства.

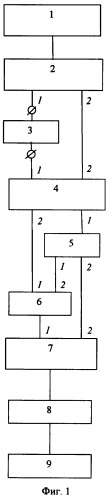

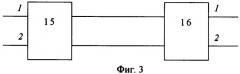

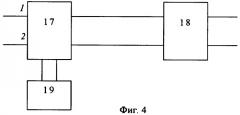

Далее предлагаемое изобретение поясняется более подробно с использованием прилагаемых схемных фигур, где: на фиг.1 показан схематично идентификатор частотных характеристик, на фиг.2 - блок формирования воздействия, на фиг.3 - блок коммутации данных, на фиг.4 - блок микропроцессорного вычислителя и на фиг.5 - блок преобразования кода и усиления.

Идентификатор частотных характеристик (фиг.1) состоит из генератора 1, блока формирования воздействия (БФВ) 2, соединенных последовательно, выход 1 последнего соединен с входом исследуемой системы (ИС) 3, выход которой подключен к входу 1 блока коммутации данных (БКД) 4, вход 2 которого соединен с выходом 2 БФВ. Выход 1 БКД 4 связан с входом блока коммутации адреса (БКА) 5, а выход 2 БКД 4 связан с входом 1 оперативного запоминающего устройства данных (ОЗУ Д) 6. Выход 1 БКА 5 соединен с входом 2 ОЗУ Д 6, а выход 2 с входом 2 блока микропроцессорного вычислителя (БМВ) 7, вход 1 которого подключен к выходу ОЗУ Д 6. Выход БМВ 7 соединен с входом блока преобразования кода и усиления (БПКУ) 8, выход которого связан с входом печатающего устройства (ПУ) 9.

Идентификатор частотных характеристик содержит следующие блоки.

Генератор 1 - кварцевый генератор импульсов.

Блок формирования воздействия 2 (фиг.2) включает:

а) схему формирования 10 симметричного треугольного импульса, построенную на базе 12-разрядного счетчика с элементами управления на триггерах,

б) схему преобразования 11 симметричного треугольного импульса в синусоидальный импульс - на базе большой интегральной схемы постоянного запоминающего устройства (БИС ПЗУ);

в) схему коммутации 12 цифровых сигналов, состоящую из элементов 2И/ИЛИ-НЕ, функционально представляющих собой мультиплексоры на два входа;

г) схему масштабирования 13 цифрового сигнала, построенную на регистрах сдвига;

д) схему преобразования 14 цифра-аналог - на базе интегральной схемы (ИС) 12-разрядного цифроаналогового преобразователя (ЦАП).

Блок коммутации данных 4 (фиг.3) содержит:

а) схему преобразования 15 аналог-цифра, построенную на ИС 12-разрядного ЦАП,

б) схему коммутации 16 каналов и выбора формата данных - на базе регистров транзистор-транзисторной логики (ТТЛ).

Блок коммутации адреса 5 построен на двоичных счетчиках с элементами управления на триггерах.

Оперативное запоминающее устройство данных 6 реализуется на микросхемах памяти.

Блок микропроцессорного вычислителя 7 (фиг.4) состоит из:

а) микропроцессорного вычислителя 17, построенного на однокристальном микропроцессоре,

б) схемы синхронизации и управления 18 - на большой интегральной схеме (БИС) программируемого адаптера;

в) постоянной памяти 19, реализуемой на большой интегральной схеме расширенного формата постоянного запоминающего устройства (БИС РФ ПЗУ).

Блок преобразования кода и усиления 8 (фиг.5) включает:

а) схемы регистров данных 20, построенных на регистрах ТТЛ,

б) схемы преобразования кода и усиления 21 - на базе БИС ПЗУ.

Печатающее устройство 9 - электрифицированная пишущая машинка.

Идентификатор ЧХ работает следующим образом.

Последовательность импульсов с выхода генератора 1 поступает на вход блока формирования воздействия БФВ 2, в котором происходит изменение периода (частоты), формы, масштабирование и преобразование сигнала. Сигнал (аналоговый или цифровой) с выхода 1 БФВ 2 подается на вход исследуемой системы 3, а с выхода 2 на вход блока коммутации данных БКД 4, на вход 1 которого поступает сигнал отклика с выхода исследуемой системы 3. В БКД 4 происходит преобразование (аналогового сигнала в цифровой), наложение цифровых сигналов и их преобразование в требуемый формат для передачи в оперативное запоминающее устройство данных ОЗУ Д 6. Содержимое из ОЗУ Д 6 считывается в блок микропроцессорного вычислителя БМВ 7 по адресу, код которого формирует блок коммутации адреса БКА 5. Блок микропроцессорного вычислителя БМВ 7 выполняет арифметическую и логическую обработку информации из ОЗУ Д 6 по программе, хранящейся в постоянном запоминающем устройстве (ПЗУ) БМВ 7.

Далее приведены отдельные алгоритмы программ вычисления.

Идентификатор для определения частотных характеристик, содержащий генератор, печатающее устройство вместе с блоком преобразования кода и усиления, отличающийся тем, что он содержит блок формирования воздействия, который на входе соединен с генератором, а на выходе с блоком коммутации данных, вход которого используется для подключения к выходу исследуемой системы, вход которой подключается к выходу блока формирования воздействия; блок коммутации адреса и оперативное запоминающее устройство данных на входе связаны с блоком коммутации данных, а на выходе с блоком микропроцессорного вычислителя, причем между собой блок коммутации адреса и оперативное запоминающее устройство данных соединены последовательно; блок преобразования кода и усиления на входе соединен с блоком микропроцессорного вычислителя, в котором хранятся сменные программы алгоритмов вычисления, а на выходе связан с входом печатающего устройства.