Двухтактный каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)). Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов. Двухтактный каскодный дифференциальный усилитель (ДКДУ) содержит первый и второй дифференциальные каскады (1) и (6) на n-p-n и p-n-p транзисторах (Т) соответственно, базы которых подключены ко входам (2) и (3) ДКДУ, а эмиттеры связаны с коллектором выходного Т, соответственно первого и второго источников опорного тока (4) и (7), согласованных, соответственно, с шиной (5) отрицательного и шиной (8) положительного источников питания (ИП), базы выходных p-n-p Т (9) и (10) объединены и подключены к положительному источнику напряжения смещения (ИНС) (11), базы выходных n-p-n Т (12) и (13) объединены и подключены к отрицательному ИНС (14), причем эмиттеры Т (9) и (10) через токостабилизирующие двухполюсники (ТД) (16) и (18) соответственно соединены с шиной (8) ИП, а также с токоввыми выходами (15) и (17) каскада (1), эмиттеры Т (12) и (13) соединены соответственно с первым (19) и вторым (21) токовыми выходами каскада (6) и через соответственно третий (20) и четвертый (22) ТД связаны с шиной (5) ИП, коллекторы Т (10) и (13) подключены к выходу (23) ДКДУ. Коллектор p-n-p Т (9) соединен с базой выходного Т первого (4) ИОТ, а коллектор первого n-p-n Т (12) соединен с базой выходного Т второго (7) ИОП. 5 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ), реализованных на основе двух параллельно включенных дифференциальных каскадов (ДК) с источниками опорного тока в эмиттерных цепях входных транзисторов (так называемые «dual input stage» или «комплементарных дифференциальных усилителей (КДУ)») [1-20]. По такой архитектуре, на модификации которой выдано около 100 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.). Однако в практических схемах известных КДУ коэффициент ослабления входного синфазного сигнала (Кос.сф) получается небольшим (50÷60 ДБ). Это связано с тем, что выходное сопротивление классических источников опорного тока на основе токовых зеркал, обеспечивающих наиболее широкий диапазон изменения входных синфазных напряжений КДУ, оказывается небольшим (30÷60 кОм).

Действительно, выходное сопротивление (Rвых) современных транзисторов в схеме с общим эмиттером определяется напряжением Эрли [21] (Uэ) и статическим током эмиттера Iэ:

Необходимо подчеркнуть, что уменьшение горизонтальных и вертикальных размеров интегральных биполярных транзисторов, направленное на увеличение граничной частоты усиления и степени интеграции микросхем, приводит к более сильному влиянию коллекторного напряжения на толщину активной базы, результатом чего является уменьшение напряжения Эрли и выходного дифференциального сопротивления. Так, если напряжение Эрли для дискретных n-р-n транзисторов составляет Uэ.N=80...200 В, а р-n-р - Uэ.N=40...150 В, то транзисторы современных интегральных устройств имеют гораздо меньшее напряжение Эрли: Uэ.N=20...40 B, Uэ.P=15...30 В [21].

Кроме этого, напряжение Эрли интегральных горизонтальных р-n-р транзисторов (Uэ.P) обычно меньше, чем для транзисторов n-р-n Uэ.NP<Uэ.N. Это объясняется тем, что концентрация примеси в базе горизонтального р-n-р транзистора (эпитаксиальная пленка n-типа) меньше, чем в р-базе транзисторов n-p-n [21].

Таким образом, небольшие напряжения Эрли современных транзисторов не позволяют получить (при миллиамперных токах) их выходные сопротивления больше 10-30 кОм, что отрицательно сказывается на многих параметрах КДУ и, в частности, на его коэффициенте ослабления входного синфазного сигнала (Кос.сф.).

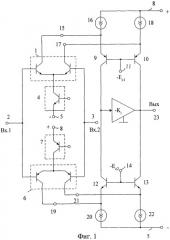

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте фирмы Motorola US 5153529, содержащий первый дифференциальный каскад 1 на n-р-n транзисторах, базы которых подключены ко входам 2 и 3 двухтактного каскодного дифференциального усилителя, а эмиттеры связаны с коллектором выходного транзистора первого источника опорного тока 4, согласованного с шиной 5 отрицательного источника питания, второй дифференциальный каскад 6 на р-n-р транзисторах, базы которых подключены ко входам 2 и 3 двухтактного каскодного дифференциального усилителя, а эмиттеры связаны с коллектором выходного транзистора второго источника опорного тока 7, согласованного с шиной 8 положительного источника питания, первый 9 и второй 10 выходные р-n-р транзисторы, базы которых объединены и подключены к положительному источнику напряжения смещения 11, первый 12 и второй 13 выходные n-р-n транзисторы, базы которых объединены и подключены к отрицательному источнику напряжения смещения 14, причем эмиттер первого 9 выходного р-n-р транзистора соединен с первым 15 токовым выходом первого дифференциального каскада 1 на n-р-n транзисторах и через первый 16 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер второго 10 выходного р-n-р транзистора связан со вторым 17 токовым выходом первого дифференциального каскада 1 на n-р-n транзисторах и через второй 18 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер первого 12 выходного n-р-n транзистора соединен с первым 19 токовым выходом второго дифференциального каскада 6 на р-n-р транзисторах и через третий 20 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, эмиттер второго 13 выходного n-р-n транзистора соединен со вторым 21 токовым выходом второго дифференциального каскада 6 на р-n-р транзисторах и через четвертый 22 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, коллектор второго 10 выходного р-n-р транзистора и коллектор второго 13 выходного n-р-n транзистора подключены к выходу 23 двухтактного каскодного дифференциального усилителя.

Существенный недостаток известного КДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов, которое определяется коэффициентом

где Ку>>1 - коэффициент усиления входного дифференциального сигнала КДУ;

Ксф.<<1 - коэффициент передачи входного синфазного сигнала КДУ.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов.

Поставленная цель достигается тем, что в дифференциальном усилителе по фиг.1, содержащем первый дифференциальный каскад 1 на n-р-n транзисторах, базы которых подключены ко входам 2 и 3 двухтактного каскодного дифференциального усилителя, а эмиттеры связаны с коллектором выходного транзистора первого источника опорного тока 4, согласованного с шиной 5 отрицательного источника питания, второй дифференциальный каскад 6 на р-n-р транзисторах, базы которых подключены ко входам 2 и 3 двухтактного каскодного дифференциального усилителя, а эмиттеры связаны с коллектором выходного транзистора второго источника опорного тока 7, согласованного с шиной 8 положительного источника питания, первый 9 и второй 10 выходные р-n-р транзисторы, базы которых объединены и подключены к положительному источнику напряжения смещения 11, первый 12 и второй 13 выходные n-р-n транзисторы, базы которых объединены и подключены к отрицательному источнику напряжения смещения 14, причем эмиттер первого 9 выходного р-n-р транзистора соединен с первым 15 токовым выходом первого дифференциального каскада 1 на n-р-n транзисторах и через первый 16 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер второго 10 выходного р-n-р транзистора связан со вторым 17 токовым выходом первого дифференциального каскада 1 на n-р-n транзисторах и через второй 18 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер первого 12 выходного n-р-n транзистора соединен с первым 19 токовым выходом второго дифференциального каскада 6 на р-n-р транзисторах и через третий 20 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, эмиттер второго 13 выходного n-р-n транзистора соединен со вторым 21 токовым выходом второго дифференциального каскада 6 на р-n-р транзисторах и через четвертый 22 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, коллектор второго 10 выходного р-n-р транзистора и коллектор второго 13 выходного n-р-n транзистора подключены к выходу 23 двухтактного каскодного дифференциального усилителя, предусмотрены новые связи - коллектор первого 9 выходного р-n-р транзистора соединен с базой выходного транзистора первого 4 источника опорного тока, а коллектор первого 12 выходного р-n-р транзистора соединен с базой выходного транзистора второго 7 источника опорного тока.

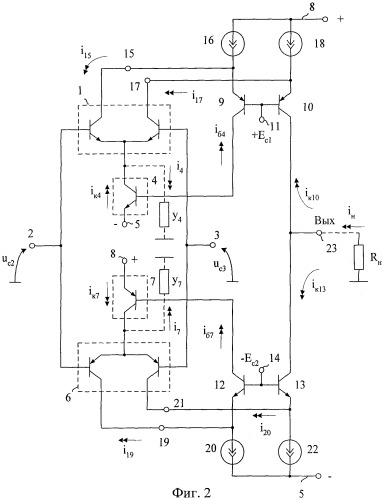

Схема заявляемого устройства в соответствии с формулой изобретения показана на чертеже фиг.2.

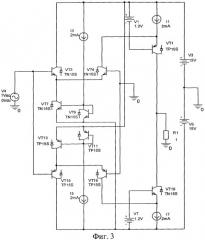

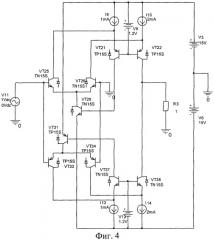

На фиг.3 - 4 показана схема известного (фиг.3) и заявляемого (фиг.4) устройств в среде компьютерного моделирования PSpice для режима расчета коэффициента передачи по дифференциальному сигналу (Ку.). Для измерения Ксф входы 2 и 3 объединяются.

На фиг.5 показаны результаты компьютерного моделирования Кос.сф. сравниваемых КДУ фиг.3 и фиг.4 в среде PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Дифференциальный усилитель фиг.2 содержит первый дифференциальный каскад 1 на n-р-n транзисторах, базы которых подключены ко входам 2 и 3 двухтактного каскодного дифференциального усилителя, а эмиттеры связаны с коллектором выходного транзистора первого источника опорного тока 4, согласованного с шиной 5 отрицательного источника питания, второй дифференциальный каскад 6 на р-n-р транзисторах, базы которых подключены ко входам 2 и 3 двухтактного каскодного дифференциального усилителя, а эмиттеры связаны с коллектором выходного транзистора второго источника опорного тока 7, согласованного с шиной 8 положительного источника питания, первый 9 и второй 10 выходные р-n-р транзисторы, базы которых объединены и подключены к положительному источнику напряжения смещения 11, первый 12 и второй 13 выходные n-р-n транзисторы, базы которых объединены и подключены к отрицательному источнику напряжения смещения 14, причем эмиттер первого 9 выходного р-n-р транзистора соединен с первым 15 токовым выходом первого дифференциального каскада 1 на n-р-n транзисторах и через первый 16 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер второго 10 выходного р-n-р транзистора связан со вторым 17 токовым выходом первого дифференциального каскада 1 на n-р-n транзисторах и через второй 18 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер первого 12 выходного n-р-n транзистора соединен с первым 19 токовым выходом второго дифференциального каскада 6 на р-n-р транзисторах и через третий 20 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, эмиттер второго 13 выходного n-р-n транзистора соединен со вторым 21 токовым выходом второго дифференциального каскада 6 на р-n-р транзисторах и через четвертый 22 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, коллектор второго 10 выходного р-n-р транзистора и коллектор второго 13 выходного n-р-n транзистора подключены к выходу 23 двухтактного каскодного дифференциального усилителя. Коллектор первого 9 выходного р-n-р транзистора соединен с базой выходного транзистора первого 4 источника опорного тока, а коллектор первого 12 выходного р-n-р транзистора соединен с базой выходного транзистора второго 7 источника опорного тока.

Выходные проводимости транзисторов первого 4 и второго 7 источников опорного тока отражены на фиг.2 элементами у4, у7, на которых выделяется синфазная составляющая входных сигналов uc=uc2=uc3.

Рассмотрим работу заявляемого ДУ по фиг.2.

При изменении синфазного сигнала на входах 2 и 3 uc=uc2=uc3 (например uc=5 В) на величину uc изменяются напряжения на коллекторах транзисторов, входящих в источники опорного тока 4 и 7.

Это приводит к изменению токов через выходные проводимости y4 и y7

На основании первого закона Кирхгофа для токов в схеме фиг.2 справедливы следующие соотношения:

где β4≈β7>>1 коэффициент усиления по току базы транзисторов, входящих в структуру источников опорного тока 4 и 7.

Из уравнений (3)-(12) при β4≈β7 можно найти токи коллекторов выходных транзисторов 10 и 13, ток и напряжение на нагрузке Rн:

Таким образом, коэффициент передачи синфазного сигнала со входов 2 и 3 на выход КДУ по фиг.2

где β=β4≈β7.

Следовательно, при одинаковых коэффициентах усиления дифференциального сигнала сравниваемых КДУ и одинаковых статических режимах схема фиг.2 имеет в Nc-раз лучшее ослабление синфазных сигналов, чем КДУ-прототип, где

Компьютерное моделирование Кос.сф заявляемого и известного КДУ на моделях интегральных транзисторов ФГУП НПП «Пульсар» подтверждает полученные выше теоретические выводы: Кос.сф. улучшается на 35 дБ, т.е. более чем в 50 раз.

Следует заметить, что повышение Кос.сф в заявляемом устройстве обеспечивается без ухудшения энергетических характеристик (токопотребления), а также диапазона изменения входных синфазных сигналов (Uc.max).

Кроме этого КДУ фиг.2 может работать при малых напряжениях питания. Это является существенным достоинством заявляемой схемы.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент РФ №2193273, H03F 3/45.

2. Патент Японии №53-25232, H03F 3/26, 98(5) А332.

3. Патент US 2001/0052818 A1, H03F, 3/45.

4. Патент Японии № JP 8222972.

5. Авт. Свид. СССР №611288.

6. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - Стр.103, Рис.6.11.

7. Патент США №6366170 B1, H03F/45.

8. Патент США №6268769, H03F/45.

9. Патент США №3974455, H03F/45.

10. Патент США №3968451, H03F/45.

11. Патент США №4837523, H03F/45.

12. Патент США №5291149, H03F/45.

13. Патент США №4636743, H03F/45.

14. Патент США №4783637, H03F/45.

15. Патент США №5515005, H03F/45.

16. Патент США №5291149, H03F/45.

17. Патент США №5140280, H03F/45.

18. Патент США №5455535, H03F/45.

19. Патент США №5523718, H03F/45.

20. Патент США №4600893, H03F/45.

21. Дворников О.В. Схемотехника биполярно-полевых аналоговых микросхем. Chip News, #10 (93), 2004, стр.41.

Двухтактный каскодный дифференциальный усилитель, содержащий первый дифференциальный каскад (1) на n-p-n транзисторах, базы которых подключены ко входам (2) и (3) двухтактного каскодного дифференциального усилителя, а эмиттеры связаны с коллектором выходного транзистора первого источника опорного тока (4), согласованного с шиной (5) отрицательного источника питания, второй дифференциальный каскад (6) на p-n-p транзисторах, базы которых подключены ко входам (2) и (3) двухтактного каскодного дифференциального усилителя, а эмиттеры связаны с коллектором выходного транзистора второго источника опорного тока (7), согласованного с шиной (8) положительного источника питания, первый (9) и второй (10) выходные p-n-p транзисторы, базы которых объединены и подключены к положительному источнику напряжения смещения (11), первый (12) и второй (13) выходные n-p-n транзисторы, базы которых объединены и подключены к отрицательному источнику напряжения смещения (14), причем эмиттер первого (9) выходного p-n-p транзистора соединен с первым (15) токовым выходом первого дифференциального каскада (1) на n-p-n транзисторах и через первый (16) токостабилизирующий двухполюсник связан с шиной (8) положительного источника питания, эмиттер второго (10) выходного p-n-p транзистора связан со вторым (17) токовым выходом первого дифференциального каскада (1) на n-p-n транзисторах и через второй (18) токостабилизирующий двухполюсник связан с шиной (8) положительного источника питания, эмиттер первого (12) выходного n-p-n транзистора соединен с первым (19) токовым выходом второго дифференциального каскада (6) на p-n-p транзисторах и через третий (20) токостабилизирующий двухполюсник связан с шиной (5) отрицательного источника питания, эмиттер второго (13) выходного n-p-n транзистора соединен со вторым (21) токовым выходом второго дифференциального каскада (6) на p-n-p транзисторах и через четвертый (22) токостабилизирующий двухполюсник связан с шиной (5) отрицательного источника питания, коллектор второго (10) выходного p-n-p транзистора и коллектор второго (13) выходного n-p-n транзистора подключены к выходу (23) двухтактного каскодного дифференциального усилителя, отличающийся тем, что коллектор первого (9) выходного p-n-p транзистора соединен с базой выходного транзистора первого (4) источника опорного тока, а коллектор первого (12) выходного n-p-n транзистора соединен с базой выходного транзистора второго (7) источника опорного тока.