Ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея

Иллюстрации

Показать всеИзобретение относится к индикаторной технике и может быть использовано для создания активно-матричных вакуумных люминесцентных дисплеев, отображающих текстовую и графическую информацию. Технический результат - улучшение качества отображения информации на активно-матричных вакуумных люминесцентных дисплеях за счет повышения яркости свечения анодов-пикселей. Достигается тем, что в ячейку управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея, содержащую управляющий и адресный n-канальные МОП транзисторы, исток управляющего транзистора соединен с анодом-пикселем, его сток - с шиной анодного питания, а затвор - с истоком адресного транзистора, сток адресного транзистора соединен со столбцовой шиной матричной адресации, а его затвор - со строчной шиной матричной адресации, введен дополнительный конденсатор, его первый вывод соединен с затвором управляющего транзистора, а его второй вывод - с анодом-пикселем, причем величина емкости дополнительного конденсатора больше суммарной величины емкостей между затвором управляющего транзистора и его стоком, подложкой и затвором адресного транзистора. Кроме того, в ячейку введены ключевой n-канальный МОП транзистор и дополнительная шина, при этом затвор этого транзистора соединен с затвором адресного транзистора, его сток - со вторым выводом дополнительного конденсатора, а исток - с дополнительной шиной; дополнительная шина соединена с подложкой. 2 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к индикаторной технике и может быть использовано для создания активно-матричных вакуумных люминесцентных дисплеев, отображающих текстовую и графическую информацию.

Известна ячейка управления пикселем активно-матричных вакуумных люминесцентных дисплеев, содержащая на подложке разряд сдвигового регистра, разряд регистра-защелки, логику «разрешения выхода», схему сдвига уровней напряжений и драйвер управления пикселем (см. www.itronise.co.jp/english/fppli/cl/l.htm).

Недостатком этой ячейки управления пикселем является большое число (не менее 20) транзисторов водной ячейке и, как следствие этого, высокая стоимость активно-матричных вакуумных люминесцентных дисплеев на их основе из-за низкого процента выхода годных активных подложек.

Наиболее близким аналогом-прототипом является ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея, содержащая управляющий и адресный n-канальные МОП транзисторы. Исток управляющего транзистора соединен с покрытым люминофором анодом-пикселем, его сток - с шиной анодного питания, а затвор - с истоком адресного транзистора. Сток адресного транзистора соединен со столбцовой шиной матричной адресации, а его затвор - со строчной шиной матричной адресации (см. патент RU №2234762, МКИ7 H01J 21/10, опубл. 20.08.2004 г.).

Недостатком конструкции этой ячейки управления пикселем является невысокое качество отображения информации на активно-матричных вакуумных люминесцентных дисплеях на их основе из-за низкой яркости свечения анодов-пикселей. Низкая яркость свечения анодов-пикселей обусловлена тем, что напряжение на аноде-пикселе ограничивается напряжением на строчной шине матричной адресации и пороговым напряжением адресного и управляющего транзисторов вследствие того, что управляющий транзистор является истоковым повторителем. Напряжение на его истоке и, следовательно, на аноде-пикселе не превышает напряжение на строчной шине матричной адресации минус удвоенное значение порогового напряжения адресного и управляющего транзисторов.

Сущность изобретения заключается в следующем.

Задача, на решение которой направлено заявляемое изобретение, заключается в улучшении качества отображения информации на активно-матричных вакуумных люминесцентных дисплеях за счет повышения яркости свечения анодов-пикселей.

Указанный технический результат при осуществлении изобретения достигается тем, что в ячейку управления анодом-пикселем активно-матричных вакуумных люминесцентных дисплеев, содержащую управляющий и адресный n-канальные МОП транзисторы, исток управляющего транзистора соединен с анодом пикселем, его сток - с шиной анодного питания, а затвор - с истоком адресного транзистора, сток адресного транзистора соединен со столбцовой шиной матричной адресации, а его затвор - со строчной шиной матричной адресации, введен дополнительно конденсатор, его первый вывод соединен с затвором управляющего транзистора, а его второй вывод - с анодом-пикселем, причем величина емкости дополнительного конденсатора больше суммарной величины емкостей между затвором управляющего транзистора и его стоком, подложкой и затвором адресного транзистора.

Кроме того, в ячейку управления анодом-пикселем активно-матричных вакуумных люминесцентных дисплеев введен ключевой n-канальный МОП транзистор и дополнительная шина, затвор этого транзистора соединен с затвором адресного транзистора, его сток - со вторым выводом дополнительного конденсатора, а исток - с дополнительной шиной. Дополнительная шина соединена с подложкой.

Размещение в ячейке управления анодом-пикселем дополнительного конденсатора параллельно истоку и затвору управляющего транзистора позволяет фиксировать у него напряжение исток-затвор и использовать его как ключ при положительном напряжении на его истоке вплоть до напряжения на шины анодного питания. Это обстоятельство устраняет ограничение напряжения на аноде-пикселе, связанное с напряжением на строчной шине матричной адресации, и тем самым позволяет увеличить яркость свечения анода-пикселя и качество отображения информации на активно-матричном вакуумном люминесцентном дисплее.

Размещение в ячейке управления анодом-пикселем дополнительного ключевого транзистора и дополнительной шины позволяет увеличить скорость заряда и разряда дополнительного конденсатора. Это обеспечивает высокую частоту регенерации изображения и исключает его мерцание, что также повышает качество отображения информации.

Соединение дополнительной шины с подложкой позволяет повысить помехоустойчивость ячейки управления анодом-пикселем, что положительно сказывается на качестве отображения информации.

Сущность изобретения поясняется графическими материалами, примером конкретного исполнения и описанием.

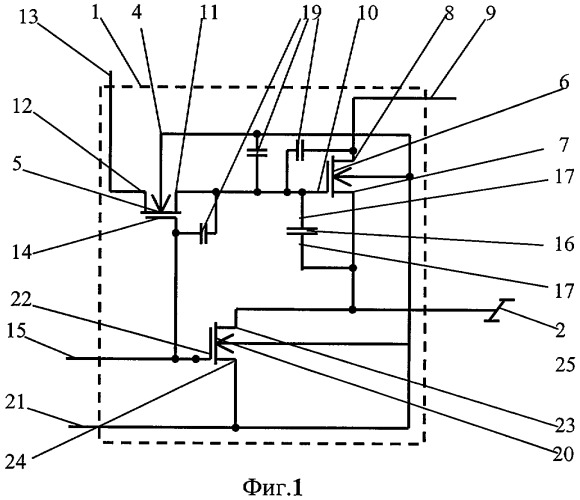

На фиг.1 показана электрическая схема ячейки управления анодом-пикселем.

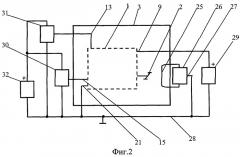

На фиг.2 изображена блок-схема включения активно-матричного вакуумного люминесцентного дисплея с предлагаемой ячейкой управления анодом-пикселем.

На чертежах введены следующие обозначения:

1 - ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея;

2 - анод-пиксель;

3 - активно-матричный вакуумный люминесцентный дисплей;

4 - подложка;

5 - адресный n-канальный МОП транзистор;

6 - управляющий n-канальный МОП транзистор;

7 - исток управляющего транзистора;

8 - сток управляющего транзистора;

9 - шина анодного питания;

10 - затвор управляющего транзистора;

11 - исток адресного транзистора;

12 - сток адресного транзистора;

13 - столбцовая шина матричной адресации;

14 - затвор адресного транзистора;

15 - строчная шина матричной адресации;

16 - дополнительный конденсатор;

17 - первый вывод дополнительного конденсатора;

18 - второй вывод дополнительного конденсатора;

19 - емкости между затвором управляющего транзистора и его стоком, подложкой и истоком адресного транзистора;

20 - ключевой n-канальный МОП транзистор;

21 - дополнительная шина;

22 - затвор ключевого транзистора;

23 - сток ключевого транзистора;

24 - исток ключевого транзистора;

25 - катод активно-матричного вакуумного люминесцентного дисплея;

26 - накальный трансформатор;

27 - средняя точка накального трансформатора;

28 - общая точка схемы;

29 - анодный источник питания;

30 - строчный драйвер;

31 - столбцовый драйвер;

32 - источник питания драйверов.

В соответствии с настоящим изобретением ячейка управления 1 анодом-пикселем 2 активно-матричного вакуумного люминесцентного дисплея 3 содержит на подложке 4 адресный n-канальный МОП транзистор 5 и управляющий n-канальный МОП транзистор 6. Исток 7 управляющего транзистора 6 соединен с анодом-пикселем 2, его сток 8 - с шиной анодного питания 9, а затвор 10 - с истоком 11 адресного транзистора 5. Сток 12 адресного транзистора 5 соединен со столбцовой шиной матричной адресации 13, а его затвор 14 - со строчной шиной матричной адресации 15. В ячейке 1 расположен дополнительный конденсатор 16, первый вывод 17 которого соединен с затвором 10 управляющего транзистора 6, а второй вывод 18 - с анодом-пикселем 2. Между затвором 10 управляющего транзистора 6 и его стоком 8, подложкой 4 и истоком 11 адресного транзистора 5 существуют емкости 19. Ячейка 1 содержит также ключевой n-канальный МОП транзистор 20 и дополнительную шину 21. Затвор 22 ключевого транзистора 20 соединен с затвором 14 адресного транзистора 5, его сток 23 - со вторым выводом 18 дополнительного конденсатора, а его исток 24 - с дополнительной шиной 21. Дополнительная шина 21 соединена с подложкой 4.

Ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея работает следующим образом (см. фиг.2).

На накаливаемый катод 25 активно-матричного вакуумного люминесцентного дисплея 3 от накального трансформатора 26 со средней точкой 27 подается напряжение накала, величина которого достаточна для эмиссии электронов. Средняя точка 27 накального трансформатора 26 соединена с общей точкой схемы 28. На шину анодного питания 9 от анодного источника питания 29 подается анодное напряжение. Подложка 4 соединена с общей точкой схемы 28. На строчную шину матричной адресации 15 с кадровой частотой от строчного драйвера 30 подаются положительные импульсы строчной адресации. В это же время для свечения анода-пикселя 2 на столбцовую шину матричной адресации 13 подается положительное напряжение от столбцового драйвера 31. Напряжение источника питания драйверов 32 меньше, чем напряжение анодного источника питания 29, но больше, чем удвоенное пороговое напряжение адресного, управляющего и ключевого транзисторов 5, 6, 20. В соответствии с этим адресный и ключевой транзисторы 5, 20 откроются. При одинаковых размерах управляющего и ключевого транзисторов 6, 20 дополнительный конденсатор 16 зарядится до напряжения источника питания драйверов 32 минус пороговое напряжение адресного транзистора 5, то есть до напряжения больше порогового напряжения управляющего транзистора 6. Первый вывод 17 дополнительного конденсатора 16 имеет положительный потенциал, а второй вывод 18 - отрицательный. После окончания положительного импульса строчной адресации адресный и ключевой транзисторы 5, 20 закроются. Величина емкости дополнительного конденсатора 16 больше суммарной величины емкостей 19 между затвором 10 управляющего транзистора 6 и его стоком 8, подложкой 4 и затвором 14 адресного транзистора 5. Поэтому разность потенциалов на дополнительном конденсаторе 16 будет сохраняться до прихода следующего положительного импульса строчной адресации. Напряжение на дополнительном конденсаторе 16 это напряжение между истоком 7 и затвором 10 управляющего транзистора 6, поэтому он будет открыт и на анод-пиксель 2 будет подана полная величина напряжения анодного источника питания 29. Яркость свечения анода-пикселя 2 не будет ограничиваться напряжением строчной адресации.

Если при подаче на строчную шину матричной адресации 15 положительного напряжения на столбцовую шину 13 подано нулевое напряжение, то дополнительный конденсатор 16 полностью разрядится, напряжение между истоком 7 и затвором 10 управляющего транзистора 6 станет равной нулю и он закроется. Свечение анода-пикселя 2 прекратится. До прихода следующего положительного импульса строчной адресации анод-пиксель 2 будет оставаться не светящимся.

Использование описываемой конструкции ячейки управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея по сравнению с известными конструкциями ячеек управления анодом-пикселем обеспечивает повышение качества отображения информации на активно-матричном вакуумном люминесцентном дисплее путем повышения яркости сечения анодов-пикселей за счет увеличения анодного напряжения.

1. Ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея, содержащая управляющий и адресный n-канальные МОП транзисторы, исток управляющего транзистора соединен с анодом-пикселем, его сток - с шиной анодного питания, а затвор - с истоком адресного транзистора, сток адресного транзистора соединен со столбцовой шиной матричной адресации, а его затвор - со строчной шиной матричной адресации, отличающаяся тем, что в ячейку введен дополнительный конденсатор, его первый вывод соединен с затвором управляющего транзистора, а его второй вывод - с анодом-пикселем, причем величина емкости дополнительного конденсатора больше суммарной величины емкостей между затвором управляющего транзистора и его стоком, подложкой и затвором адресного транзистора.

2. Ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея по п.1, отличающаяся тем, что в ячейку введены ключевой n-канальный МОП транзистор и дополнительная шина, при этом затвор этого транзистора соединен с затвором адресного транзистора, его сток - со вторым выводом дополнительного конденсатора, а исток - с дополнительной шиной.

3. Ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея по любому из пп.1 и 2, отличающаяся тем, что дополнительная шина соединена с подложкой.