Ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея

Иллюстрации

Показать всеИзобретение относится к индикаторной технике и может быть использовано для создания активно-матричных вакуумных люминесцентных дисплеев, отображающих текстовую и графическую информацию. Технический результат - улучшение качества отображения информации на активно-матричных вакуумных люминесцентных дисплеях за счет повышения яркости свечения анодов-пикселей. Достигается тем, что в ячейку управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея, содержащую управляющий и адресный n-канальные МОП транзисторы, исток управляющего транзистора соединен с анодом-пикселем, его сток - с шиной анодного питания, а затвор - с истоком адресного транзистора, сток адресного транзистора соединен со столбцовой шиной матричной адресации, а его затвор - со строчной шиной матричной адресации, введены конденсатор и дополнительная шина, при этом первый вывод конденсатора соединен с затвором управляющего транзистора, а второй вывод - с дополнительной шиной, причем величина емкости конденсатора больше суммарной величины емкостей между затвором управляющего транзистора и его стоком, истоком, подложкой и затвором адресного транзистора. 3 ил.

Реферат

Изобретение относится к индикаторной технике и может быть использовано для создания активно-матричных вакуумных люминесцентных дисплеев, отображающих текстовую и графическую информацию.

Известна ячейка управления анодом-пикселем активно-матричных вакуумных люминесцентных дисплеев, содержащая на подложке разряд сдвигового регистра, разряд регистра-защелки, логику «разрешение выхода», схему сдвига уровней напряжений и драйвер управления пикселем (см. www.inton-ise.co.jp/english/appli/cl/htm).

Недостатком этой ячейки управления анодом-пикселем является большое число (не менее 20) транзисторов в одной ячейке и, как следствие этого, высокая стоимость активно-матричных вакуумных люминесцентных дисплеев на их основе из-за низкого «процента выхода годных» активных подложек.

Наиболее близким аналогом-прототипом к предлагаемому техническому решению является ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея, содержащая управляющий и адресный n-канальные транзисторы. Исток управляющего транзистора соединен с покрытым люминофором анодом-пикселем, его сток - с шиной анодного питания, а затвор - с истоком адресного транзистора, сток адресного транзистора соединен со столбцовой шиной матричной адресации, а его затвор - со строчной шиной матричной адресации (см. патент RU №2234762, МКИ7 H01J 21/10, опубл. 20.08.2004 г.).

Недостатком конструкции этой ячейки управления анодом-пикселем является невысокое качество отображения информации на активно-матричных вакуумных люминесцентных дисплеях на их основе из-за низкой яркости свечения анодов пикселей. Низкая яркость свечения анодов пикселей обусловлена тем, что напряжение на аноде-пикселе ограничивается напряжением на строчной шине матричной адресации и пороговым напряжением адресного и управляющего транзисторов вследствие того, что управляющий транзистор является истоковым повторителем. Напряжение на его истоке и, следовательно, на аноде-пикселе не превышает напряжения на строчной шине матричной адресации минус удвоенное значение порогового напряжения адресного и управляющего транзисторов.

Сущность изобретения заключается в следующем.

Задача, на решение которой направлено заявляемое изобретение, заключается в улучшении качества отображения информации на активно-матричных вакуумных люминесцентных дисплеях за счет повышения яркости свечения анодов-пикселей.

Указанный технический результат при осуществлении изобретения достигается тем, что в ячейку управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея, содержащей управляющий и адресный n-канальные МОП транзисторы, исток управляющего транзистора соединен с анодом-пикселем, его сток - с шиной анодного питания, а затвор - с истоком адресного транзистора, сток адресного транзистора соединен со столбцовой шиной матричной адресации, а его затвор - со строчной шиной матричной адресации, введены конденсатор и дополнительная шина, при этом первый вывод конденсатора соединен с затвором управляющего транзистора, а второй вывод - с дополнительной шиной, причем величина емкости конденсатора больше суммарной величины емкостей между затвором управляющего транзистора и его стоком, истоком, подложкой и затвором адресного транзистора.

Размещение в ячейке управления анодом-пикселем дополнительно конденсатора, первый вывод которого соединен с затвором управляющего транзистора, а второй вывод - с дополнительной шиной, позволяет при высоком уровне напряжения на истоке адресного транзистора увеличить напряжение на затворе управляющего транзистора на величину, равную амплитуде импульса на дополнительной шине, и тем самым увеличить напряжение на пикселе вплоть до напряжения на шины анодного питания. При нулевом уровне напряжения на истоке адресного транзистора напряжение на затворе управляющего транзистора не изменяется и остается равным нулю. Указанные обстоятельства устраняют ограничение напряжения на аноде-пикселе, связанное с напряжением на строчной шине матричной адресации, и тем самым позволяют увеличить яркость свечения анода-пикселя и качество отображения информации на активно-матричном вакуумном люминесцентном дисплее.

Сущность изобретения поясняется графическими материалами, примером конкретного исполнения и описанием.

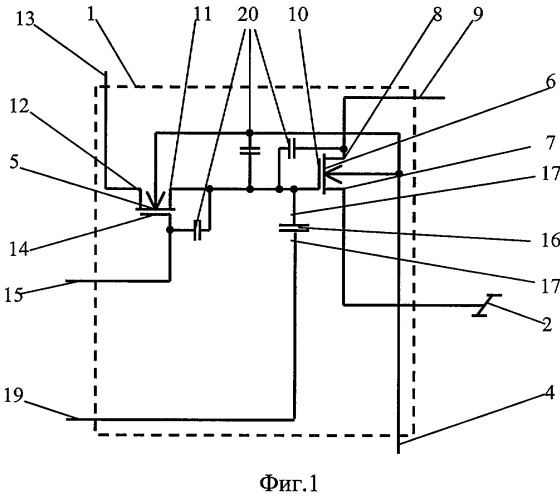

На фиг.1 показана электрическая схема ячейки управления анодом-пикселем.

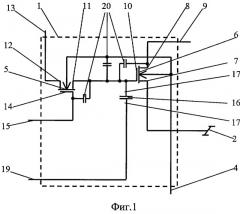

На фиг.2 изображена блок-схема включения активно-матричного вакуумного люминесцентного дисплея с предлагаемой ячейкой управления анодом-пикселем.

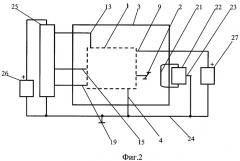

На фиг.3 изображены эпюры напряжений, которые подаются на столбцовую и строчную шины матричной адресации и дополнительную шину.

На чертежах введены следующие обозначения:

1 - ячейка управления анодом-пикселем вакуумного люминесцентного дисплея;

2 - анод-пиксель;

3 - активно-матричный вакуумный люминесцентный дисплей;

4 - подложка;

5 - адресный n-канальный МОП транзистор;

6 - управляющий n-канальный МОП транзистор;

7 - исток управляющего транзистора;

8 - сток управляющего транзистора;

9 - шина анодного питания;

10 - затвор управляющего транзистора;

11 - исток адресного транзистора;

12 - сток адресного транзистора;

13 - столбцовая шина матричной адресации;

14 - затвор адресного транзистора;

15 - строчная шина матричной адресации;

16 - конденсатор;

17 - первый вывод конденсатора;

18 - второй вывод конденсатора;

19 - дополнительная шина;

20 - емкости между затвором управляющего транзистора и его стоком, подложкой и истоком адресного транзистора;

21 - катод;

22 - накальный трансформатор;

23 - средняя точка накального трансформатора;

24 - общая точка схемы;

25 - формирователь входных сигналов;

26 - источник постоянного тока;

27 - анодный источник питания;

28 - время кадра «А»;

29 - импульс строчной адресации;

30 - длительность импульса строчной адресации;

31 - импульс столбцовой адресации;

32 - первый временный интервал;

33 - второй временный интервал;

34 - импульс на дополнительной шине;

35 - время кадра «В».

В соответствии с настоящим изобретением ячейка управления 1 анодом-пикселем 2 активно-матричного вакуумного люминесцентного дисплея 3 содержит на подложке 4 адресный n-канальный МОП транзистор 5 и управляющий n-канальный МОП транзистор 6. Исток 7 управляющего транзистора 6 соединен с анодом-пикселем 2, его сток 8 - с шиной анодного питания 9, а затвор 10 - с истоком 11 адресного транзистора 5. Сток 12 адресного транзистора 5 соединен со столбцовой шиной матричной адресации 13, а его затвор 14 - со строчной шиной матричной адресации 15. В ячейке 1 расположен дополнительно конденсатор 16, первый вывод 17 которого соединен с затвором 10 управляющего транзистора 6, а второй вывод 18 - с дополнительной шиной 19. Между затвором 10 управляющего транзистора 6 и его стоком 8, подложкой 4 и истоком 11 адресного транзистора 5 существуют емкости 20.

Ячейка работает следующим образом (см. фиг.2 и 3).

На катод 21 активно-матричного вакуумного люминесцентного дисплея 3 от накального трансформатора 22 со средней точкой 23 подается напряжение накала, величина которого достаточна для эмиссии электронов. Средняя точка 23 накального трансформатора 22 соединена с общей точкой схемы 24. Подложка 4 соединена с общей точкой схемы 24. Формирователь входных сигналов 25 подключен к источнику постоянного тока 26 напряжением Vp, причем Vp>2·Vto, где Vto - пороговое напряжение адресного и управляющего транзисторов 5, 6. Шина анодного питания 9 подключена к анодному источнику питания 27, причем величина напряжения которого Va больше, чем 2·(Vp-Vto).

Во время кадра «А» 28 на строчную шину матричной адресации 15 от формирователя входных сигналов 25 подается импульс строчной адресации 29, с длительностью 30 и амплитудой Vp. В это же время на столбцовую шину матричной адресации 13 подается импульс столбцовой адресации 31, амплитудой Vp. Длительность 30 импульса строчной адресации 29 состоит из первого временного интервала 32 и второго временного интервала 33. Во время первого временного интервала 32 на дополнительную шину 19 подается нулевое напряжение. Дополнительный конденсатор 16 заряжается до напряжения Vp-2·Vto. Во время второго временного интервала 33 на дополнительную шину 19 подается импульс 34 амплитудой Vp. На истоке 11 адресного транзистора 5 установится напряжение 2·Vp-Vto, дополнительный конденсатор 16 во время второго временного интервала 33 не разряжается, так как напряжение на истоке 11 и стоке 12 адресного транзистора 5 не меньше, чем напряжение на его затворе 14. На аноде-пикселе 2 установится напряжение 2·(Vp-Vto). По окончании импульса строчной адресации 29 на затворе 14 адресного транзистора 5 устанавливается нулевое напряжение, адресный транзистор 5 закроется до прихода следующего импульса строчной адресации 29, на аноде-пикселе 2 сохранится напряжение 2·(Vp-Vto).

Во время кадра «В» 35 на строчную шину матричной адресации 15 и дополнительную шину 19 подаются те же напряжения, что и во время кадра «А» 28. На столбцовой шине матричной адресации 13 установлено нулевое напряжение. Во время первого временного интервала 32, во время второго временного интервала 33 и по окончании импульса строчной адресации 30 напряжение на затворе 10 управляющего транзистора 6 и на аноде-пикселе 2 до следующего обращения к адресному транзистору 5 будет равно нулю.

Таким образом, во время кадра «А» на аноде-пикселе 2 будет повышенное напряжение 2·(Vp-Vto), что обуславливает высокий уровень яркости свечения анода-пикселя 2. Во время кадра «В» на аноде-пикселе 2 будет нулевое напряжение и, следовательно, полное отсутствие свечения анода-пикселя 2, что обуславливает высокий контраст изображения.

Использование описываемой конструкции ячейки управления анодом-пикселем по сравнению с известными конструкциями ячеек управления обеспечивает повышение качества отображения информации на активно-матричном вакуумном люминесцентном дисплее путем повышения яркости свечения анодов-пикселей за счет увеличения анодного напряжения.

Ячейка управления анодом-пикселем активно-матричного вакуумного люминесцентного дисплея, содержащая управляющий и адресный n-канальные МОП-транзисторы, исток управляющего транзистора соединен с анодом-пикселем, его сток - с шиной анодного питания, а затвор - с истоком адресного транзистора, сток адресного транзистора соединен со столбцовой шиной матричной адресации, а его затвор - со строчной шиной матричной адресации, отличающаяся тем, что в ячейку введены конденсатор и дополнительная шина, при этом первый вывод конденсатора соединен с затвором управляющего транзистора, а второй вывод - с дополнительной шиной, причем величина емкости конденсатора больше суммарной величины емкостей между затвором управляющего транзистора и его стоком, истоком, подложкой и затвором адресного транзистора.