Устройство для защиты интегральных микросхем от воздействия радиации

Иллюстрации

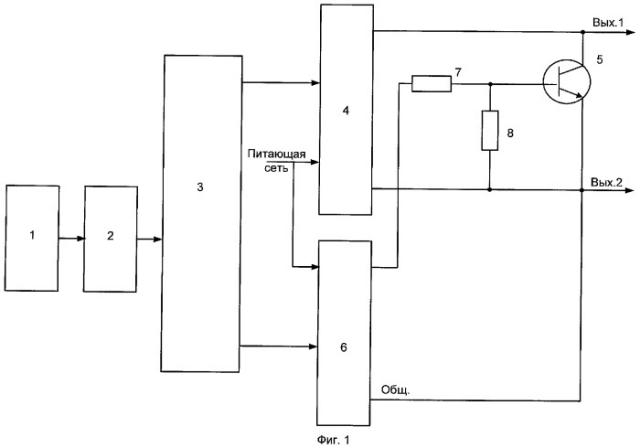

Показать всеИзобретение относится к электронике и может быть использовано в составе радиоэлектронной аппаратуры наземного, морского и аэрокосмического базирования для защиты от воздействия радиации. Техническим результатом является существенное уменьшение задержки времени срабатывания защиты, что уменьшает разрушающее воздействие радиации на микросхемы, входящие в защищаемый блок, т.к. уменьшается время нахождения защищаемых микросхем в аварийной ситуации. Устройство содержит детектор излучений (1), подключенный к усилителю сигналов детектора (2), который соединен с блоком выдачи команд управления питанием (3), один выход которого соединен с управляющим входом вторичного источника питания (ВИП) (4), другой - с управляющим входом блока включения опережающей защиты (6), выход которого через первый резистор (Р) (7) соединен с базой силового импульсного транзистора (Т) (5). Выход ВИП (4) соединен с первым выходом устройства и коллектором Т (5), между базой и эмиттером которого включен второй Р (8). Общие шины ВИП (4) и блока включения опережающей защиты (6) соединены со вторым выходом устройства и эмиттером Т (5). Входы питания этих блоков подключены к питающей сети. 2 з.п. ф-лы, 3 ил.

Реферат

Изобретение относится к электронике интегральных микросхем и может быть использовано в составе радиоэлектронной аппаратуры наземного, морского и аэрокосмического базирования для защиты от воздействия радиации (в «последнюю минуту»).

Известно устройство защиты, описанное в книге «Проектирование аналоговых интегральных схем» А.Б.Гребена / Под редакцией Е.Х.Караерова. - М.: Энергия, 1976 г., в разделе «Схемы устойчивые к радиации» на стр.240-248, рис.11-13. Известное устройство содержит дифференциальный усилитель, каскады согласования, выходной каскад. Недостатком этого устройства является невысокая устойчивость при возникновении радиации (спецвоздействий).

Известно устройство фирмы «MAXWELL TECHNOLOGIES» (США), реализованное в виде микросхемы HSN-3000, описанное в электронном каталоге фирмы MAXWEL по адресу в сети Интернет http://www.maxwell.com/microelectronics/products/index.asp.

Известное устройство содержит детектор излучений, выход которого соединен с входом усилителя сигналов детектора, подключенного ко входу таймера. Выход последнего через первый транзистор соединен с первым выходом устройства и через блок логики и второй транзистор соединен со вторым выходом устройства. Недостатком известного устройства является невысокая надежность и неустойчивость защищаемого блока в целом при воздействии радиации, обусловленные недостаточным быстродействием защиты. Это связано с задержкой выключения питания, что в свою очередь связано со временем разряда конденсаторов, подключенных к шинам питания микросхем, входящих в защищаемый блок. Таким образом, все эти явления приводят к существенному увеличению задержки срабатывания защиты, увеличению времени пребывания защищаемых микросхем в чрезвычайной ситуации и, следовательно, снижению надежности и живучести радиоэлектронной аппаратуры.

Следует подчеркнуть, что при возникновении внешней радиации открываются все транзисторы микросхем, входящих в защищаемый блок. Современные большие интегральные схемы состоят из «вертикальных» цепей, содержащих последовательно соединенные полевые транзисторы с изолированным затвором. Поэтому под влиянием радиационного воздействия возникает режим короткого замыкания по цепи питания, что приводит к выходу из строя полупроводниковых кристаллов и/или перегорание проводов, подходящих к этим кристаллам.

Задачей настоящего изобретения является повышение устойчивости и надежности микросхем, входящих в защищаемый блок в условиях возникновения спецвоздействий. Техническим результатом настоящего изобретения является существенное уменьшение задержки времени срабатывания защиты, что уменьшает разрушающее воздействие радиации на микросхемы, входящие в защищаемый блок, т.к. уменьшается время нахождения защищаемых микросхем в аварийной ситуации. Уменьшение времени срабатывания защиты имеет принципиальное значение, поскольку появление спецвоздействий может привести к перегоранию микросхем вследствие возникновения сквозных экстратоков.

К разряду спецвоздействий относятся следующие виды излучений:

- гамма лучи;

- рентгеновские лучи;

- поток нейтронов;

- поток протонов;

- электромагнитный импульс.

Защищаемыми микросхемами являются:

- микропроцессоры;

- микроконтроллеры;

- микросхемы оперативной памяти;

- микросхемы постоянной памяти;

- микросхемы АЦП и ЦАП и т.д.

Указанный технический результат достигается тем, что устройство для защиты интегральных микросхем от воздействия радиации содержит детектор излучений, усилитель сигналов детектора, блок выдачи команд управления питанием, блок включения опережающей защиты, вторичный источник питания, силовой импульсный транзистор, первый и второй резисторы, при этом выход детектора излучений соединен с входом усилителя сигналов детектора, выход которого соединен с входом блока выдачи команд управления питанием, первый выход которого соединен с управляющим входом вторичного источника питания, первый выход последнего соединен с первым выходом устройства и коллектором силового импульсного транзистора, второй выход блока выдачи команд управления питанием соединен с управляющим входом блока включения опережающей защиты, общая шина которого соединена с общей шиной вторичного источника питания, вторым выходом устройства и эмиттером силового импульсного транзистора, база которого через первый резистор соединена с выходом блока включения опережающей защиты, между базой и эмиттером транзистора подключен второй резистор, питающая сеть подключена ко входу питания вторичного источника питания и входу питания блока включения опережающей защиты.

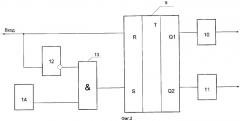

Блок выдачи команд управления питанием содержит RS-триггер, первый и второй выход которого через первую и вторую схемы согласования соединены соответственно с первым и вторым выходами блока выдачи команд управления питанием, вход блока выдачи команд управления питанием соединен с R-входом триггера и входом логического инвертора, выход последнего соединен с первым входом схемы совпадения, второй вход которой соединен с выходом генератора импульсной последовательности с большой скважностью, выход схемы совпадения соединен с S - входом триггера.

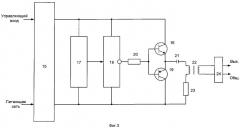

Блок включения опережающей защиты содержит линейный стабилизатор напряжения, первый вход которого соединен с борт-сетью, второй вход соединен с управляющим входом блока включения опережающей защиты, первый выход линейного стабилизатора напряжения соединен с коллектором n-p-n транзистора и с первыми входами задающего генератора волны напряжения прямоугольной формы со скважностью два и логического инвертора, второй выход линейного стабилизатора соединен с коллектором p-n-p транзистора и со вторыми входами генератора напряжения прямоугольной формы и логического инвертора, выход генератора напряжения прямоугольной формы соединен с входом логического инвертора, выход которого через третий резистор соединен с базами n-p-n и p-n-p транзисторов, эмиттеры которых соединены между собой и с первой обкладкой конденсатора, вторая обкладка конденсатора через первичную обмотку импульсного трансформатора соединена с первым выводом четвертого резистора, второй вывод которого соединен с коллектором p-n-p транзистора, вторичная обмотка импульсного трансформатора через двухполупериодный мостовой выпрямитель соединена с выходом блока включения опережающей защиты и с общей шиной.

Сущность изобретения поясняется чертежами.

На фиг.1 представлена схема устройства для защиты интегральных микросхем от воздействия радиации.

Это устройство содержит детектор 1 излучений, выход которого соединен с входом усилителя 2 сигналов детектора. Выход последнего соединен с входом блока 3 выдачи команд управления питанием. Первый выход блока выдачи команд управления питанием соединен с управляющим входом вторичного источника 4 питания. Первый выход последнего соединен с первым выходом устройства, предназначенным для подключения к входу питания защищаемого блока, и с коллектором силового импульсного транзистора 5. Второй выход блока выдачи команд управления питанием соединен с управляющим входом блока 6 включения опережающей защиты, общая шина которого соединена с общей шиной вторичного источника питания, вторым выходом устройства и эмиттером силового импульсного транзистора 5, база которого через резистор 7 соединена с выходом блока 6 включения опережающей защиты. Между базой и эмиттером упомянутого транзистора подключен резистор 8. Питающая сеть подключена к входу вторичного источника 4 питания и блоку 6 включения опережающей защиты. Второй выход устройства предназначен для подключения к общей шине защищаемого блока.

На фиг.2 представлена схема блока выдачи команд управления питанием. Он содержит RS-триггер 9, первый и второй выходы которого через первичную 10 и вторичную 11 схемы согласования соединены соответственно с первым и вторым выходами блока выдачи команд управления питанием, вход блока выдачи команд управления питанием соединен с R-входом триггера и входом логического инвертора 12. Выход последнего соединен с первым входом схемы 13 совпадения, второй вход которой соединен с выходом генератора 14 импульсной последовательности с большой скважностью, а выход схемы совпадения соединен с S-входом триггера.

На фиг.3 представлена схема блока включения опережающей защиты. Он содержит линейный стабилизатор 15 напряжения, первый вход которого соединен с питающей сетью, а второй вход соединен с управляющим входом блока включения опережающей защиты. Первый выход линейного стабилизатора напряжения соединен с коллектором n-p-n транзистора 16 и с первыми входами задающего генератора 17 волны напряжения прямоугольной формы со скважностью два и логического инвертора 18. Второй выход линейного стабилизатора соединен с коллектором p-n-p транзистора 19 и со вторыми входами задающего генератора волны напряжения прямоугольной формы и логического инвертора. Выход задающего генератора напряжения прямоугольной формы соединен с входом логического инвертора, выход которого через резистор 20 соединен с базами n-p-n и p-n-p транзисторов 16 и 19. Эмиттеры последних соединены между собой и с первой обкладкой конденсатора 21. Вторая обкладка конденсатора через первичную обмотку импульсного трансформатора 22 соединена с первым выводом резистора 23, второй вывод которого соединен с коллектором p-n-p транзистора. Вторичная обмотка импульсного трансформатора через двухполупериодный мостовой выпрямитель 24 соединена с выходом блока включения опережающей защиты и с общей шиной.

Рассмотрим состояние устройства для защиты в отсутствии спецвоздействий при поданном напряжении питающей сети. После появления этого напряжения начинает работать генератор импульсной последовательности 14, на выходе которого формируются положительные импульсы, следующие с большой скважностью. При периоде повторения 10 секунд длительность импульсов составляет одну микросекунду. Эти импульсы поступают на второй вход схемы 13 совпадения. На ее первый вход поступает положительный уровень напряжения от логического инвертора 12.

В рассматриваемом режиме на выходе детектора 1 излучений и на выходе усилителя 2 сигналы отсутствуют. На выходе инвертора 12, а также и на первом входе схемы 13 совпадения присутствует разрешающий положительный уровень напряжения, который не препятствует прохождению импульсов от генератора 14. Импульсы, поступающие на S-вход триггера 9 от выхода схемы 13 совпадения, устанавливают этот триггер в первое устойчивое состояние. При этом высокий логический уровень появляется на выходе Q1 триггера 9 и через схему 10 согласования воздействует на вторичный источник 4 питания, что обеспечивает поступление напряжения питания на защищаемый блок. В то же время низкий логический уровень с выхода Q2 триггера 9 через вторую схему 11 согласования выключает линейный стабилизатор 15 так, что его выходное напряжение становится равным нулю. Так как задающий генератор 17 и остальные элементы блока включения опережающей защиты оказываются обесточенными, какие-либо сигналы на выходе выпрямителя 24 отсутствуют. Силовой импульсный транзистор закрыт, и защищаемый блок функционирует нормально.

Теперь рассмотрим работу устройства для защиты интегральных микросхем в чрезвычайной ситуации, когда все упомянутые элементы оказываются в зоне облучения. При этом элементы системы защиты должны быть обеспечены эффективным экранированием. Такое требование может быть обеспечено, поскольку все входящие компоненты, кроме защищаемого блока, могут быть выполнены в виде микроэлектронного блока. Кроме того, эти входящие компоненты могут быть выбраны с высоким уровнем спецстойкости. Следует отметить, что стоимость таких спецстойких элементов превышает стоимость обычных компонентов на два-три порядка. Следует подчеркнуть, что уровень устойчивости того или иного устройства зависит не только от уровня спецстойкости входящих элементов, но и в не меньшей степени от более или менее удачной конфигурации принципиальной электрической схемы.

В рассматриваемой ситуации на выходе детектора 1 излучений появляется сигнал, который через усилитель 2 поступает на R-вход триггера 9 и на вход инвертора 12. При этом импульсы, поступающие на второй вход схемы 13 совпадения, блокируются сигналом, поступающим на первый вход схемы 13 совпадения. Благодаря этому на S-входе триггера 9 отсутствуют сигналы активного высокого переключающего уровня.

Под влиянием положительных сигналов на R-входе триггер 9 переключается во второе устойчивое состояние. Триггер 9 через первую схему 10 согласования выключает вторичный источник 4 питания, и через вторую схему 11 согласования включает линейный стабилизатор 15 напряжения. Вследствие этого начинает работать задающий генератор 17, с выхода которого волна напряжения прямоугольной формы через логический инвертор 18 и транзисторы 16 и 19, работающие в режиме эмиттерных повторителей, а также через конденсатор 21 и резистор 23 поступает на первичную обмотку импульсного трансформатора 22. Благодаря конденсатору 21 на первичной обмотке трансформатора 22, а также и на вторичной его обмотке формируется волна разнополярного напряжения прямоугольной формы, которая после мостового выпрямителя 24 в виде постоянного положительного напряжения подается на импульсный каскад, выполненный на транзисторе 5. Ток, открывающий транзистор 5, проходит по цепи: выход блока 6 включения опережающей защиты - резистор 7 - участок «база-эмиттер» транзистора 5 - общая шина. Все это приводит к открыванию транзистора 5, что обеспечивает опережающее отключение питания от защищаемого блока и быстрый разряд конденсаторов, расположенных на выводах питания защищаемого блока. Таким образом, реализуется защита микросхем, входящих в защищаемый блок, при том случае, когда он оказывается в зоне облучения. В рассматриваемой чрезвычайной ситуации от генератора 14 на вход схемы 13 совпадения продолжают поступать кратковременные импульсы с большим периодом следования. Эти импульсы стремятся перевести триггер 9 в первое устойчивое состояние. При этом возможны два варианта поведения устройства защиты. Если одновременно на R-вход поступает напряжение высокого уровня, которое имеет приоритет перед сигналами, поступающими на S-вход за счет реализации функции запрета, осуществляемой на схеме 13 совпадения, то триггер 9 принимает второе устойчивое состояние, соответствующее состоянию защиты. Если же активные сигналы на R-входе отсутствуют, то триггер 9 принимает первое устойчивое состояние за счет импульсов, поступающих на S-вход, что соответствует рабочему режиму. В последнем случае происходят автоматическое самовосстановление и переход защищаемого блока в штатный режим работы. Все современные цифровые большие интегральные схемы построены по технологии КМОП, т.е. на основе комплиментарных транзисторов с изолированным затвором. Такие микросхемы состоят из большого числа «вертикальных» цепей, каждая из которых содержит два или большее число упомянутых транзисторов, включенных последовательно между шинами питания. При этом в случае возникновения радиационного воздействия все транзисторы открываются, и вследствие отсутствия каких-либо ограничивающих резисторов потребляемый ток мгновенно возрастает до величины в единицы ампер. Это может привести к перегоранию проводниковых выводов от полупроводникового кристалла или же к выходу из строя самого кристалла.

В предложенном устройстве уменьшение времени срабатывания защиты оказалось возможным, в частности, благодаря наличию блока 6 включения опережающей защиты. Это позволяет уменьшить разрушение воздействия на микросхемы, входящие в защищаемый блок. В настоящем изобретении уменьшено время пребывания защищаемых микросхем в чрезвычайной ситуации, обусловленное временем разряда конденсаторов, подключенных к выводам защищаемых микросхем за счет действия разряжающего транзистора 5.

Использование предложенного устройства для защиты позволит существенно повысить надежность и живучесть защищаемых микросхем при возникновении радиационного излучения.

1. Устройство для защиты интегральных микросхем от воздействия радиации, содержащее детектор излучений, усилитель сигналов детектора, блок выдачи команд управления питанием, блок включения опережающей защиты, вторичный источник питания, силовой импульсный транзистор, первый и второй резисторы, при этом выход детектора излучений соединен с входом усилителя сигналов детектора, выход которого соединен с входом блока выдачи команд управления питанием, первый выход которого соединен с управляющим входом вторичного источника питания, первый выход последнего соединен с первым выходом устройства и коллектором силового импульсного транзистора, второй выход блока выдачи команд управления питанием соединен с управляющим входом блока включения опережающей защиты, общая шина которого соединена с общей шиной вторичного источника питания, вторым выходом устройства и эмиттером силового импульсного транзистора, база которого через первый резистор соединена с выходом блока включения опережающей защиты, между базой и эмиттером транзистора подключен второй резистор, питающая сеть подключена к входу питания вторичного источника питания и к входу питания блока включения опережающей защиты.

2. Устройство по п.1, отличающееся тем, что блок выдачи команд управления питанием содержит RS-триггер, первый и второй выход которого через первую и вторую схемы согласования соединены соответственно с первым и вторым выходами блока выдачи команд управления питанием, вход блока выдачи команд управления питанием соединен с R-входом триггера и входом логического инвертора, выход последнего соединен с первым входом схемы совпадения, второй вход которой соединен с выходом генератора импульсной последовательности с большой скважностью, выход схемы совпадения соединен с S-входом триггера.

3. Устройство по п.1, отличающееся тем, что блок включения опережающей защиты содержит линейный стабилизатор напряжения, первый вход которого соединен с питающей сетью, второй вход соединен с управляющим входом блока включения опережающей защиты, первый выход линейного стабилизатора напряжения соединен с коллектором n-p-n-транзистора и первыми входами задающего генератора волны напряжения прямоугольной формы со скважностью два и логического инвертора, второй выход линейного стабилизатора соединен с коллектором p-n-p-транзистора и вторыми входами генератора напряжения прямоугольной формы и логического инвертора, выход генератора напряжения прямоугольной формы соединен с входом логического инвертора, выход которого через третий резистор соединен с базами n-p-n- и p-n-p-транзисторов, эмиттеры которых соединены между собой и с первой обкладкой конденсатора, вторая обкладка конденсатора через первичную обмотку импульсного трансформатора соединена с первым выводом четвертого резистора, второй вывод которого соединен с коллектором p-n-p-транзистора, вторичная обмотка импульсного трансформатора через двухполупериодный мостовой выпрямитель соединена с выходом блока включения опережающей защиты и общей шиной.