Устройство слежения за частотой шумоподобных сигналов

Иллюстрации

Показать всеИзобретение относится к области радиотехники и может использоваться в приемниках шумоподобных сигналов с минимальной частотной манипуляцией. Достигаемый технический результат - повышение помехоустойчивости и точности слежения за частотой шумоподобных сигналов с минимальной частотной манипуляцией. Устройство содержит частотный дискриминатор, включающий квадратурные каналы, каждый из которых содержит входной перемножитель, интегратор и элемент задержки, аналого-цифровой преобразователь, преобразователь Гильберта, три сумматора, три вычитателя, петлевой фильтр, восемь канальных перемножителей, решающий блок, выходной перемножитель, блок формирования опорных сигналов, содержащий цифровой синтезатор отсчетов, и блок кодовой синхронизации. 2 ил.

Реферат

Изобретение относится к области радиотехники и может использоваться в приемниках шумоподобных сигналов с минимальной частотной манипуляцией.

Известно устройство автоматической подстройки частоты фазоманипулированного сигнала, содержащее многоканальный коррелятор, опорный многофазный генератор. формирователь сигнала, дешифратор, основной и дополнительный блоки памяти, различитель направления набега фазы и формирователь управляющего сигнала [1].

Однако известное устройство обладает недостаточно высокой помехоустойчивостью.

Наиболее близким техническим решением к предлагаемому является устройство слежения за частотой шумоподобных сигналов, содержащее частотный дискриминатор, включающий квадратурные каналы, каждый из которых содержит последовательно соединенные входной перемножитель, интегратор, элемент задержки и канальный перемножитель, причем другой вход канального перемножителя каждого канала подключен к выходу интегратора другого канала, а выходы каналов объединены через вычитатель, к выходу которого подключен петлевой фильтр [2].

Недостаток устройства - низкая помехоустойчивость приема сигналов при скорости передачи дискретной информации, близкой или равной частоте повторения шумоподобного сигнала.

Предлагаемое изобретение призвано решить задачу повышения помехоустойчивости приема шумоподобных сигналов с минимальной частотной манипуляцией при скорости передачи дискретной информации, равной частоте повторения шумоподобного сигнала.

Поставленная задача решается тем, что в устройство слежения за частотой шумоподобных сигналов, содержащее частотный дискриминатор, включающий квадратурные каналы, каждый из которых содержит последовательно соединенные входной перемножитель, интегратор, элемент задержки и канальный перемножитель, причем другой вход канального перемножителя каждого канала подключен к выходу интегратора другого канала, а выходы каналов объединены через вычитатель, к выходу которого подключен петлевой фильтр, введены аналого-цифровой преобразователь, вход которого является входом устройства, преобразователь Гильберта, подключенный к выходу аналого-цифрового преобразователя и объединенным сигнальным входам первого и второго входных перемножителей, третий и четвертый входные перемножители, сигнальные входы которых объединены и подключены к выходу преобразователя Гильберта, а другие входы соединены соответственно с опорными входами первого и второго входных перемножителей, первый сумматор и первый вычитатель, входы которых подключены к выходам первого и четвертого, второго и третьего входных перемножителей соответственно, первый, второй, третий, четвертый канальные перемножители, второй сумматор, второй вычитатель, седьмой и восьмой канальные перемножители, последовательно соединенные третий сумматор, решающий блок и выходной перемножитель, другой вход которого подключен к выходу третьего вычитателя, а выход соединен со входом петлевого фильтра, блок формирования опорных сигналов, вход которого подключен к выходу петлевого фильтра, дополнительные входы соединены соответственно с выходами первого сумматора и первого вычитателя, выходы соединены соответственно с попарно объединенными опорными входами первого и третьего, второго и четвертого входных перемножителей, а дополнительные выходы подключены соответственно к попарно объединенным опорным входам первого и четвертого, второго и третьего канальных перемножителей и синхронизирующим входам первого и второго интеграторов, при этом входы первого и третьего, второго и четвертого канальных перемножителей попарно объединены и подключены к выходам первого сумматора и первого вычитателя соответственно, а выходы первого и второго, третьего и четвертого канальных перемножителей объединены соответственно через второй сумматор и второй вычитатель, выходы которых соединены со входами первого и второго интеграторов соответственно, первые входы седьмого и восьмого канальных перемножителей подключены соответственно к выходам первого и второго интеграторов, другие входы соединены с выходами первого и второго элементов задержки соответственно, а выходы седьмого и восьмого канальных перемножителей объединены через третий сумматор, причем блок формирования опорных сигналов содержит первый цифровой синтезатор отсчетов, вход которого подключен к выходу петлевого фильтра, а выходы являются выходами блока формирования опорных сигналов, и блок кодовой синхронизации, входы и выходы которого являются дополнительными входами и выходами блока формирования опорных сигналов, содержащий первый и второй каналы временного дискриминатора, каждый из которых включает первый, второй, третий и четвертый перемножители, последовательно соединенные четвертый сумматор, третий интегратор, пятый перемножитель и соответственно четвертый вычитатель, четвертый интегратор, шестой перемножитель, при этом входы первого и третьего, второго и четвертого перемножителей каждого канала подключены соответственно к выходам первого сумматора и первого вычитателя, а выходы первого и второго, третьего и четвертого перемножителей каждого канала объединены соответственно через четвертый сумматор и четвертый вычитатель, входы пятого перемножителя и входы шестого перемножителя каждого канала объединены, их выходы подключены к пятому сумматору, а выходы пятого сумматора обоих каналов объединены через пятый вычитатель, последовательно соединенный со вторым петлевым фильтром и блоком формирования квадратурных сигналов, который содержит последовательно соединенные управляемый тактовый генератор, генератор псевдослучайной последовательности и дешифратор, причем к выходу управляемого тактового генератора подключен делитель частоты на четыре, выход которого соединен со входом второго цифрового синтезатора отсчетов, другой вход которого подключен к дополнительному выходу генератора псевдослучайной последовательности, выходы второго цифрового синтезатора отсчетов подключены соответственно к попарно объединенным опорным входам первого и четвертого, второго и третьего перемножителей первого и второго каналов, дополнительные его выходы, являющиеся выходами блока кодовой синхронизации, соединены соответственно с опорными входами канальных перемножителей квадратурного преобразователя, а выход дешифратора, являющийся дополнительным выходом блока кодовой синхронизации, соединен с синхронизирующими входами третьего и четвертого интеграторов обоих каналов, а также первого и второго интеграторов частотного дискриминатора.

Введение перечисленных узлов с описанными связями позволяет по сравнению с прототипом повысить помехоустойчивость и точность слежения за частотой шумоподобных сигналов с минимальной частотной манипуляцией.

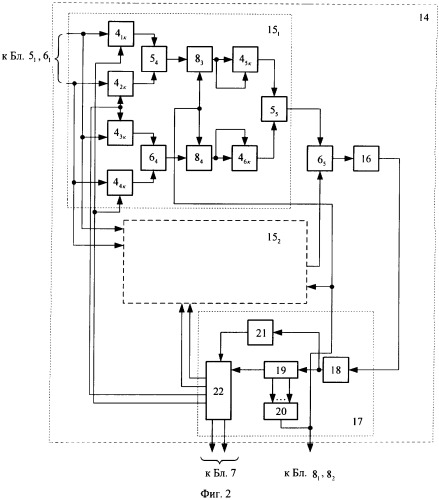

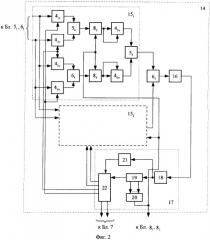

На фиг.1 изображена функциональная схема предлагаемого устройства слежения за частотой шумоподобных сигналов, на фиг.2 - функциональная схема блока кодовой синхронизации.

Устройство слежения за частотой шумоподобных сигналов содержит аналого-цифровой преобразователь 1, вход которого является входом устройства, частотный дискриминатор 2, включающий преобразователь 3 Гильберта, подключенный к выходу аналого-цифрового преобразователя 1, первый, второй, третий и четвертый входные перемножители 41, 42, 43, 44, первый сумматор 51 и первый вычитатель 61, квадратурный преобразователь 7, первый, второй, третий и четвертый канальные перемножители 4′1, 4′2, 4′3, и 4′4, второй сумматор 52 и второй вычитатель 62, первый и второй интеграторы 81 и 82, первый и второй элементы 91 и 92 задержки, пятый, шестой, седьмой и восьмой канальные перемножители 4′5, 4′6, 4′7 и 4′8, третий сумматор 53, третий вычитатель 63, решающий блок 10, выходной перемножитель 45, а также петлевой фильтр 11 и блок 12 формирования опорных сигналов, содержащий первый цифровой синтезатор 13 отсчетов и блок 14 кодовой синхронизации. При этом сигнальные входы первого и второго, третьего и четвертого входных перемножителей 41 и 42, 43 и 44 объединены и подключены соответственно ко входу и выходу преобразователя 3 Гильберта, другие входы первого и третьего, второго и четвертого входных перемножителей 41 и 43, 42 и 44 соединены соответственно с выходами первого цифрового синтезатора 13 отсчетов, являющимися выходами блока 12 формирования опорных сигналов. Выходы первого и четвертого, второго и третьего входных перемножителей 41 и 44, 42 и 43 объединены соответственно через первый сумматор 51 и первый вычитатель 61, выходы которых соединены соответственно с попарно объединенными входами первого и третьего, второго и четвертого канальных перемножителей 4′1 и 4′3, 4′2 и 4′4 квадратурного преобразователя 7, а также со входами блока 14 кодовой синхронизации, являющимися дополнительными входами блока 12 формирования опорных сигналов. Другие входы первого и четвертого, второго и третьего канальных перемножителей 4′1 и 4′4, 4′2 и 4′3 попарно объединены и подключены соответственно к выходам блока 14 кодовой синхронизации, являющимся дополнительными выходами блока 12 формирования опорных сигналов, третий дополнительный выход которого соединен с синхронизирующими входами первого и второго интеграторов 81 и 82, а выходы первого и второго, третьего и четвертого канальных перемножителей 4′1 и 4′2, 4′3 и 4′4 объединены соответственно через второй сумматор 52 и второй вычитатель 62. К выходу второго сумматора 52 подключены последовательно соединенные первый интегратор 81, первый элемент 91 задержки, пятый канальный перемножитель 4′5, а к выходу второго вычитателя 62 - последовательно соединенные второй интегратор 82, второй элемент 92 задержки, шестой канальный перемножитель 4′6. Другие входы пятого и шестого канальных перемножителей 4′7 и 4′8 подключены соответственно к выходам второго и первого интеграторов 81 и 82, а выходы объединены через третий вычитатель 63. Входы седьмого и восьмого канальных перемножителей 4′7 и 4′8 соединены соответственно с выходами первого и второго интеграторов 81 и 82, другие входы подключены соответственно к выходам первого и второго элементов 91 и 92 задержки. Выходы седьмого и восьмого канальных перемножителей 4′7 и 4′8 объединены через третий сумматор 53, который последовательно соединен с решающим блоком 10 и выходным перемножителем 45. Другой вход выходного перемножителя 45 подключен к выходу третьего вычитателя 63, а выход - к последовательно соединенным петлевому фильтру 11 и первому цифровому синтезатору 13 отсчетов, вход которого является входом блока 12 формирования опорных сигналов.

Блок 14 кодовой синхронизации содержит первый и второй каналы 151 и 152 временного дискриминатора, каждый из которых включает первый, второй, третий и четвертый перемножители 41к, 42к, 43к и 44к, последовательно соединенные четвертый сумматор 54, третий интегратор 83, пятый перемножитель 45к и соответственно четвертый вычитатель 64, четвертый интегратор 84, шестой перемножитель 46к. При этом сигнальные входы первого и третьего, второго и четвертого перемножителей 41к и 43к, 42к и 44к каждого из каналов 151 и 152 подключены соответственно к выходам первого сумматора 51 и первого вычитателя 61 частотного дискриминатора 2. Выходы первого и второго, третьего и четвертого перемножителей 41к и 42к, 43к и 44к, каждого из каналов 151 и 152 объединены соответственно через четвертый сумматор 54 и четвертый вычитатель 64. Входы каждого из перемножителей 45к и 46к первого и второго каналов 151 и 152 объединены, а выходы подключены к пятому сумматору 55, выход которого является выходом канала. Выходы обоих каналов объединены через пятый вычитатель 65, последовательно соединенный со вторым петлевьм фильтром 16 и блоком 17 формирования квадратурных сигналов. Последний содержит последовательно соединенные управляемый тактовый генератор 18, генератор 19 псевдослучайной последовательности и дешифратор 20, причем к выходу управляемого тактовою генератора 18 подключен делитель 21 частоты на четыре, выход которого соединен со входом второго цифрового синтезатора 22 отсчетов. Другой вход последнего подключен к дополнительному выходу генератора 19 псевдослучайной последовательности, выходы второго цифрового синтезатора 22 отсчетов подключены соответственно к попарно объединенным опорным входам первого и четвертого, второго и третьего перемножителей 41к и 44к, 42к и 43к первого и второго каналов 151 и 215, а дополнительные выходы, являющиеся выходами блока 14 кодовой синхронизации, соединены соответственно с опорными входами канальных перемножителей 4′1, 4′2, 4′3, 4′4 квадратурного преобразователя 7. Выход дешифратора 20, являющийся дополнительным выходом блока 14 кодовой синхронизации, соединен с синхронизирующими входами третьего и четвертого интеграторов 83 и 84 обоих каналов 151 и 152, а также первого и второго интеграторов 81 и 82 частотного дискриминатора 2.

Устройство слежения за частотой шумоподобных сигналов (ШПС) работает следующим образом.

Входной шумоподобный сигнал, преобразованный в аналого-цифровом преобразователе 1, поступает на входные перемножители 41, 42, 43, 44 частотного дискриминатора 2: на входы перемножителей 41 и 42 непосредственно, а на входы перемножителей 43 и 44 - через преобразователь 3 Гильберта. На другие входы перемножителей 41 и 43, 42 и 44 соответственно поступают отсчеты опорных гармонических ортогональных сигналов частоты ω0, равной средней частоте шумоподобного сигнала, которые вырабатываются цифровым синтезатором 13 отсчетов блока 12 формирования опорных сигналов. Квадратурные составляющие комплексной огибающей шумоподобного сигнала образуются путем объединения соответственно в сумматоре 51 и вычитателе 61 результатов перемножения отсчетов самого сигнала и его преобразования по Гильберту с отсчетами опорных сигналов частоты ω0. При этом составляющие удвоенной частоты ω0, благодаря применению преобразователя 3 Гильберта, полностью подавляются.

Отсчеты квадратурных компонентов комплексной огибающей сигнала с выходов сумматора 51 и вычитателя 61 соответственно поступают на входы перемножителей 4′1, 4′2 и 4′3, 4′4 квадратурного преобразователя 7, где перемножаются с отсчетами опорных квадратурных сигналов, формируемых блоком 14 кодовой синхронизации. При идеальной кодовой синхронизации опорные квадратурные сигналы являются точными копиями квадратурных компонентов комплексной огибающей принимаемого шумоподобного сигнала. Результаты перемножения сигналов в синфазных каналах квадратурного преобразователя 7 объединяются в сумматоре 52 и вычитателе 62, образуя соответственно «косинусную» и «синусную» квадратурные составляющие. Интеграторы 81 и 82 в квадратурных каналах частотного дискриминатора 2 осуществляют когерентное накопление на интервале, равном периоду ТП повторения ШПС, поступающих на их входы отсчетов квадратурных составляющих, формируя отсчеты сжатого по спектру сигнала. Сброс интеграторов 81 и 82 осуществляется с шагом TП синхроимпульсами, вырабатываемыми блоком 14 кодовой синхронизации.

Результаты интегрирования в квадратурных каналах поступают соответственно в элементы 91 и 92 задержки, где задерживаются на ТП. В канальных перемножителях 4′5 и 4′6 отсчеты задержанного сигнала соответственно первого и второго квадратурных каналов перемножаются с отсчетами незадержанного сигнала другого канала. Сигнал ошибки, пропорциональный частотному рассогласованию, формируется на выходе вычитателя 63 путем сравнения выходных сигналов перемножителей 4′5 и 4′6 квадратурных каналов частотного дискриминатора. Для снятия фазовой манипуляции, обусловленной передачей цифровой информации, используется схема, состоящая из канальных перемножителей 4′7 и 4′8, сумматора 53, решающего блока 10 и выходного перемножителя 45. При любом сочетании информационных символов на двух смежных периодах повторения шумоподобного сигнала знаки отсчетов выходных сигналов вычитателя 63 и решающего блока 10 с характеристикой sign(x) совпадают, благодаря чему исключается влияние цифровой модуляции ШПС на формирование сигнала ошибки. Выходной сигнал петлевого фильтра 11, сглаживающего флуктуации сигнала ошибки, используется для управления частотой цифрового синтезатора 13 отсчетов опорных сигналов несущей частоты.

Блок 14 кодовой синхронизации работает следующим образом. Сигналы с выходов сумматора 51 и вычитателя 61 частотного дискриминатора 2 поступают на перемножители 41к, 43к, и 42к, 44к двух каналов 151 и 152 временного дискриминатора. На опорные входы перемножителей 41к, 42к и 43к, 44к подаются отсчеты опорных квадратурных сигналов, формируемые цифровым синтезатором 22 отсчетов. При этом на перемножители 41к и 44к, 42к и 43к первого канала 151 подаются соответственно отсчеты опорных квадратурных сигналов, опережающих на половину длительности Т элемента ШПС, а на перемножители второго канала 152 - отсчеты опорных квадратурных сигналов, задержанных на Т/2 относительно синхронных опорных квадратурных сигналов, используемых в квадратурном преобразователе 7 частотного дискриминатора 2. В каждом канале 151 и 152 сигналы с выходов перемножителей 41к и 42к, 43к и 44к попарно объединяются в сумматоре 54 и вычитателе 64, образуя соответственно «косинусную» и «синусную» квадратурные составляющие, которые поступают далее на интеграторы 83 и 84, осуществляющие когерентное накопление отсчетов квадратурных составляющих на интервале ТП. С помощью перемножителей 45к и 46к результаты интегрирования в квадратурных каналах возводятся в квадрат и объединяются в сумматоре 55. Сигнал ошибки, пропорциональный временному рассогласованию комплексных огибающих принятого и опорного ШПС, формируется путем сравнения выходных сигналов каналов 151 и 152 в вычитателе 65. Петлевой фильтр 16 сглаживает флуктуации сигнала ошибки, формируя управляющий сигнал для управляемого тактового генератора 18 блока 17 формирования квадратурных сигналов. Меандровый сигнал тактовой частоты fТ=1/T, вырабатываемый управляемым тактовым генератором 18, поступает на вход генератора 19 псевдослучайной последовательности, а также на вход делителя 21 частоты на четыре, который формирует сигнал частоты fT/4, подаваемый на вход цифрового синтезатора 22 отсчетов. На другой вход цифрового синтезатора 22 отсчетов поступает ПСП, формируемая генератором 19 псевдослучайной последовательности, которая определяет знак приращения фазы π/2 на интервале, равном длительности T элемента ПСП.

С выходов цифрового синтезатора 22 отсчетов опорные квадратурные сигналы поступают на перемножители 41к, 42к, 43к, 44к каждого канала 151 и 152 временного дискриминатора, а также на перемножители 4′1, 4′2, 4′3, 4′4 квадратурного преобразователя 7 частотного дискриминатора 2. Дешифратор 20, подключенный к генератору 19 псевдослучайной последовательности, формирует синхронизирующий сигнал частоты FП=1/ТП для интеграторов 81, 82 и 83, 84 соответственно частотного дискриминатора и каждого канала 151 и 152 временного дискриминатора.

Пример реализации цифрового синтезатора отсчетов квадратурных сигналов с использованием накапливающего сумматора (аккумулятора фазы) и постоянного запоминающего устройства для хранения отсчетов квадратурных сигналов приведен в [3].

Предлагаемое устройство позволяет повысить помехоустойчивость и точность слежения за частотой шумоподобных сигналов с минимальной частотной манипуляцией.

Источники информации

1. Патент РФ №2089047 С1 от 1997.08.27.

2. Радиотехнические системы / Ю.П.Гришин, В.П.Ипатов, Ю.М.Казаринов и др.; Под ред. Ю.М.Казаринова. - М.: Высш. шк., 1990. - С.318 (рис.14.12).

3. Цифровые системы фазовой синхронизации / М.И.Жодзишский, С.Ю.Сила-Новицкий, В.А.Прасолов и др.; Под. Ред. М.И.Жодзишского. - М.: Сов. радио, 1980. - С.55-57.

Устройство слежения за частотой шумоподобных сигналов, содержащее частотный дискриминатор, включающий квадратурные каналы, каждый из которых содержит последовательно соединенные входной перемножитель, интегратор, элемент задержки и канальный перемножитель, причем другой вход канального перемножителя каждого канала подключен к выходу интегратора другого канала, а выходы каналов объединены через вычитатель, к выходу которого подключен петлевой фильтр, отличающееся тем, что в него введены аналого-цифровой преобразователь, вход которого является входом устройства, преобразователь Гильберта, подключенный к выходу аналого-цифрового преобразователя и объединенным сигнальным входам первого и второго входных перемножителей, третий и четвертый входные перемножители, сигнальные входы которых объединены и подключены к выходу преобразователя Гильберта, а другие входы соединены соответственно с опорными входами первого и второго входных перемножителей, первый сумматор и первый вычитатель, входы которых подключены к выходам первого и четвертого, второго и третьего входных перемножителей соответственно, первый, второй, третий, четвертый канальные перемножители, второй сумматор, второй вычитатель, седьмой и восьмой канальные перемножители, последовательно соединенные третий сумматор, решающий блок и выходной перемножитель, другой вход которого подключен к выходу третьего вычитателя, а выход соединен со входом петлевого фильтра, блок формирования опорных сигналов, вход которого подключен к выходу петлевого фильтра, дополнительные входы соединены соответственно с выходами первого сумматора и первого вычитателя, выходы соединены соответственно с попарно объединенными опорными входами первого и третьего, второго и четвертого входных перемножителей, а дополнительные выходы подключены соответственно к попарно объединенным опорным входам первого и четвертого, второго и третьего канальных перемножителей и синхронизирующим входам первого и второго интеграторов, при этом входы первого и третьего, второго и четвертого канальных перемножителей попарно объединены и подключены к выходам первого сумматора и первого вычитателя соответственно, а выходы первого и второго, третьего и четвертого канальных перемножителей объединены соответственно через второй сумматор и второй вычитатель, выходы которых соединены со входами первого и второго интеграторов соответственно, первые входы седьмого и восьмого канальных перемножителей подключены соответственно к выходам первого и второго интеграторов, другие входы соединены с выходами первого и второго элементов задержки соответственно, а выходы объединены через третий сумматор, причем блок формирования опорных сигналов содержит первый цифровой синтезатор отсчетов, вход которого подключен к выходу петлевого фильтра, а выходы являются выходами блока формирования опорных сигналов, и блок кодовой синхронизации, входы и выходы которого являются дополнительными входами и выходами блока формирования опорных сигналов, содержащий первый и второй каналы временного дискриминатора, каждый из которых включает первый, второй, третий и четвертый перемножители, последовательно соединенные четвертый сумматор, третий интегратор, пятый перемножитель и соответственно четвертый вычитатель, четвертый интегратор, шестой перемножитель, при этом входы первого и третьего, второго и четвертого перемножителей каждого канала подключены соответственно к выходам первого сумматора и первого вычитателя, а выходы первого и второго, третьего и четвертого перемножителей каждого канала объединены соответственно через четвертый сумматор и четвертый вычитатель, входы пятого перемножителя и входы шестого перемножителя каждого канала объединены, их выходы подключены к пятому сумматору, а выходы пятого сумматора обоих каналов объединены через пятый вычитатель, последовательно соединенный со вторым петлевым фильтром и блоком формирования квадратурных сигналов, который содержит последовательно соединенные управляемый тактовый генератор, генератор псевдослучайной последовательности и дешифратор, причем к выходу управляемого тактового генератора подключен делитель частоты на четыре, выход которого соединен со входом второго цифрового синтезатора отсчетов, другой вход которого подключен к дополнительному выходу генератора псевдослучайной последовательности, выходы второго цифрового синтезатора отсчетов подключены соответственно к попарно объединенным опорным входам первого и четвертого, второго и третьего перемножителей первого и второго каналов, дополнительные его выходы, являющиеся выходами блока кодовой синхронизации, соединены соответственно с опорными входами канальных перемножителей квадратурного преобразователя, а выход дешифратора, являющийся дополнительным выходом блока кодовой синхронизации, соединен с синхронизирующими входами третьего и четвертого интеграторов обоих каналов, а также первого и второго интеграторов частотного дискриминатора.