Патент ссср 232603

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 232603

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сова Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 13.XI.1967 (№ 1195927/26-24) Кл. 42m, 5/00

21а1, 36 18 с присоединением заявки ¹

Приоритет

МПЕ G 06f

Н 03k

УД1 681.326.34;621.316..37:621.318.57 (088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Опубликовано 11.XII.1968. Бюллетень № 1 за 1969 г.

Дата опубликования описания 31.III.1969

Авторы изобретения

И. И. Мешечкин и Г. В. Никулин

Заявитель

РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ АСИНХРОННЫХ ПРОЦЕССОВ

Известны распределители импульсов асинхронных процессов, содержащие входные триггеры, генератор синхронизации и собирательные схемы.

Предлагаемое устройство отличается от известных тем, что в нем входы триггера синхронизации соединены с выходами приемных триггеров через входные вентили, управляющие входы которых соединены со схемой сравнения через схему задержки и собирательную схему, а выходы триггера синхронизации через выходные вентили, вторые входы которых соединены с выходами соответствующих приемных триггеров, подключены к формирователям, выходы которых соединены с выходными шинами, входами установки в исходное состояние соответствующих приемных триггеров и входами собирательной схемы.

Это позволяет повысить быстродействие системы.

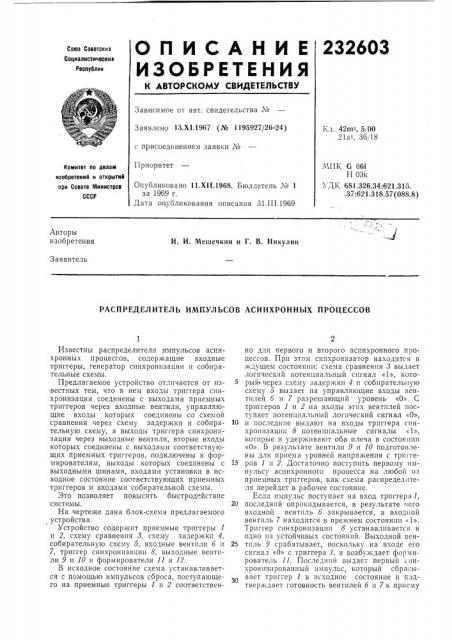

На чертеже дана блок-схема предлагаемого устройства.

Устройство содержит приемные триггеры 1 и 2, схему сравнения 8, схему задержки 4, собирательную схему б, входные вентили 6 и

7, триггер синхронизации 8, выходные вентили 9 и 10 и формирователи 11 и 12.

В исходное состояние схема устанавливается с помощью импульсов сброса, поступающего на приемные триггеры 1 и 2 соответственно для первого и второго асинхронного процессов. При этом синхронизатор находится в ждущем состоянии: схема сравнения 8 выдает логический потенциальный сигнал «1», кото5 рый через схему задержки 4 и собирательную схему 5 выдает на управляющие входы вентилей 6 и 7 разрешающий уровень «О». С триггеров 1 и 2 на входы этих вентилей поступает потенциальный логический сигнал «О», 10 и последние выдают на входы триггера синхронизации 8 потенциальные сигналы «1», которые и удерживают оба плеча в состоянии

«О». В результате вентили 9 и 10 подготовлены для приема уровней напряжения с тригге15 ров 1 и 2. Достаточно поступить первому импульсу асинхронного процесса на любой пз приемных триггеров, как схема распределителя перейдет в рабочее состояние.

Если импульс поступает на вход триггера 1, 20 последний опрокидывается, в результате его входной вентиль 6 закрывается, а входной вентиль 7 находится в прежнем состоянии «1».

Триггер синхронизации 8 устанавливается в одно из устойчивых состояний. Выходной вен25 тиль 9 срабатывает, поскольку на входе его сигнал «0» с триггера 1, и возбуждает формирователь 11. Последний выдает первый с инхронизпрованный импульс, который сбрасывает триггер 1 в исходное состояние и подтверждает готовность вентилей 6 и 7 к приему

232603

Составитель А. Ходырев

Редактор Л. А. Утехина Техред Л. Я. Левина Корректор О. Б. Тюрина

Заказ 433/5 Тираж 530 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Тип огр афин, и р. С а пупов а, 2 сигнала триггера 2 (если в паузу из него поступил импульс второго асинхронного процесса), поскольку сигнал «равенство — неравенство» поступает на эти вентили с задержкой.

В этом случае (если в паузу поступил такой сигнал), вентиль 7 будет закрытым, а вентиль б открытым в течение времени действия импульса. Триггер 8 устанавливается в обратное положение. Открывается выходной вентиль

10, и формирователь 12 выдает на выход первый синхронизированный импульс второго асинхронного процесса, который возвращает триггер 2 в исходное состояние и подтверждает вновь готовность вентилей б и 7. Длительность выходных импульсов определяется в основном задержкой формирователей 11 и 12.

В том случае, если импульсы двух асинхронных процессов совпадают во времени, так что одновременно закрываются вентили б и 7, триггер 8 самостоятельно устанавливается в одно из двух устойчивых состояний, отдавая этим спонтанно предпочтение одному из процессов. Далее схема работает аналогично.

Схема распределителя обеспечивает задержку выходного импульса относительно входного в каждом из своих плеч не более, чем на длительность формируемых в обратном плече выходных импульсов. Этим обеспечивается максимально возможное быстродействие распределителя и устройства, в которое он входит.

Предмет изобретения

Распределитель импульсов асинхронных процессов, содержащий приемные триггеры, синхронизатор, состоящий из схем сравнения и задержки, собирательной схемы, входных и выходных вентилей и триггера синхронизации, и формирователи, отличающийся тем, что, с целью увеличения быстродействия устройства, в нем входы триггера синхронизации соединены с выходами приемных триггеров через входные вентили, управляющие входы которых соединены со схемой сравнения через схему задержки и собирательную схему, а выходы триггера синхронизации через выходные вентили, вторые входы которых соединены с выходами соответствующих приемных триггеров, подключены к формирователям, выходы которых соединены с выходными шинами, со входами установки в исходное состояние соответствующих приемных триггеров и со входами собирательной схемы.