Способ коррекции погрешностей аналого-цифрового преобразования и устройство для его осуществления

Иллюстрации

Показать всеИзобретение относится к измерительной технике, в частности к способам коррекции погрешностей аналого-цифрового преобразования (АЦП) для использования в информационно-измерительных системах. Техническим результатом является снижение сложности реализации при одновременном повышении точности и быстродействия. Способ коррекции погрешностей АЦП заключается в использовании тестирования и коррекции, причем с момента включения корректируемого n-разрядного АЦП (7) осуществляется его непрерывное тестирование в течение 2n тактов путем подачи на его вход тестового сигнала, сформированного высокоточным n-разрядным ЦАП (5), с последующим запоминанием (в оперативном запоминающем устройстве) (ОЗУ) (8) кода разности выходного кода АЦП (7) и кода номера такта по адресу выходного кода корректируемого n-разрядного АЦП (7). По завершении непрерывного тестирования осуществляются чередующиеся в течение одного такта процессы периодического тестирования и коррекции погрешностей АЦП (7), при этом в режиме коррекции выходной код АЦП (7) служит одновременно уменьшаемым кодом и адресом вычитаемого кода (в (n+1)-разрядном сумматоре) (9) - кода, записанного ранее в ОЗУ (8) в ходе режима тестирования, несущего информацию об отклонении реальной характеристики преобразования АЦП (7) от идеальной. Устройство также содержит генератор тактовых импульсов (1), n-разрядный двоичный счетчик (2), (n+1)-входовый элемент И (3), 2х(n+1)-входовый инвертирующий цифровой коммутатор (4), коммутатор аналоговых сигналов (6), элемент ИЛИ (10), делитель на два (11). 2 н.п. ф-лы, 6 ил.

Реферат

Область техники, к которой относится изобретение

Изобретение относится к измерительной технике, в частности к способам коррекции погрешностей аналого-цифрового преобразования и устройствам для их осуществления, и может быть использовано в информационно-измерительных системах.

Уровень техники

Известен способ коррекции погрешностей аналого-цифрового преобразования включающий аналого-цифровое (прямое) преобразование исходного сигнала, цифро-аналоговое (обратное) преобразование сигнала, уменьшенного на величину образцового сигнала прямого преобразования исходного сигнала; полученный сигнал подвергают прямому преобразованию, осуществляют также обратное преобразование сигнала, увеличенного на величину образцового сигнала результата прямого преобразования исходного сигнала, полученный сигнал также подвергают прямому преобразованию, вычисляют скорректированный результат преобразования исходного сигнала по формуле

где К - величина образцового сигнала;

Y1 - результат аналого-цифрового преобразования исходного сигнала;

Y2 - результат аналого-цифрового преобразования значения цифроаналогового преобразования величины (Y1-К);

Y3 - результат аналого-цифрового преобразования значения цифроаналогового преобразования величины (Y1+К).

Для реализации данного способа использовано измерительно-вычислительное устройство, содержащее управляющий вычислительный комплекс (УВК), магистраль типа "общая шина", точный цифроаналоговый преобразователь, источник измеряемого сигнала, входной коммутатор аналоговых сигналов, групповой нормирующий преобразователь с нелинейной функцией преобразования, аналого-цифровой преобразователь (Авторское свидетельство СССР №984030 от 23.12.1982 г.).

Недостатком данного способа и устройства его реализации является высокая сложность, низкая точность и низкое быстродействие, а кроме того, при определенных характеристиках преобразователя, когда существенное значение имеет нелинейность, алгоритм коррекции оказывается нереализуемым.

Наиболее близким к предлагаемому изобретению и взятый авторами за прототип, является способ коррекции погрешностей аналого-цифрового преобразования, заключающийся в формировании кодового сигнала, пропорционального входному аналоговому сигналу с последующим его запоминанием, осуществлении n циклов коррекции, в первом из которых формируют первый эталонный кодовый сигнал, в качестве которого используется запомненный кодовый сигнал с последующим цифроаналоговым и аналого-цифровым его преобразованием с запоминанием результата, после чего формируют второй эталонный кодовый сигнал путем добавления образцового кодового сигнала к первому эталонному кодовому сигналу с последующим цифроаналоговым и аналого-цифровым его преобразованием с запоминанием результата, вычисляют скорректированный код входного аналогового сигнала по кодовым сигналам, пропорциональным входному и двум эталонным сигналом, запоминают его и сравнивают с запомненным кодовым сигналом, пропорциональным входному сигналу, если полученная разность не превышает наперед заданную величину, то формируют выходной кодовый сигнал, равный скорректированному кодовому сигналу, в противном случае осуществляют следующие циклы коррекции, в которых в качестве первого эталонного кодового сигнала используют запомненный в предыдущем цикле коррекции скорректированный кодовый сигнал; вычисление скорректированного кодового сигнала осуществляют по формуле (2)

X'(i-1).ск=X(i-1).ск+Ki, причем:

для i=2, ..., n;

где К - величина образцового сигнала;

Хнск - не скорректированный код входного сигнала;

Xi.ск - скорректированный код входного сигнала;

- результат цифрового измерения входного сигнала;

Yi, Y'i - результаты аналого-цифрового преобразования первого и второго эталонных сигналов.

Для реализации данного способа использовано измерительно-вычислительное устройство (комплекс), содержащее магистраль, цифроаналоговый преобразователь, коммутатор, аналого-цифровой преобразователь, вычислитель (Патент РФ №2085033 от 20.07.1997 г.).

Недостатком данного способа и устройства его реализации является высокая сложность, низкая точность и низкое быстродействие.

Раскрытие изобретения

Технический результат, который может быть достигнут с помощью предлагаемого изобретения, сводится к снижению сложности реализации при одновременном повышении точности и быстродействия.

Технический результат достигается тем, что в способ коррекции погрешностей аналого-цифрового преобразования, включающий коррекцию на основе последовательного цифроаналогового и аналого-цифрового преобразования сигналов, с последующим сохранением результата аналого-цифрового преобразования в оперативном запоминающем устройстве, введен процесс тестирования, который в начале осуществляется в непрерывном режиме с момента включения аналого-цифрового преобразователя в течение 2n тактов, с последующим запоминанием кода разности выходного кода аналого-цифрового преобразователя и кода номера такта по адресу выходного кода корректируемого n-разрядного аналого-цифрового преобразователя, на вход которого подается тестовый сигнал, представляющий собой ступенчатую функцию напряжения, уровень мгновенного значения которого пропорционален коду числа тактовых импульсов, и в случае линеаризации за полный период тестирования (2n тактов) будет совпадать с идеализированной характеристикой аналого-цифрового преобразования, при этом в ходе непрерывного тестирования режим коррекции блокируется, а по завершении непрерывного тестирования начинается этап коррекции погрешностей аналого-цифрового преобразования, причем режимы коррекции и периодического тестирования в течение одного такта чередуются, а периодическое тестирование проводится ввиду возможной нестабильности характеристики преобразования аналого-цифрового преобразователя, при этом в режиме коррекции выходной код аналого-цифрового преобразователя служит одновременно уменьшаемым кодом и адресом вычитаемого кода - кода, записанного ранее в оперативное запоминающее устройство в ходе режима тестирования, несущего информацию об отклонении искаженной (реальной) характеристики преобразования аналого-цифрового преобразователя от идеальной; результат вычислений представляет собой код значения напряжения, лежащего на идеализированной характеристике аналого-цифрового преобразования.

В устройство для осуществления способа коррекции погрешностей аналого-цифрового преобразования, содержащее коммутатор аналоговых сигналов, первый информационный вход которого служит входом устройства, а выход подключен ко входу корректируемого n-разрядного аналого-цифрового преобразователя, выходы которого являются адресными входами оперативного запоминающего устройства (2n слова × n разряда), введены генератор тактовых импульсов, n-разрядный двоичный счетчик, (n+1)-входовый элемент И, 2×(n+1)-входовый инвертирующий цифровой коммутатор, n-разрядный цифроаналоговый преобразователь, (n+1)-разрядный сумматор, двухвходовый элемент ИЛИ, делитель на два, причем выход генератора тактовых импульсов подключен к входу n-разрядного двоичного счетчика, выходы которого одновременно подключены к n входам (n+1)-входового элемента И, к n входам первой группы 2×(n+1)-входового инвертирующего цифрового коммутатора и входам n-разрядного цифроаналогового преобразователя, выход которого подключен к второму информационному входу коммутатора аналоговых сигналов; выходы корректируемого n-разрядного аналого-цифрового преобразователя подключены к n входам второй группы входов (n+1)-разрядного сумматора, на (n+1)-й вход второй группы входов которого (являющегося знаковым разрядом) подан уровень логического нуля; n выходов (n+1)-разрядного сумматора являются выходами устройства, кроме того, выходы с первого по k-й и (n+1)-й (знаковый) одновременно подключены к (k+1)-н входам оперативного запоминающего устройства, соответствующие выходы которого соединены с подобными входами второй группы входов 2×(n+1)-входового инвертирующего цифрового коммутатора, у которого на входы второй группы входов, с (k+1)-го по n-й и (n+1)-й вход первой группы входов подан уровень логического нуля, а (n+1)-й вход второй группы входов, являющийся входом управления, одновременно соединен с выходом двухвходового элемента ИЛИ, входом управления коммутатора аналоговых сигналов, выходом устройства Uзапр., запрещающим снятие информации, поступающей с выхода устройства; выходы инвертирующего цифрового коммутатора соединены со входами первой группы входов (n+1)-разрядного сумматора, на младший разряд переноса которого подан уровень логической единицы; выход (n+1)-входового элемента И подключен к входу делителя на два, инверсный выход которого одновременно соединен с (n+1)-м входом (n+1)-входового элемента И и со вторым входом двухвходового элемента ИЛИ, первый вход которого подключен к выходу генератора тактовых импульсов.

2×(n+1)-входовый инвертирующий цифровой коммутатор содержит инвертор, (n+1)-н инвертирующие коммутационные модули, в каждый из которых входят по два двухвходовых элемента И, двухвходовый элемент ИЛИ-НЕ, причем вход управления инвертирующего цифрового коммутатора подключен ко вторым входам первого двухвходового элемента И непосредственно, а второго двухвходового элемента И через инвертор; первые входы обоих двухвходовых элементов И являются входами, соответственно, первой и второй групп входов инвертирующего цифрового коммутатора, при этом номера входов инвертирующего цифрового коммутатора соответствуют номерам инвертирующих коммутационных модулей; выходы двухвходовых элементов И являются входами двухвходовых элементов ИЛИ-НЕ, выходы которых являются выходами инвертирующих коммутационных модулей и соответствующими выходами инвертирующего цифрового коммутатора, при этом номера выходов инвертирующего цифрового коммутатора соответствуют номерам инвертирующих коммутационных модулей.

Сущность способа коррекции погрешностей аналого-цифрового преобразования заключается в использовании процессов тестирования и коррекции, причем с момента включения корректируемого n-разрядного аналого-цифрового преобразователя осуществляется его непрерывное тестирование в течение 2n тактов путем подачи на его вход тестового сигнала, сформированного высокоточным n-разрядным цифроаналоговым преобразователем (ЦАП), с последующим запоминанием кода разности выходного кода аналого-цифрового преобразователя и кода номера такта по адресу выходного кода корректируемого n-разрядного аналого-цифрового преобразователя; по завершении непрерывного тестирования осуществляются чередующиеся в течение одного такта, процессы периодического тестирования и коррекции погрешностей аналого-цифрового преобразования, при этом в режиме коррекции выходной код аналого-цифрового преобразователя служит одновременно уменьшаемым кодом и адресом вычитаемого кода - кода, записанного ранее в оперативное запоминающее устройство в ходе режима тестирования, несущего информацию об отклонении искаженной (реальной) характеристики преобразования аналого-цифрового преобразователя от идеальной; результат вычислений представляет собой код значения напряжения, лежащего на идеализированной характеристике аналого-цифрового преобразования.

Краткое описание чертежей

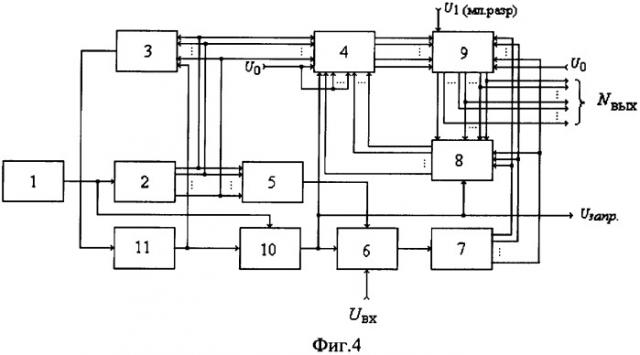

На фиг.1 приведены линейная безыскаженная и выпуклая аддетивно-мультипликативная (искаженная) характеристики преобразования АЦП.

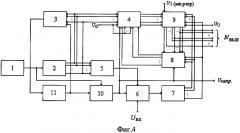

На фиг.2 приведены линейная безыскаженная и вогнутая аддетивно-мультипликативная (искаженная) характеристики преобразования АЦП.

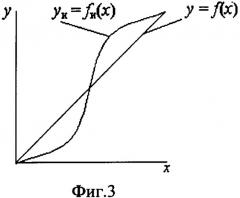

На фиг.3 приведены линейная безыскаженная и выпукло-вогнутая аддетивно-мультипликативная (искаженная) характеристики преобразования АЦП.

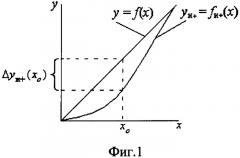

На фиг.4 приведена структурная схема устройства реализации способа коррекции погрешностей аналого-цифрового преобразования.

На фиг.5 приведена структурная схема инвертирующего цифрового коммутатора.

На фиг.6 приведены временные диаграммы работы устройства реализации способа коррекции погрешностей аналого-цифрового преобразования.

Осуществление изобретения

В основе предлагаемого способа коррекции погрешностей аналого-цифрового преобразования лежат следующие концепции.

Процесс аналого-цифрового преобразования может быть охарактеризован двумя основными типами характеристик преобразования:

- линейной безыскаженной, фиг.1, 2, 3, функция y=f(x);

- аддитивно-мультипликативной (искаженной), фиг.1, 2, 3, функциями yи=fи(x)

Данные характеристики преобразования АЦП описываются выражениями:

y=x

yи=а+b·х+с·х2+...+h·xg,

где а, b, с, h - весовые коэффициенты, на которые, как правило, накладываются условия:

В общем случае, искаженные характеристики преобразования АЦП yи принимают вид выпуклых yи+, вогнутых yи- или попеременно выпукло-вогнутых yи± кривых, фиг.1, 2, 3. Погрешность преобразования, при этом, будет определяться соотношениями:

,

где x0 - значение напряжения входного сигнала в момент дискретизации (амплитуда напряжения дискретного значения преобразуемого сигнала);

или в общем виде:

Δyи(x0)=f(x0)-fи(x0).

Несмотря на то, что х, являясь, по сути, аналоговой величиной, характеризуется бесконечным числом возможных значений, x0, как дискретная величина, принимает лишь 2n значений, где n - разрядность АЦП. В силу этого предыдущее выражение можно представить в матричном виде:

или

или

где i∈[1, ..., 2n].

Так как функция y=x служит описанием линейной безыскаженной характеристики преобразования АЦП, матрица безыскаженных значений ||f(xi)|| будет детерминированной. В свою очередь, матрица подлежащих коррекции значений АЦП ||fи(xi)|| и матрица отклонений ||Δyи(xi)|| могут быть детерминированными лишь апостериорно. При этом монотонность характеристик преобразования, фиг.1 и 2, обеспечивает соответствие:

Причем данное соответствие, в реальных АЦП, как правило, однозначное.

С учетом выполнения равенства y=x и требования равенства уровней напряжения шагов квантования у АЦП и ЦАП одной разрядности, предыдущее соотношение можно представить в виде:

Указанную взаимосвязь, присущую конкретному АЦП, можно выявить проведя его тестирование во всем диапазоне входных сигналов. А именно, подавая на вход АЦП тестовый сигнал заданного уровня хт.i и выполняя расчеты отклонения Δyи(xтi) согласно (3), с использованием выходного сигнала АЦП fи(xт.i). Тем самым, множество значений {Δyи(xт.i)} отклонения искаженной (реальной) характеристики преобразования АЦП от безыскаженной (идеальной) приобретает детерминированный характер.

При поступлении на вход АЦП преобразуемого сигнала Xc.j, имеющего статус случайного, выходной кодовый сигнал fи(xс.j) сопоставляется с множеством тестовых значений отклонения характеристики преобразования АЦП {Δyи(хТ.i)} и при выполнении условия:

fи(xc.j)∈[1, ..., 2n].

принимается решение о соответствии

Таким образом, предлагаемый способ коррекции погрешностей аналого-цифрового преобразования заключается в следующем.

На первом этапе, с момента включения, корректируемый n-разрядный АЦП в течение 2n тактов подвергается непрерывному тестированию, суть которого заключается в подаче на вход АЦП сигнала, сформированного высокоточным n-разрядным ЦАП. При этом уровень напряжения сигнала пропорционален номеру такта (фиг.6. а, д). Выходной код АЦП служит адресом ячеек памяти оперативного запоминающего устройства (ОЗУ), в которые записывается код разности номера такта и выходного кода АЦП.

К моменту поступления 2n-ного такта в ОЗУ формируется матрица (3) детерминированных значений отклонения аддитивно-мультипликативной (искаженной, то есть реальной) характеристики преобразования АЦП от безыскаженной (идеальной). Роль коэффициентов матрицы апостериорных значений аддитивно-мультипликативной (искаженной) характеристики преобразования АЦП играет перечень возможных выходных кодов АЦП.

По завершении этапа непрерывного тестирования (фиг.6. е; tнепр.тест) АЦП переходит в режим коррекции погрешностей. На этом этапе периодическое тестирование АЦП осуществляется во второй (активной) половине тактов (фиг.6. е; tпер.тест). Периодическое тестирование проводится в силу возможной нестабильности параметров работающего АЦП. В течение первой (пассивной) половины тактов осуществляется анализ и последующая коррекция отсчетов информационного входного сигнала (фиг.6. е; tкор). По поступлении на вход АЦП преобразуемого сигнала ОЗУ переводится в режим считывания информации из ячеек, адрес которых соответствует выходному коду АЦП. Считанный код вычитается из выходного кода АЦП (4). Сформированный код будет соответствовать режиму безыскаженного аналого-цифрового преобразования.

Структурная схема устройства реализации способа коррекции погрешностей аналого-цифрового преобразования приведена на фиг.4.

Устройство реализации способа коррекции погрешностей аналого-цифрового преобразования содержит генератор тактовых импульсов (ГТИ) 1, n-разрядный двоичный счетчик 2, (n+1)-входовый элемент И 3, 2×(n+1)-входовый инвертирующий цифровой коммутатор (ИЦК) 4, n-разрядный цифроаналоговый преобразователь (ЦАП) 5, коммутатор 6 аналоговых сигналов, корректируемый n-разрядный АЦП 7, ОЗУ 8 (2n слова × (k+1) разряда), (n+1)-разрядный сумматор 9, двухвходовый элемент ИЛИ 10, делитель на два 11, причем выход ГТИ 1 подключен к входу n-разрядного двоичного счетчика 2, выходы которого одновременно подключены к n входам (n+1)-входового элемента И 3, к n входам первой группы 2×(n+1)-входового ИЦК 4 и входам n-разрядного ЦАП 5, выход которого подключен к второму информационному входу коммутатора 6 аналоговых сигналов, первый информационный вход которого служит входом устройства, а выход подключен к входу корректируемого n-разрядного АЦП 7, выходы которого подключены одновременно к шине адресов ОЗУ 8 и к n входам второй группы входов (n+1)-разрядного сумматора 9, на (n+1)-й вход второй группы входов которого (являющегося знаковым разрядом) подан уровень логического нуля; n выходов (n+1)-разрядного сумматора 9, являются выходами устройства, кроме того, выходы с первого по k-й и (n+1)-й (знаковый) одновременно подключены к (k+1)-н входам ОЗУ 8, соответствующие выходы которого соединены с подобными входами второй группы входов 2×(n+1)-входового ИЦК 4, у которого на входы второй группы входов с (k+1)-го по n-й и (n+1)-й вход первой группы входов подан уровень логического нуля, а (n+1)-й вход второй группы входов, являющийся входом управления, одновременно соединен с выходом двухвходового элемента ИЛИ 10, входом управления коммутатора 6 аналоговых сигналов, выходом устройства Uразр., разрешающим снятие информации, поступающей с выхода устройства; выходы ИЦК 4 соединены со входами первой группы входов (n+1)-разрядного сумматора 9, на младший разряд переноса которого подан уровень логической единицы; выход (n+1)-входового элемента И 3 подключен к входу делителя 11 на два, инверсный выход которого одновременно соединен с (n+1)-м входом (n+1)-входового элемента И 3 и со вторым входом двухвходового элемента ИЛИ 10, первый вход которого подключен к выходу ГТИ 1.

2×(n+1)-входовый инвертирующий цифровой коммутатор 4 содержит инвертор 12, (n+1)-н инвертирующие коммутационные модули 13, в каждый из которых входят два двухвходовых элемента И 14 и 15, двухвходовый элемент ИЛИ-НЕ 16, причем вход управления ИЦК 4 подключен ко вторым входам двухвходовых элементов И 14 непосредственно, а И 15 через инвертор 12; первые входы двухвходовых элементов И 14 и И 15 являются входами, соответственно, первой и второй групп входов ИЦК 4, при этом номера входов ИЦК 4 соответствуют номерам инвертирующих коммутационных модулей 13; выходы двухвходовых элементов И 14 и И 15 являются входами двухвходовых элементов ИЛИ-НЕ 16, выходы которых являются выходами инвертирующих коммутационных модулей 13 и соответствующими выходами ИЦК 4, при этом номера выходов ИЦК 4 соответствуют номерам инвертирующих коммутационных модулей 13.

Инвертирующий цифровой коммутатор 4 работает следующим образом.

При поступлении сигнала управления с низким уровнем напряжения на вход Uуправл. на вторые входы двухвходовых элементов И 14 подается уровень логической нуля. На вторые входы двухвходовых элементов И 15 подается уровень логической единицы, сформированный инвертором 12. Элементы И 14 запираются, элементы И 15 открываются. Коммутация сигналов первой группы входов ИЦК 4 запрещается. Коммутация сигналов второй группы входов ИЦК 4 производится с одновременной инверсией состояний посредством элементов ИЛИ-НЕ 16.

При поступлении сигнала управления с высоким уровнем напряжения на вход Uуправл. на вторые входы двухвходовых элементов И 14 подается уровень логической единицы. На вторые входы двухвходовых элементов И 15 подается уровень логического нуля, сформированный инвертором 12. Элементы И 14 открываются, элементы И 15 запираются. Коммутация сигналов второй группы входов ИЦК 4 запрещается. Коммутация сигналов первой группы входов ИЦК 4 производится с одновременной инверсией состояний посредством элементов ИЛИ-НЕ 16.

Диаграммы, поясняющие принцип работы устройства реализации способа коррекции погрешностей аналого-цифрового преобразования, приведены на фиг.6, в частности диаграммы выходных сигналов:

а) - ГТИ1;

б) - прямого выхода триггера младшего разряда n-разрядного двоичного счетчика 2;

в) - n-входового элемента И 3;

г) - инверсного выхода делителя 11 на два;

д) - n-разрядного ЦАП 5;

е) - двухвходового элемента ИЛИ 10.

Устройство реализации способа коррекции погрешностей аналого-цифрового преобразования работает следующим образом.

Работа устройства проходит в два этапа - этап тестирования и этап коррекции.

Этап непрерывного тестирования начинается в момент включения устройства и продолжается в течение первых 2n тактов ГТИ 1 (фиг 6. а, е). Перепадом питания делитель на два 11 устанавливается в нулевое состояние. Высокий уровень потенциала, с инверсного выхода делителя на два 11 (фиг 6. г), поступает на второй вход двухвходового элемента ИЛИ 10, в результате чего на его выходе также устанавливается уровень высокого потенциала (фиг 6. е), который не будет зависить от уровня логического потенциала на первом входе двухвходового элемента ИЛИ 10 (выходных сигналов ГТИ 1). Уровень высокого потенциала с выхода двухвходового элемента ИЛИ 10 обеспечивает:

- коммутацию посредством коммутатора 6 аналоговых сигналов напряжения с выхода ЦАП 5 на вход АЦП 7;

- перевод ОЗУ 8 в режим записи;

- коммутацию выходного кода n-разрядного двоичного счетчика 2 и кода знакового разряда, с последующей их инверсией, на первую группу входов сумматора 9;

- формирование сигнала, запрещающего считывание информации с выходов устройства (уровень высокого потенциала на выходе Uзапр.).

Выходной код n-разрядного двоичного счетчика 2 несет информацию о номере такта, одновременно являясь коэффициентом матрицы безыскаженных значений ||f(xi)|| (3).

С учетом введения напряжения с уровнем логической единицы на вход переноса младшего разряда сумматора 9 и инверсии, осуществляемой ИЦК 4, выходной код n-разрядного двоичного счетчика 2 преобразуется в дополнительный код отрицательного числа (второе слагаемое в выражении (3)).

Уровень напряжения сигнала на выходе ЦАП 5 пропорционален номеру такта (коду n-разрядного двоичного счетчика 2), (фиг 5. д).

Выходной код АЦП 7 одновременно поступает на вторые входы сумматора 9 и служит адресом ячеек памяти ОЗУ 8, в которые записывается выходной код сумматора 9, представляющий собой коэффициенты матрицы отклонений ||Δyи(xi)|| (3).

ОЗУ 8 (2n слова × (k+1) разряда) характеризуется тем, что k<n, причем величина k определяется предельной погрешностью корректируемого АЦП. Например, в случае 16 разрядного АЦП с максимальной погрешностью 1% абсолютная погрешность, выраженная:

- в уровнях квантования, составит:

δ=216/100=655 уровней

- в числе разрядов, составит:

512=29<nδ<210=1024.

С учетом пикового характера погрешностей правомерно принимать k=9. (k+1)-й разряд - знаковый, тогда (k+1)=10. Общий объем памяти ОЗУ составит:

2n·(k+1)=216·10=655360 бит.

К моменту поступления 2n-ного такта в ОЗУ 8 формируется код матрицы (3) детерминированных значений отклонения аддитивно-мультипликативной (искаженной) характеристики преобразования АЦП от безыскаженной (идеальной). При этом коэффициенты матрицы отклонений будут жестко взаимосвязаны с аддитивно-мультипликативной (искаженной) характеристикой преобразования АЦП 7 (выходными кодами АЦП 7).

В момент поступления на вход n-разрядного двоичного счетчика 2 (2n-1)-го импульса с выхода ГТИ 1 на всех выходах счетчика 2, а значит и на выходе (n+1)-входового элемента И 3, устанавливается уровень логической единицы (фиг 6.в). По поступлению на вход n-разрядного двоичного счетчика 2 2n-ного импульса:

- n-разрядный двоичный счетчик 2 обнуляется;

- на выходе (n+1)-входового элемента И 3 устанавливается уровень логического нуля, (фиг 6.в);

- на инверсном выходе делителя на два 11 устанавливается уровень логического нуля (фиг 6.г), (данное состояние остается неизменным вплоть до выключения питания устройства);

- на втором входе двухвходового элемента ИЛИ 10 устанавливается уровень логического нуля (фиг 6.е);

- этап непрерывного тестирования завершается (фиг.6.е; tнепр.тест), начинается этап коррекции.

Этап коррекции.

При наступлении активной части такта (импульса, поступающего с выхода ГТИ 1 (фиг.6.а) алгоритм работы устройства аналогичен алгоритму этапа непрерывного тестирования. Периодическое тестирование АЦП 7 необходимо вследствие возможной нестабильности параметров работающего АЦП.

При наступлении пассивной части такта (паузы в поступлении импульсов с выхода ГТИ 1 (фиг.6.а) на выходе двухвходового элемента ИЛИ 10 устанавливается уровень логического нуля (фиг.6.е; tкор), что:

- обеспечивает коммутацию посредством коммутатора 6 аналоговых сигналов напряжения с входа устройства на вход АЦП 7;

- ОЗУ 8 переводится в режим считывания информации из ячеек, адрес которых соответствует выходному коду АЦП 7;

- формирование сигнала, разрешающего считывание информации с выходов устройства (уровень низкого потенциала на выходе Uзапр.).

- коммутацию выходного кода ОЗУ 8, с последующей их инверсией, на первую группу входов сумматора 9.

С учетом введения напряжения с уровнем логической единицы на вход переноса младшего разряда сумматора 9 и инверсии, осуществляемой ИЦК 4, выходной код ОЗУ 8 преобразуется в дополнительный код отрицательного числа (второе слагаемое в выражении (4)).

Выходной код АЦП 7 есть не что иное, как коэффициенты матрицы апостериорных значений аддитивно-мультипликативной (реальной) характеристики преобразования АЦП. Посредством ОЗУ 8 и сумматора 9 обеспечивается сопоставление коэффициентов матриц идеальной и реальной характеристик преобразования АЦП.

То есть, в случае использования устройства, реализующего предлагаемый способ коррекции погрешностей аналого-цифрового преобразования, возможно обеспечить безыскаженное аналого-цифровое преобразование сигналов с минимальным использованием вычислительных ресурсов.

Минимальное использование вычислительных ресурсов существенно выделяет предлагаемый способ и устройство его реализации, по сравнению с прототипом, по целому ряду показателей:

1) сложности реализации - прототип несомненно сложнее, так как для его реализации использован измерительно-вычислительный комплекс (фактически спецпроцессор);

2) степени коррекции погрешностей - прототип обеспечивает меньшую точность АЦП в силу использования операции деления (2), (3), (4) которая, в обязательном порядке, сопровождается погрешностями расчетов, так как делимое и делитель являются дискретными величинами, а значит, наряду со стандартной погрешностью цифровых систем, обусловленной величиной шага квантования (от которой не избавлено и устройство по предлагаемому способу), имеет место дополнительная погрешность - погрешность вычислений;

3) быстродействию - прототип обладает значительно более низким быстродействием уже в силу использования итерационного алгоритма, который предполагает как минимум два цикла аналого-цифровых преобразований, за каждый из которых преобразования должны проводиться трижды (величины Y, Yi, Y'i, (2)), то есть реальное быстродействие прототипа, без учета потерь времени на проведение вычислений, как минимум в три раза меньше, чем у устройства по предлагаемому способу.

В ходе проведения сравнительной оценки прототипа и устройства по предлагаемому способу нельзя не учитывать критерий готовности устройства к использованию (времени выхода устройства на рабочий режим), по которому устройство по предлагаемому способу явно проигрывает. Однако следует учесть, что измерительная техника, к области которой относится изобретение, обязательно предполагает предварительный «прогрев» аппаратуры перед началом измерений, а значит длительность этапа тестирования устройства по предлагаемому способу, составляющая доли секунды (единицы секунд), не окажет практически никакого влияния на коэффициент готовности измерительной техники (информационно-измерительной системы). Справедливость изложенного обусловлена тем, что в коррекции характеристик преобразования нуждаются прежде всего высокоскоростные АЦП. В частности, 12-разрядный последовательно-параллельный АЦП ADC 12281 выполняет до 20 млн. отсчетов в секунду (Волович Г.И. Микросхемы АЦП и ЦАП / Г.И.Волович, В.Б.Ежов. - М.: Издательский дом «Додэка-XXI», 2005. - 432 с.), в силу этого этап непрерывного тестирования согласно выражению

,

где k=2 - количество обращений к АЦП за такт;

Nn=2n=212 - количество тактов за период непрерывного тестирования АЦП;

Nt=2·107 - количество отсчетов в секунду (количество обращений к АЦП за секунду);

составит:

То есть в случае реализации устройства по предлагаемому способу, по отношению к прототипу, будет иметь место:

1) снижение сложности;

2) увеличение точности;

3) повышение быстродействия.

1. Способ коррекции погрешностей аналого-цифрового преобразования, включающий коррекцию на основе последовательного цифроаналогового и аналого-цифрового преобразования сигналов с последующим сохранением результата аналого-цифрового преобразования в оперативном запоминающем устройстве, отличающийся тем, что в него введен процесс тестирования, который в начале осуществляется в непрерывном режиме с момента включения аналого-цифрового преобразователя в течение 2n тактов с последующим запоминанием кода разности выходного кода аналого-цифрового преобразователя и кода номера такта по адресу выходного кода корректируемого n-разрядного аналого-цифрового преобразователя, на вход которого подается тестовый сигнал, представляющий собой ступенчатую функцию напряжения, уровень мгновенного значения которого пропорционален коду числа тактовых импульсов и в случае линеаризации за полный период тестирования (2n тактов) будет совпадать с идеализированной характеристикой аналого-цифрового преобразования, при этом в ходе непрерывного тестирования режим коррекции блокируется, а по завершении непрерывного тестирования начинается этап коррекции погрешностей аналого-цифрового преобразования, причем режимы коррекции и периодического тестирования в течение одного такта чередуются, а периодическое тестирование проводится ввиду возможной нестабильности характеристики преобразования аналого-цифрового преобразователя, при этом в режиме коррекции выходной код аналого-цифрового преобразователя служит одновременно уменьшаемым кодом и адресом вычитаемого кода - кода, записанного ранее в оперативное запоминающее устройство в ходе режима тестирования, несущего информацию об отклонении искаженной реальной характеристики преобразования аналого-цифрового преобразователя от идеальной; результат вычислений представляет собой код значения напряжения, лежащего на идеализированной характеристике аналого-цифрового преобразования.

2. Устройство коррекции погрешностей аналого-цифрового преобразования, содержащее коммутатор аналоговых сигналов, первый информационный вход которого служит входом устройства, а выход подключен ко входу корректируемого n-разрядного аналого-цифрового преобразователя, выходы которого являются адресными входами оперативного запоминающего устройства (2n слова × n разряда), отличающееся тем, что в устройство введены генератор тактовых импульсов, n-разрядный двоичный счетчик, (n+1)-входовый элемент И, 2×(n+1)-входовый инвертирующий цифровой коммутатор, n-разрядный цифроаналоговый преобразователь, (n+1)-разрядный сумматор, двухвходовый элемент ИЛИ, делитель на два, причем выход генератора тактовых импульсов подключен к входу n-разрядного двоичного счетчика, выходы которого одновременно подключены к n входам (n+1)-входового элемента И, к n входам первой группы 2×(n+1)-входового инвертирующего цифрового коммутатора и входам n-разрядного цифроаналогового преобразователя, выход которого подключен к второму информационному входу коммутатора аналоговых сигналов; выходы корректируемого n-разрядного аналого-цифрового преобразователя подключены к n входам второй группы входов (n+1)-разрядного сумматора, на (n+1)-й вход второй группы входов которого, являющегося знаковым разрядом, подан уровень логического нуля; n выходов (n+1)-разрядного сумматора являются выходами устройства, кроме того, выходы с первого по k-й и (n+1)-й (знаковый) одновременно подключены к (n+1)-м входам оперативного запоминающего устройства, соответствующие выходы которого соединены с подобными входами второй группы входов 2×(n+1)-входового инвертирующего цифрового коммутатора, у которого на входы второй группы входов, с (k+1)-го по n-й и (n+1)-й вход первой группы входов подан уровень логического нуля, а (n+1)-й входы второй группы входов, являющийся входом управления, одновременно соединен с выходом двухвходового элемента ИЛИ, входом управления коммутатора аналоговых сигналов, выходом устройства Uзапр., запрещающим снятие информации, поступающей с выхода устройства; выходы инвертирующего цифрового коммутатора соединены со входами первой группы входов (n+1)-разрядного сумматора, на младший разряд переноса которого подан уровень логической единицы; выход (n+1)-входового элемента И подключен к входу делителя на два, инверсный выход которого одновременно соединен с (n+1)-м входом (n+1)-входового элемента И и со вторым входом двухвходового элемента ИЛИ, первый вход которого подключен к выходу генератора тактовых импульсов; а 2×(n+1)-входовый инвертирующий цифровой коммутатор содержит инвертор, (n+1) инвертирующие коммутационные модули, в каждый из которых входят по два двухвходовых элемента И, двухвходовый элемент ИЛИ-НЕ, причем