Обработка управляющей команды аутентификации сообщения для обеспечения безопасности данных

Иллюстрации

Показать всеИзобретение относится к средствам обеспечения архитектуры вычислительной системы. Техническим результатом является расширение функциональных возможностей вычислительных систем с обеспечением новых дополнительных команд или инструкций с возможностью эмуляции другими архитектурами. В заявке описаны способ, система и компьютерный программный продукт для вычисления кода аутентификации данных, хранящихся в памяти вычислительной среды. Посредством команды задается единица памяти, для которой требуется вычислить код аутентификации. В процессе вычислительной операции процессор определяет один из методов шифрования, который подлежит применению при вычислении кода аутентификации. 2 н. и 8 з.п. ф-лы, 15 ил.

Реферат

Изобретение относится к архитектуре вычислительной системы и, в частности, к новым командам, которые расширяют z-архитектуру фирмы IBM и могут эмулироваться другими архитектурами.

До появления настоящего изобретения, начиная с 60-х годов прошлого века, когда были созданы компьютеры, получившие известность под именем системы S/360, и до настоящего времени трудом многих талантливых инженеров компании IBM была создана особая архитектура, которая в силу своей естественной принадлежности к вычислительным системам получила название "мэйнфрейм" (от англ. "mainframe" - мощный универсальный компьютер), и принципы работы которой определяют архитектуру машины, описывая реализуемые в мэйнфрейме команды, которые были изобретены в компании IBM и которые с учетом их признанного за прошедшие годы значительного вклада в усовершенствование вычислительных машин, представленных мэйнфреймами, были включены в принципы работы систем компании IBM. Первое издание "Принципов работы z-архитектуры" вышло в свет в декабре 2000 г. в виде опубликованного стандартного справочного руководства SA22-7832-00.

Авторами установлено, что развитию данной области техники могут способствовать новые дополнительные команды или инструкции, которые могут быть включены в компьютеры z-архитектуры, а также могут эмулироваться другими разработчиками в более простых машинах, о чем сказано ниже.

В настоящем изобретении предлагается способ вычисления кода аутентификации сообщения для данных, хранящихся в памяти вычислительной среды, с помощью процессора, содержащего память, в которой имеется блок параметров для выполнения команд процессора. Предлагаемый в изобретении способ включает задание посредством команды процессора единицы памяти вычислительной среды, содержащей данные, для которых требуется вычислить код аутентификации сообщения, и вычисление посредством этой команды указанного кода аутентификации сообщения, причем указанная команда соотнесена с полем в регистре процессора, определяющим значение кода функции вычисления кода аутентификации сообщения, на основании которого процессор при выполнении указанной команды определяет один из методов шифрования, который подлежит применению для вычисления кода аутентификации, а при наличии в указанном поле дополнительного значения кода функции процессор выполняет операцию запроса, вызывающую сохранение в блоке параметров слова состояния, имеющего множество разрядов, каждый из которых соответствует определенной функции, причем если определенный разряд слова состояния имеет первое двоичное значение, то этот разряд соответствует значению кода функции, соответствующему установленной в процессоре функции, а если определенный разряд слова состояния имеет второе двоичное значение, то этот разряд соответствует значению кода функции, соответствующему не установленной в процессоре функции.

Предлагаемый в изобретении способ позволяет посредством команды вычисления кода аутентификации выполнять операцию сохранения для сохранения в блоке параметров слова состояния, в отличие от известных систем команд процессоров, предоставляющих для этого возможность использования команд загрузки или перемещения.

Особенности предпочтительных вариантов осуществления изобретения станут очевидными для специалиста из приведенного ниже подробного описания изобретения, сопровождаемого чертежами, на которых показано:

на фиг.1 - команда "вычисление кода аутентификации сообщения" (КМАС) в формате команд RRE,

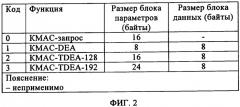

на фиг.2 - таблица, в которой приведены коды функций для команды КМАС, показанной на фиг.1,

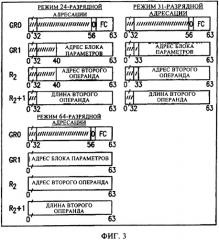

на фиг.3 - присвоение команде КМАС, показанной на фиг.1, значений в регистре общего назначения (GR),

на фиг.4 - символ, обозначающий побитовую операцию "исключающее ИЛИ" (XOR),

на фиг.5 - символ для шифрования и расшифрования по алгоритму шифрования данных (DEA),

на фиг.6 - формат блока параметров для КМАС-запроса,

на фиг.7 - формат блока параметров для KMAC-DEA,

на фиг.8 - операция KMAC-DEA,

на фиг.9 - формат блока параметров для KMAC-TDEA-128,

на фиг.10 - операция KMAC-TDEA-128,

на фиг.11 - формат блока параметров для KMAC-TDEA-192,

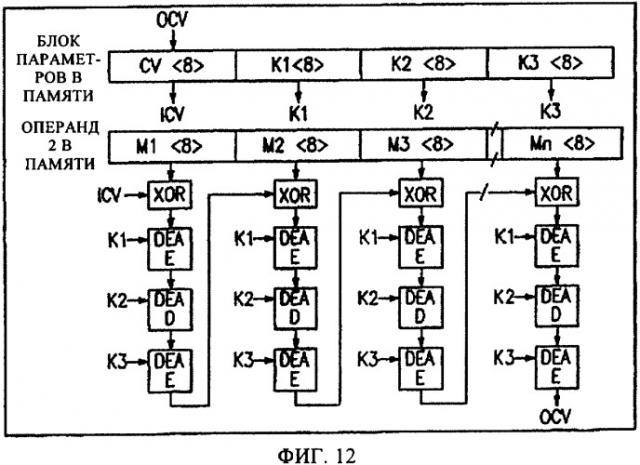

на фиг.12 - операция KMAC-TDEA-192,

на фиг.13 - таблица, в которой показан приоритет выполнения команды КМАС,

на фиг.14 - криптографический сопроцессор, и

на фиг.15 - обобщенный предпочтительный вариант осуществления памяти компьютера, в которой хранятся команды, соответствующие предпочтительному варианту изобретения, и данные, а также механизм выборки, дешифрации и выполнения таких команд либо в вычислительной системе, в которой используются команды этой архитектуры, либо при эмуляции таких команд.

Ниже сначала рассматривается команда "вычисление кода аутентификации сообщения" (КМАС), затем предпочтительная вычислительная система, а в качестве альтернативы - вычислительная система, которая для выполнения таких команд эмулирует другую вычислительную систему.

Команда "вычисление кода аутентификации сообщения" (КМАС)

На фиг.1 представлена команда "вычисление кода аутентификации сообщения" (КМАС) в формате команд RRE.

Выполняется функция, указываемая кодом функции в регистре 0 общего назначения. Разряды 16-23 команды и поле R1 игнорируются.

Разряды 57-63 регистра 0 общего назначения содержат код функции. На фиг.2 показаны присвоенные коды функций. Все другие коды функций свободны (не присвоены). Разряд 56 общего регистра должен быть нулевым, в противном случае определяется исключительная ситуация при нарушении заданных условий. Все остальные разряды регистра 0 общего назначения игнорируются.

Регистр 1 общего назначения содержит логический адрес крайнего левого байта блока параметров, хранящегося в памяти. В режиме 24-разрядной адресации содержимым разрядов 40-63 регистра 1 общего назначения является адрес, а содержимое разрядов 0-39 игнорируется. В режиме 31-разрядной адресации содержимым разрядов 33-63 регистра 1 общего назначения является адрес, а содержимое разрядов 0-32 игнорируется.

В режиме 64-разрядной адресации содержимым разрядов 0-63 регистра 1 общего назначения является адрес.

На фиг.2 показаны коды функций команды "вычисление кода аутентификации сообщения".

Все другие коды функций свободны (не присвоены). Функция запроса является средством указания доступности других функций. Для функции запроса содержимое регистров R2 и R2+1 общего назначения игнорируется.

Для всех остальных функций второй операнд обрабатывают в соответствии с тем, как это задано кодом функции с использованием начального значения цепочки в блоке параметров, и полученным результатом заменяют значение цепочки. При выполнении этой операции также используется криптографический ключ в блоке параметров. Операцию осуществляют до достижения местоположения конца второго операнда или обработки числа байтов, заданного центральным процессором (ЦП), в зависимости от того, что произойдет раньше. Результат указывают в коде условия.

Поле R2 обозначает четно-нечетную пару регистров общего назначения и должно соответствовать регистру с четным номером, в противном случае определяется исключительная ситуация при нарушении заданных условий.

Местоположение крайнего левого байта второго операнда задается содержимым регистра R2 общего назначения. Число байтов в местоположении второго операнда задается в регистре R2+1 общего назначения.

При выполнении операции адрес в регистре R2 общего назначения увеличивается на число обработанных байтов из второго операнда, а его длина в регистре R2+1 общего назначения уменьшается на такое же число байтов. Формирование и обновление адреса и его длины зависит от режима адресации.

В режиме 24-разрядной адресации содержимое разрядов 40-63 регистра R2 общего назначения представляет собой адрес второго операнда и игнорируется; разряды 40-63 обновленного адреса заменяют собой соответствующие разряды в регистре R_ общего назначения, переносы разряда 40 обновленного адреса игнорируются, а содержимое разрядов 32-39 регистра R_ общего назначения устанавливается на нуль. В режиме 31-разрядной адресации содержимым разрядов 33-63 регистра R_ общего назначения является адрес второго операнда, а содержимое разрядов 0-32 игнорируется; разряды 33-63 обновленного адреса заменяют собой соответствующие разряды в регистре R_ общего назначения, переносы разряда 33 обновленного адреса игнорируются, а содержимое разряда 32 регистра R_ общего назначения устанавливается на нуль. В режиме 64-разрядной адресации содержимым разрядов 0-63 регистра R_ общего назначения является адрес второго операнда; разряды 0-63 обновленных адресов заменяют собой содержимое регистра R_ общего назначения, а переносы разряда 0 игнорируются.

В режимах как 24-разрядной, так и 31-разрядной адресации содержимым разрядов 32-63 регистра R2+1 общего назначения является 32-разрядное целое двоичное число без знака, которое задает число байтов во втором операнде, а обновленное значение заменяет собой содержимое разрядов 32-63 регистра R2+1 общего назначения. В режиме 64-разрядной адресации содержимое разрядов 0-63 регистра R2+1 общего назначения образует 64-разрядное целое двоичное число без знака, которое задает число байтов во втором операнде, и обновленное значение заменяет собой содержимое регистра R2+1 общего назначения.

В режимах 24-разрядной и 31-разрядной адресации содержимое разрядов 0-31 регистров R2 и R2+1 общего назначения всегда остается неизменным.

На фиг.3 показано содержимое описанных выше регистров общего назначения.

В режиме адресации с использованием регистров доступа (AR) регистры доступа 1 и R2 задают адресные пространства, содержащие соответственно блок параметров и второй операнд.

Получаемый результат аналогичен результату обработки, начинаемой с левого конца второго операнда и продолжаемой вправо блок за блоком. Операция завершается, когда обработаны все исходные байты во втором операнде (что именуется нормальным завершением) или когда обработано заданное ЦП число блоков, которое меньше длины второго операнда (что именуется частичным завершением). Заданное ЦП число блоков зависит от модели и может быть различным при каждом выполнении команды. Как правило, заданное ЦП число блоков не равно нулю. В некоторых нештатных ситуациях такое число может равняться нулю и может быть установлен код условия 3 без продвижения вперед (зацикливание). Вместе с тем ЦП обеспечивает защиту от бесконечного повторения в таком случае зацикливания.

Если поле значения цепочки перекрывает любую часть второго операнда, результат, полученный в поле значения цепочки, является непредсказуемым.

Нормальное завершение происходит в том случае, когда обработано то число байтов во втором операнде, которое задано в регистре R2+1 общего назначения.

Если операция закончилась ввиду нормального завершения, устанавливается код условия 0, а полученное значение в регистре R2+1 равно нулю. Если операция закончилась ввиду частичного завершения, устанавливается код условия 3, и полученное значение в регистре R2+1 не равно нулю.

Если длина второго операнда изначально равна нулю, доступ ко второму операнду и блоку параметров не осуществляется, регистры R2 и R2+1 общего назначения не меняются и устанавливается код условия 0.

С точки зрения других ЦП и канальных программ ссылки на блок параметров и хранимые в памяти операнды могут являться ссылками с множественным доступом, доступ к таким ячейкам в памяти необязательно должен быть осуществляться одновременно с доступом к блоку параметров, а последовательность таких доступов или ссылок не определена.

О возникновении исключительных ситуаций по доступу (исключениях из доступа) может сообщаться в отношении более крупной части второго операнда, чем часть, обрабатываемая за одну операцию выполнения команды; вместе с тем, исключения из доступа не распознаются в отношении местоположений за пределами длины второго операнда, а также местоположений на расстоянии более 4 Кбайт от текущего обрабатываемого местоположения.

Символы, используемые при описании функций

При дальнейшем описании функций "вычисление кода аутентификации сообщения" используются символы, приведенные на фиг.4 и 5. Для функций, задействующих алгоритм шифрования данных DEA (от англ. "Data Encryption Algorithm"), разряд четности ключа DEA в каждом байте ключа DEA игнорируется, и операция продолжается в нормальном режиме независимо от четности ключа DEA.

Более подробно алгоритм шифрования данных описан в стандарте Data Encryption Algorithm, ANSI-X3.92.1981, American National Standard for Information Systems (Американский национальный стандарт для информационных систем).

КМАС-запрос (код функции 0)

Местоположения операндов и адреса, используемые данной командой, соответствуют показанным на фиг.3. На фиг.6 показан формат блока параметров, используемого для функции КМАС-запроса.

В блоке параметров хранится 128-разрядное слово состояния. Разряды 0-127 данного поля соответствуют кодам функций соответственно 0-127 команды КМАС. Если разряд равен единице, соответствующая функция установлена; в противном случае функция не установлена.

По завершении выполнения функции КМАС-запроса применяется код условия 0; код условия 3 к данной функции неприменим.

KMAC-DEA (код функции 1)

Местоположения операндов и адреса, используемые данной командой, соответствуют показанным на фиг.3.

На фиг.7 показан формат блока параметров, используемого для функции KMAC-DEA.

Код аутентификации сообщения для 8-байтовых блоков сообщения (M1, М2...Mn) в операнде 2 вычисляют с использованием алгоритма DEA при помощи 64-разрядного криптографического ключа и 64-разрядного значения цепочки в блоке параметров.

Код аутентификации сообщения, который также называют выходным значением цепочки (OCV - от англ. "Output Chaining Value"), сохраняют в поле значения цепочки блока параметров. Операция KMAC-DEA показана на фиг.8.

KMAC-TDEA-128 (код функции 2)

Местоположения операндов и адреса, используемые данной командой, соответствуют показанным на фиг.3.

На фиг.9 показан формат блока параметров, используемого для функции KMAC-TDEA-128.

Код аутентификации сообщения для 8-байтовых блоков сообщения (M1, М2...Mn) в операнде 2 вычисляют с использованием алгоритма TDEA при помощи двух 64-разрядных криптографических ключей и 64-разрядного значения цепочки в блоке параметров.

Код аутентификации сообщения, который также называют выходным значением цепочки (OCV), сохраняют в поле значения цепочки блока параметров. Операция KMAC-TDEA-128 показана на фиг.10.

KMAC-TDEA-192 (код функции 3)

Местоположения операндов и адреса, используемые данной командой, соответствуют показанным на фиг.3.

На фиг.11 показан формат блока параметров, используемого для функции KM-TDEA-192.

Код аутентификации сообщения для 8-байтовых блоков сообщения (M1, М2...Mn) в операнде 2 вычисляют с использованием алгоритма TDEA при помощи трех 64-разрядных криптографических ключей и 64-разрядного значения цепочки в блоке параметров.

Код аутентификации сообщения, который также называют выходным значением цепочки (OCV), сохраняют в поле значения цепочки блока параметров. Операция KMAC-TDEA-192 показана на фиг.12.

Особые условия для КМАС

При наличии любого из нижеперечисленных условий определяется исключительная ситуация при нарушении заданных условий и не предпринимаются какие-либо действия:

1. Разряд 56 регистра 0 общего назначения не равен нулю.

2. Для разрядов 57-63 регистра 0 общего назначения не определен или не установлен код функции.

3. Поле R обозначает регистр с нечетным номером или регистр 0 общего назначения.

4. Длина второго операнда не является кратной размеру блока данных указанной функции (для определения размера блоков данных для функций "вычисление кода аутентификации сообщения" см. фиг.7-54 на стр.7-92).

Получаемый код условия:

0 нормальное завершение

1 --

2 --

3 частичное завершение

Программные исключительные ситуации:

• по доступу (выборка, операнд 2 и длина сообщения в битах; выборка и сохранение, значение цепочки);

• при выполнении операции (если не установлена вспомогательная программа засекречивания сообщений);

• при нарушении заданных условий.

Примечания по программированию:

1. Разряд 56 регистра 0 общего назначения зарезервирован для будущего расширения и должен быть установлен на нуль.

2. Если установлен код условия 3, адрес и длину второго операнда в регистрах R2 и R2+1 общего назначения, соответственно, и значение цепочки в блоке параметров обычно обновляют таким образом, что программа может легко вернуться к команде и продолжить выполнение операции. В нештатных ситуациях ЦП защищает от бесконечного повторения операций в случаях зацикливания. Таким образом, когда бы ни был установлен код условия 3, программа может успешно вернуться к команде без зацикливания.

3. Если длина второго операнда изначально не равна нулю и установлен код условия 0, обновление регистров происходит таким же образом, как и при коде условия 3; значение цепочки в данном случае таково, что обработка дополнительных операндов может быть осуществлена таким же образом, как если бы они были частью той же цепочки.

4. Перед обработкой первой части сообщения программа должна задать исходные значения для поля значений цепочки. Согласно стандарту ANSI X9.0 или Х9.19 исходное значение цепочки должно соответствовать нулевому разряду.

Криптографический сопроцессор

В предпочтительном варианте осуществления изобретения предусматривается использование криптографического сопроцессора (сопроцессор криптографической поддержки), который может использоваться в сочетании с описанными выше командами, а также для выполнения шифрованных сообщений и как вспомогательное средство для решения разнообразных задач сцепления сообщений, которые могут использоваться при сцеплении и криптографическом применении в сочетании с соответствующими командами.

На фиг.14 показан криптографический сопроцессор, который непосредственно присоединен к тракту данных, общему для всех внутренних исполнительных устройств на универсальном микропроцессоре, который имеет несколько операционных конвейеров. Внутренняя шина 1 микропроцессора, которая является общей для всех остальных исполнительных устройств, соединена с криптографическим блоком 2 управления, который отслеживает на шине команды процессора, которые он должен выполнять.

Криптографический блок управления служит криптографическим сопроцессором, который непосредственно связан с трактом данных, общим для всех внутренних исполнительных устройств центрального процессора на универсальном микропроцессоре, обеспечивающих доступные аппаратные средства (Е0...Еn) или из их сочетания в предпочтительном варианте с операционными конвейерами. При появлении в регистре 3 команд криптографической команды блок 2 управления вызывает из доступных аппаратных средств соответствующий алгоритм. Данные операнда через входной регистр 4, действующий по принципу обслуживания в порядке поступления (FIFO-регистр), поступают по той же внутренней шине микропроцессора. По завершении операции в регистре 6 состояния ставится флаг, а результаты становятся доступными для чтения с выходного FIFO-регистра 5.

В проиллюстрированном предпочтительном варианте осуществления изобретение рассчитано на возможность наращивания для включения стольких аппаратурных машин, сколько требуется конкретной реализацией в зависимости от задач, которые ставятся перед системой. Пути передачи данных в направлении входного и выходного регистров 7 являются общими для всех машин.

В предпочтительном варианте осуществления изобретения криптографические функции реализованы в аппаратном исполнительном устройстве на ЦП, чем достигается меньшее время ожидания (задержка) при вызове и выполнении операций шифрования и повышается эффективность.

За счет сокращения времени ожидания значительно расширяются возможности универсальных процессоров в системах, где часто выполняется много операций шифрования, в особенности, если при этом речь идет лишь о небольших объемах данных. Это делает возможной реализацию, способную существенно ускорить процессы, связанные с осуществлением защищенных онлайновых транзакций. Наиболее распространенные способы обеспечения безопасности онлайновых транзакций предусматривают применение набора из трех алгоритмов. Первый алгоритм используется один раз за сеанс и может быть реализован аппаратно или программно, а остальные алгоритмы вызываются при каждой транзакции во время сеанса, при этом настоящее изобретение исключает затраты времени, связанные и с задержкой при вызове внешних аппаратных средств, и с выполнением алгоритма программными средствами.

На фиг.15 концептуально показана реализация предпочтительного варианта осуществления изобретения на примере мэйнфрейма с описанным выше микропроцессором, который, как доказано экспериментальным путем в компании IBM, может эффективно использоваться в массовой реализации формата команд предложенной архитектуры для компьютеров с функциональностью длинного смещения, который используют программисты, в наши дни обычно программисты, работающие на языке "Си". Такие форматы команд, которые хранятся в запоминающем устройстве, может реализовать "родной" сервер IBM z-архитектуры или в качестве альтернативы вычислительные машины на базе других архитектур. Их могут эмулировать существующие и будущие серверы IBM класса мэйнфрейм и другие машины IBM (например, серверы серии р и серверы серии х). Их могут выполнять использующие оперативную систему Linux разнообразные компьютеры на базе аппаратных средств IBM, Intel, AMD, Sun Microsystems и других компаний. Помимо выполнения таким аппаратным обеспечением с z-архитектурой Linux также может применяться в машинах, использующих эмуляцию на базе Hercules, UMX, FXI или Platform Solutions, в которых режим выполнения в целом представляет собой режим эмуляции. В режиме эмуляции осуществляют дешифрацию конкретной эмулируемой команды и формируют стандартную подпрограмму для реализации отдельной команды в виде стандартной подпрограммы или драйвера на языке С или создают драйвер для определенного аппаратного обеспечения иным способом, доступным для специалистов в данной области техники, ознакомившихся с описанием предпочтительного варианта осуществления. Различные способы осуществления на целевом компьютере эмуляции формата команд, архитектура которых разработана для исполнения на другом компьютере, а также серийно выпускаемые средства программного обеспечения, используемые в этих целях, описаны в ряде патентов, раскрывающих программные и аппаратные средства эмуляции, включая, без ограничения, патенты US 5551013, US 6009261, US 5574873, US 6308255, US 6463532 и US 5790825.

В данном предпочтительном варианте осуществления изобретения форматы для несуперскалярной команды, предшествующие формату с длинным смещением, образуют адрес хранения операнда путем суммирования базового регистра и 12-разрядного смещения без знака либо базового регистра, индексного регистра и 12-разрядного смещения без знака, а новые форматы команды с длинным смещением образуют адрес хранения операнда путем суммирования базового регистра и 20-разрядного смещения со знаком либо базового регистра, индексного регистра и 20-разрядного смещения со знаком.

Как показано на фиг.15, такие команды выполняются аппаратно процессором или путем эмуляции такого набора команд программным обеспечением, установленным на компьютере с другим "родным" набором команд.

На фиг.15 позицией 501 обозначена память (запоминающее устройство) компьютера, в котором хранятся команды и данные. В таком компьютере изначально хранятся описанные в настоящем изобретении команды с длинным смещением. Позицией 502 обозначен механизм выборки команд из памяти компьютера, который также может предусматривать помещение выбранных команд в местное буферное запоминающее устройство. Затем команды в исходном виде поступают в дешифратор 503 команд, который определяет тип выбранной команды. Позицией 504 обозначен механизм выполнения команд. Он может предусматривать загрузку данных в регистр из памяти 501, сохранение данных из регистра в памяти или выполнение какой-либо арифметической или логической операции. Тип такой выполняемой операции предварительно определен дешифратором команд. В данном случае выполняются описанные в настоящем изобретении команды с длинным смещением. Если команды с длинным смещением выполняются в "родной" вычислительной системе, процесс завершается, как это описано выше. Если же набор команд со структурой, содержащей команды с длинным смещением, эмулирует другой компьютер, описанный процесс будет реализован в хост-компьютере 505 программно. В этом случае упомянутые выше механизмы, как правило, будут реализованы в виде одной или нескольких стандартных системных подпрограмм в рамках эмулирующего программного обеспечения. В обоих случаях происходят вызов, дешифрация (декодирование) и выполнение команды.

В частности, команды этой архитектуры можно использовать с компьютерной архитектурой, в которой применяются существующие форматы команд с 12-разрядным смещением без знака, используемым для формирования адреса хранения операнда, а также с архитектурой, в которой применяются дополнительные форматы команд, обеспечивающие дополнительные разряды смещения, предпочтительно на 20 разрядов, представляющего собой увеличенное смещение со знаком, используемое для формирования адреса хранения операнда. Команды такой архитектуры представляют собой компьютерное программное обеспечение, которое хранится в запоминающем устройстве компьютера и служит для генерации кода, исходящего из процессора, в котором используется компьютерное программное обеспечение, и содержит код команды, используемый компилятором или эмулятором/интерпретатором, хранящимся в запоминающем устройстве 501 компьютера, при этом первая часть кода команды содержит код операции, задающий операцию, которую нужно выполнить, а вторая часть назначает операнды для участия в ее выполнении. При использовании команд с длинным смещением становится возможным напрямую обращаться к дополнительным адресам.

Как показано на фиг.15, такие команды выполняются аппаратно процессором или - путем эмуляции указанного набора команд - программным обеспечением, работающим на компьютере с другим собственным набором команд.

В соответствии с компьютерной архитектурой, используемой в предпочтительном варианте изобретения, поле смещения состоит из двух частей, при этом наименьшая значимая часть состоит из 12 разрядов и обозначается DL, DL1 - для операнда 1 или DL2 - для операнда 2, а наибольшая значимая часть состоит из 8 разрядов и обозначается DH, DH1 - для операнда 1 или DH2 - для операнда 2.

Кроме того, в предпочтительной компьютерной архитектуре формат команды таков, что коду операции соответствуют разряды с 0 по 7 и с 40 по 47, целевому регистру, называемому R1, соответствуют разряды с 8 по 11, индексному регистру, называемому Х2, соответствуют разряды с 12 по 15, базовому регистру, называемому В2, соответствуют разряды с 16 по 19, первой части состоящего из двух частей смещения, которая называется DL2, соответствуют разряды с 20 по 31, а второй части, которая называется DH2, соответствуют разряды с 32 по 39.

Эта компьютерная архитектура имеет такой формат команды, что коду операции соответствуют разряды с 0 по 7 и с 40 по 47, целевому регистру, называемому R1, соответствуют разряды с 8 по 11, исходному регистру, называемому R3, соответствуют разряды с 12 по 15, базовому регистру, называемому В2, соответствуют разряды с 16 по 19, первой части состоящего из двух частей смещения, которая называется DL2, соответствуют разряды с 20 по 31, а второй части, которая называется DH2, соответствуют разряды с 32 по 39.

Кроме того, предложенные для архитектуры компьютера команды с длинным смещением имеют такой формат, что коду операции соответствуют разряды с 0 по 7 и с 40 по 47, целевому регистру, называемому R1, соответствуют разряды с 8 по 11, значению маски, называемому М3, соответствуют разряды с 12 по 15, базовому регистру, называемому В2, соответствуют разряды с 16 по 19, первой части состоящего из двух частей смещения, которая называется DL2, соответствуют разряды с 20 по 31, а второй части, которая называется DH2, соответствуют разряды с 32 по 39.

Как показано выше, предпочтительная архитектура компьютера с длинным смещением имеет такой формат команды, что коду операции соответствуют разряды с 0 по 7 и с 40 по 47, непосредственному значению, называемому I2, соответствуют разряды с 8 по 15, базовому регистру, называемому В2, соответствуют разряды с 16 по 19, первой части состоящего из двух частей смещения, которая называется DL1, соответствуют разряды с 20 по 31, а второй части, которая называется DH1, соответствуют разряды с 32 по 39.

Предложенная в изобретении архитектура компьютера с длинным смещением отличается эффективностью при работе с новыми создаваемыми командами, в которых применен только формат команды с новым 20-разрядным смещением без знака.

В особом варианте осуществления предложенной в изобретении архитектуры компьютера используются существующие команды, форматы которых имеют только 12-разрядное смещение без знака и которые в новых форматах определены как имеющие существующее 12-разрядное значение смещения без знака, если 8 старших разрядов в поле смещения DH являются нулевыми разрядами, или как имеющие 20-разрядное смещение со знаком, если 8 старших разрядов в поле смещения DH не являются нулевыми разрядами.

Еще одной формой осуществления изобретения является устройство для вычисления кода аутентификации сообщения для данных, хранящихся в памяти вычислительной среды, имеющее средства для задания посредством команды единицы памяти, для которой требуется вычислить код аутентификации, и средства вычисления посредством этой команды кода аутентификации для единицы памяти.

1. Способ вычисления кода аутентификации сообщения для данных, хранящихся в памяти вычислительной среды, с помощью процессора, содержащего память, в которой имеет блок параметров для выполнения команд процессора, включающий

задание посредством команды процессора единицы памяти вычислительной среды, содержащей данные, для которых требуется вычислить код аутентификации сообщения, и

вычисление посредством этой команды указанного кода аутентификации сообщения, причем указанная команда соотнесена с полем в регистре процессора, определяющим значение кода функции вычисления кода аутентификации сообщения, на основании которого процессор при выполнении указанной команды определяет один из методов шифрования, который подлежит применению для вычисления кода аутентификации, а при наличии в указанном поле дополнительного значения кода функции процессор выполняет операцию запроса, вызывающую сохранение в блоке параметров указанной единицы пасяти слова состояния, имеющего множество разрядов, каждый из которых соответствует определенной функции, причем если определенный разряд слова состояния имеет первое двоичное значение, то этот разряд соответствует значению кода функции, соответствующему установленной в процессоре функции, а если определенный разряд слова состояния имеет второе двоичное значение, то этот разряд соответствует значению кода функции, соответствующему не установленной в процессоре функции.

2. Способ по п.1, в котором указанная команда при ее выполнении процессором сохраняет вычисленный код аутентификации в первом операнде.

3. Способ по п.1, в котором методы шифрования, соответствующие значениям кода функции, включают в себя криптографическую операцию с 64-разрядным ключом по алгоритму DEA, криптографическую операцию с двумя 64-разрядными ключами по алгоритму Triple DEA и криптографическую операцию с тремя 64-разрядными ключами по алгоритму Triple TDEA.

4. Способ по п.1, в котором для вычисления кода аутентификации создают криптографический ключ, соотнесенный с единицей памяти.

5. Способ по п.1, в котором команда выполняется устройством обработки данных, эмулирующим архитектуру команды, причем архитектура команды отличается от архитектуры устройства обработки данных.

6. Способ по п.1, в котором задают множество единиц памяти и вычисление кода аутентификации сообщения выполняют для этого множества единиц памяти.

7. Способ по п.6, в котором код аутентификации сообщения вычисляют путем формирования цепочки шифрованных блоков сообщения, содержащихся в единицах памяти.

8. Способ по п.1, в котором указанная команда реализована аппаратными и/или программными средствами.

9. Способ по п.1, в котором задание единицы памяти включает в себя предоставление информации о местоположении структуры данных, соотнесенной с указанной единицей памяти.

10. Носитель данных с хранящейся на нем компьютерной программой, содержащей команды, предназначенные для осуществления всех стадий способа по любому из пп.1-9 при выполнении компьютерной программы в вычислительной системе.