Устройство для преобразования аналоговых сигналов в код

Иллюстрации

Показать всеИспользование: в области вычислительной и измерительной техники. Технический результат заключается в повышении точности и расширении функциональных возможностей устройства. Устройство для преобразования аналоговых сигналов в код содержит первый аналого-цифровой преобразователь (АЦП), второй АЦП, ключи, устройство управления, генератор тактовой частоты. В него введены источник прецизионного опорного напряжения, снабженный системой термостатирования, регистр управления, буферный регистр, процессор, постоянное запоминающее устройство с прошивкой программ процессора для управления устройством для преобразования аналоговых сигналов в код, ключи выполнены в виде релейных ключей, каждый первый и второй АЦП выполнены как сигма-дельта аналого-цифровой преобразователь, к контактам ключей подключены вывод нулевого потенциала источника аналогового сигнала и выход источника прецизионного опорного напряжения. 3 ил.

Реферат

Изобретение относится к области вычислительной и измерительной техники, а именно к устройствам для преобразования напряжения постоянного тока в код.

Известно устройство для преобразования аналоговых сигналов в код [1], содержащее два аналого-цифровых преобразователя (АЦП) и устройство управления каждым АЦП.

Наиболее близким по технической сущности является устройство для преобразования аналоговых сигналов в код [2], содержащее первый аналого-цифровой преобразователь (АЦП), второй АЦП, ключи с входами аналоговых сигналов, устройство управления, генератор тактовой частоты.

Недостатком такого устройства для преобразования аналоговых сигналов в код является погрешность преобразования, обусловленная температурным и временным изменениями коэффициента преобразования.

Техническим результатом изобретения является повышение точности устройства для преобразования аналоговых сигналов в код и расширение его функциональных возможностей.

Данный технический результат достигается в устройстве для преобразования аналоговых сигналов в код, содержащем первый аналого-цифровой преобразователь (АЦП), второй АЦП, ключи с входами аналоговых сигналов, устройство управления, генератор тактовой частоты, тем, что в него введены источник прецизионного опорного напряжения, снабженный системой термостатирования, регистр управления, буферный регистр, процессор, постоянное запоминающее устройство (ПЗУ) с прошивкой программ процессора для управления устройством для преобразования аналоговых сигналов в код, первый, второй, третий, четвертый ключи выполнены в виде релейных ключей, каждый первый и второй АЦП выполнен как сигма-дельта аналого-цифровой преобразователь, к размыкающим контактам первого и второго релейных ключей подключен потенциальный вывод источника аналогового сигнала, к размыкающим контактам третьего и четвертого релейных ключей подсоединен вывод нулевого потенциала источника аналогового сигнала, к замыкающим контактам третьего и четвертого релейных ключей подключен выход источника прецизионного опорного напряжения, переключающий контакт третьего релейного ключа подсоединен к замыкающему контакту первого релейного ключа, переключающий контакт четвертого релейного ключа подсоединен к замыкающему контакту второго релейного ключа, переключающий контакт первого релейного ключа подсоединен к входу первого АЦП, к входу второго АЦП подключен переключающий контакт второго релейного ключа, к входам управления первого, второго, третьего и четвертого релейных ключей подключены соответственно первый, второй, третий и четвертый выходы регистра управления, к входам процессора подключены выходы первого и второго АЦП и генератора тактовой частоты, еще один вход процессора предназначен для подключения сигнала цикла от внешнего процессора, один выход процессора соединен шиной с входом регистра управления, другие выходы процессора соединены с входами данных, адреса записи и разрешения записи буферного регистра, тактовые входы первого и второго АЦП соединены с выходами процессора, ПЗУ соединено шиной с процессором, регистр управления и процессор предназначены для выполнения функций устройства управления, для передачи данных внешнему процессору предназначены выход кода и вход адреса чтения буферного регистра.

Посредством введения регистра управления, буферного регистра, процессора, источника прецизионного опорного напряжения, ПЗУ с прошивкой программ процессора, релейных ключей, подключения к контактам релейных ключей вывода нулевого потенциала источника аналоговых сигналов, источника прецизионного опорного напряжения, выполнения АЦП как сигма-дельта аналого-цифровой преобразователь, обеспечивается повышение точности преобразования аналогового сигнала в код за счет компенсации аддитивной и мультипликативной погрешностей преобразования, улучшения соотношения сигнал-шум.

Путем выполнения первого и второго АЦП как сигма-дельта аналого-цифровой преобразователь, введения процессора расширяются функциональные возможности устройства для преобразования аналоговых сигналов в код, так как его выходными сигналами являются интегральная функция входного сигнала и временной интервал, за который эта функция получается. Это упрощает процедуру обмена внешнего процессора с устройством для преобразования аналоговых сигналов в код как с асинхронным устройством и позволяет получать одновременно интегральную функцию входного сигнала и производную от этого интеграла.

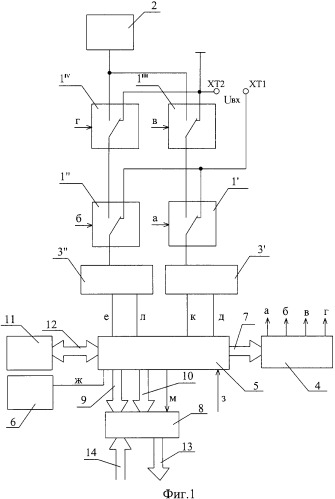

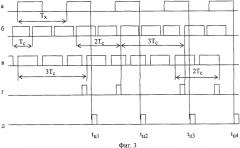

На фиг.1 представлена электрическая схема устройства для преобразования аналоговых сигналов в код, на фиг.2 - циклограммы работы устройства для преобразования аналоговых сигналов в код, на фиг.3 - циклограммы тактовых и управляющих сигналов.

В устройстве для преобразования аналоговых сигналов в код (фиг.1) потенциальный вывод ХТ1 источника аналоговых сигналов подключен к размыкающим контактам первого 1I и второго 1II релейных ключей, к размыкающим контактам третьего 1III и четвертого 1IV релейных ключей подсоединен вывод ХТ2 нулевого потенциала источника аналоговых сигналов. К замыкающим контактам третьего 1III и четвертого 1IV релейных ключей подключен выход источника прецизионного опорного напряжения 2, у которого выполнена система термостатирования. Переключающий контакт третьего релейного ключа 1III подсоединен к замыкающему контакту первого релейного ключа 1I, переключающий контакт четвертого релейного ключа 1IV подсоединен к замыкающему контакту второго релейного ключа 1II. Переключающий контакт первого релейного ключа 1I подсоединен к входу первого АЦП 3I, к переключающему контакту второго релейного ключа 1II подсоединен вход второго АЦП 3II. Первый АЦП 3I и второй АЦП 3II выполнены как сигма-дельта аналого-цифровой преобразователь. К входу управления первого релейного ключа 1I подключен первый выход «а» регистра управления 4. Соответственно к входам управления второго 1II, третьего 1III и четвертого 1IV релейного ключей подсоединены второй «б», третий «в» и четвертый «г» выходы регистра управления 4.

Выход первого АЦП 3I подключен к входу «д» процессора 5, к входу «е» которого подсоединен выход второго АЦП 3II. К входу «ж» процессора 5 подключен выход генератора тактовой частоты 6. Вход «з» процессора 5 предназначен для подключения сигнала внешнего цикла от внешнего процессора.

Выходы «к», «л» процессора 5 подсоединены к тактовым входам первого 3I и второго 3II АЦП. Еще один выход процессора 5 соединен шиной 7 с входом регистра управления 4. Выход «м» процессора 5 подключен к входу разрешения записи буферного регистра 8. Шиной 9 выход процессора 5 соединен с входом данных буферного регистра 8, вход адреса записи которого соединен шиной 10 с выходом процессора 5. ПЗУ 11 соединено шиной 12 с процессором 5. Выход кода по шине 13 и вход адреса чтения по шине 14 буферного регистра 8 предназначены для передачи данных внешнему процессору.

Устройство для преобразования аналоговых сигналов в код работает следующим образом.

Напряжение Uвх на выводах ХТ1, ХТ2 (фиг.1) источника аналоговых сигналов через размыкающий контакт первого релейного ключа 1I подсоединяется к входу первого АЦП 3I и через размыкающий контакт второго релейного ключа 1II - к входу второго АЦП 3II. После преобразования в первом АЦП 3I напряжения Uвх1 в код Nвх1, коррекции кода Nвх1 в процессоре 5, по шине 13 буферного регистра 8 во внешний процессор после запроса внешнего процессора выдается выходной код Nвых1 устройства для преобразования аналоговых сигналов в код.

В момент времени t1 (фиг.2) по сигналу с выхода «а» регистра управления 4 происходит переключение первого релейного ключа 1I, и на вход первого АЦП 3I подается потенциал, существующий на выводе ХТ2 источника аналоговых сигналов. В первом АЦП 3I этот потенциал преобразуется в код N01. С момента времени t1 процессор 5 выдает после коррекции в буферный регистр 8 преобразованное в код Nвх2 во втором АЦП 3II напряжение Uвх2, и по шине 13 буферного регистра 8 во внешний процессор после запроса внешнего процессора выдается выходной код Nвых2 устройства для преобразования аналоговых сигналов в код.

В момент времени t2 по сигналу с выхода «в» регистра управления 4 происходит переключение третьего релейного ключа 1III, и на вход первого АЦП 3I подается напряжение Uоп от источника прецизионного опорного напряжения 2, которое преобразуется в первом АЦП 3I в код Nоп1.

В момент времени t3 по сигналу управления с выхода «а» регистра управления 4 первый релейный ключ 1I возвращается в исходное положение, подключая к входу первого АЦП 3I входное напряжение Uвх1. В это же время по сигналу управления с выхода «в» регистра управления 4 третий релейный ключ 1III возвращается в исходное состояние.

В интервал времени от момента времени t3 до момента времени t4 в процессоре 5 производятся следующие вычисления.

Вычисляется код N'вх1:

Определяется код N'оп1:

Вычисляется коэффициент K1:

где NK - код напряжения источника прецизионного опорного напряжения 2, определенный при предварительной калибровке устройства для преобразования аналоговых сигналов в код.

В процессоре 5 формируется скорректированный код Nвых1:

Этот код выдается в буферный регистр 8 и с выхода буферного регистра 8 по шине 13 выдается во внешний процессор по запросу внешнего процессора.

В момент времени t4 процессор прекращает выдачу кода Nвых2 в буферный регистр 8.

В момент времени t5 по сигналу управления с выхода «б» регистра управления 4 происходит переключение второго релейного ключа 1II, на вход второго АЦП 3II поступает потенциал, существующий на выводе ХТ2 источника аналоговых сигналов, который преобразуется во втором АЦП 3II в код N02.

В момент времени t6 сигналом управления с выхода «г» регистра управления 4 производится переключение четвертого релейного ключа 1IV, на вход второго АЦП 3II подается напряжение Uоп от источника прецизионного опорного напряжения 2, которое преобразуется во втором АЦП 3II в код Nоп2.

В момент времени t7 по сигналу управления с выхода «б» регистра управления 4 второй релейный ключ 1II возвращается в исходное положение, подключая к входу второго АЦП 3II входное напряжение Uвх1. В это же время по сигналу управления с выхода «г» регистра управления 4 четвертый релейный ключ 1IV возвращается в исходное состояние.

В интервал времени от момента времени t7 до момента времени t8 в процессоре 5 производятся следующие вычисления.

Вычисляется код N'вх2:

Определяется код N'оп1:

Вычисляется коэффициент K2:

В процессоре 5 формируется скорректированный код Nвых2:

Этот код выдается в буферный регистр 8 и с выхода буферного регистра 8 по шине 13 выдается во внешний процессор по запросу внешнего процессора. Момент t8 аналогичен моменту t0 циклограммы (фиг.2), с этого момента циклограмма повторяется. Этим обеспечивается непрерывность преобразования входного напряжения от источника аналогового сигнала.

Таким образом во внешний процессор передается код Nвых, который содержит попеременно поступающие коды Nвых1, Nвых2, представляющие преобразованное в первом АЦП 3I и втором АЦП 3II входное напряжение от источника аналоговых сигналов. В кодах Nвых1 и Nвых2 устранена аддитивная погрешность по формулам (1) и (5) соответственно, обусловленная наличием потенциала на выводе нулевого потенциала источника аналоговых сигналов. Кроме того, в кодах Nвых1 и Nвых2 устранена мультипликативная погрешность преобразования, вызванная изменением коэффициента преобразования первого АЦП 3I и второго АЦП 3II с течением времени и в зависимости от температуры окружающей среды.

На вход «з» процессора 5 от внешнего процессора подаются импульсы Тx внешнего цикла (фиг.3, а), которым определяется последовательность выдачи кодов Nвых1, Nвых2. Поступающими на тактовый вход первого АЦП 3I с выхода «к» процессора 5 тактовыми импульсами формируется в первом АЦП 3I последовательность интервалов преобразования длительностью Тс (фиг.3, б). Поступающими на тактовый вход второго АЦП 3II с выхода «л» процессора 5 тактовыми импульсами формируется во втором АЦП 3II последовательность интервалов преобразования длительностью Тс (фиг.3, в), смещенная примерно на половину Тс относительно последовательности в соответствии с фиг.3, б. Длительность интервала преобразования Тс не менее чем в 2 раза меньше минимальной длительности Тx внешнего цикла. При этом за интервал между положительными перепадами импульсов внешнего цикла один из АЦП 3I,3II успевает закончить больше внутренних асинхронных циклов преобразования Тс возможно большей длительности. Погрешность преобразования сигма-дельта АЦП тем меньше, чем больше длительность интегрирования сигнала шума за интервал преобразования Тс.

К отрицательному перепаду импульса внешнего цикла процессор 5 подготавливает сумму полных приращений кода за то количество циклов Тс, которое укладывается между положительными фронтами импульсов внешнего цикла (фиг.3, г), и длительность текущего преобразования с помощью синхроимпульсов генератора тактовой частоты. В моменты времени, когда и в каком из АЦП 3I или 3II подготовлена сумма полных приращений кода Nвых за период nTс (где n=2, 3...), коды или Nвых1, или Nвых2 в моменты времени tц1, tц2, tц3, tц4 и т.д. (фиг.3, д) передаются во внешний процессор с выхода буферного регистра 8 по шине 13 по запросу внешнего процессора. Кроме того, по запросу внешнего процессора по шине 13 может быть передана длительность временного интервала nTc, за который получена данная сумма полных приращений.

Регистр управления 4 и процессор 5 во время работы устройства для преобразования аналоговых сигналов в код выполняют функции устройства управления.

Источники информации

1. Авторское свидетельство СССР №1184090, А кл. Н03М 1/00. Следящий аналого-цифровой преобразователь, 1984 г.

2. Авторское свидетельство СССР №377843, кл. Н03М 1/00. Многоканальный аналого-цифровой преобразователь, 1971 г.

Устройство для преобразования аналоговых сигналов в код, содержащее первый аналого-цифровой преобразователь (АЦП), второй АЦП, ключи с входами аналоговых сигналов, устройство управления, генератор тактовой частоты, отличающееся тем, что в него введены источник прецизионного опорного напряжения, снабженный системой термостатирования, регистр управления, буферный регистр, процессор, постоянное запоминающее устройство (ПЗУ) с прошивкой программ процессора для управления устройством для преобразования аналоговых сигналов в код, первый, второй, третий, четвертый ключи выполнены в виде релейных ключей, каждый первый и второй АЦП выполнен как сигма-дельта аналого-цифровой преобразователь, к размыкающим контактам первого и второго релейных ключей подключен потенциальный вывод источника аналогового сигнала, к размыкающим контактам третьего и четвертого релейных ключей подсоединен вывод нулевого потенциала источника аналогового сигнала, к замыкающим контактам третьего и четвертого релейных ключей подключен выход источника прецизионного опорного напряжения, переключающий контакт третьего релейного ключа подсоединен к замыкающему контакту первого релейного ключа, переключающий контакт четвертого релейного ключа подключен к замыкающему контакту второго релейного ключа, переключающий контакт первого релейного ключа подсоединен к входу первого АЦП, к входу второго АЦП подключен переключающий контакт второго релейного ключа, к входам управления первого, второго, третьего и четвертого релейных ключей подключены соответственно первый, второй, третий и четвертый выходы регистра управления, к входам процессора подключены выходы первого и второго АЦП и генератора тактовой частоты, еще один вход процессора предназначен для подключения сигнала цикла от внешнего процессора, один выход процессора соединен шиной с входом регистра управления, другие выходы процессора соединены с входами данных, адреса записи и разрешения записи буферного регистра, тактовые входы первого и второго АЦП соединены с выходами процессора, ПЗУ соединено шиной с процессором, регистр управления и процессор предназначены для выполнения функций устройства управления, для передачи данных внешнему процессору предназначены выход кода и вход адреса чтения буферного регистра.