Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)). Технический результат заключается в повышении коэффициента усиления по напряжению. Дифференциальный усилитель (ДУ) содержит входной дифференциальный каскад (ДК) (1) с источником опорного тока (ИОТ) (2) в общей эмиттерной цепи, повторитель тока (ПТ) (3), имеющий базовый вход (4), а также эмиттерные входы (5) и (6), которые соединены с токовыми выходами (7) и (8) ДК (1) и через токостабилизирующие резисторы (9) и (10) связаны с шиной (11) источника питания (ИП), первый (12) и второй (13) ИОТ, причем второй ИОТ (13) соединен с выходом (14) ДУ и основным токовым выходом (15) ПТ (3). В схему введен дополнительный транзистор (16), эмиттер которого подключен к первому ИОТ (12), база соединена с выходом (14) ДУ, а коллектор подключен к базовому входу (4) ПТ (3). 2 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах, которые стали основой более чем 20 серийных ОУ, выпускаемых как зарубежными (НА 2520, НА 5190, AD 797, AD 8631, AD 8632, ОР 90 и др.), так и российскими (154УД3 и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ, на их модификации выдано более 100 патентов в различных странах. Предлагаемое изобретение относится к данному подклассу устройств.

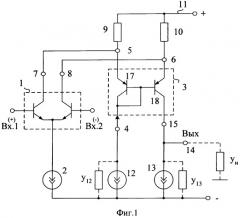

Одной из модификаций «перегнутых» каскадных усилителей является схема фиг.1, представленная в публикациях [1-11]. Она используется в ОУ ряда зарубежных фирм (НА 2539, ОР-90, ОР-42), а также в отечественных микросхемах 140УД30.

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США № 5734296, содержащий входной дифференциальный каскад 1 с источником опорного тока 2 в общей эмиттерной цепи, повторитель тока 3, имеющий базовый вход 4, а также эмиттерные входы 5 и 6, которые соединены с токовыми выходами 7 и 8 входного дифференциального каскада 1 и через токостабилизирующие резисторы 9 и 10 связаны с шиной 11 источника питания, первый 12 и второй 13 источники опорного тока, причем второй источник опорного тока 13 соединен с выходом дифференциального усилителя 14 и основным токовым выходом 15 повторителя тока 3.

Существенный недостаток известного ДУ состоит в том, что он имеет недостаточно высокий предельный коэффициент усиления по напряжению (Ку), который измеряется при сопротивлении нагрузки .

Основная цель предлагаемого изобретения состоит в повышении предельного коэффициента усиления по напряжению Ку.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с источником опорного тока 2 в общей эмиттерной цепи, повторитель тока 3, имеющий базовый вход 4, а также эмиттерные входы 5 и 6, которые соединены с токовыми выходами 7 и 8 входного дифференциального каскада 1 и через токостабилизирующие резисторы 9 и 10 связаны с шиной 11 источника питания, первый 12 и второй 13 источники опорного тока, причем второй источник опорного тока 13 соединен с выходом дифференциального усилителя 14 и основным токовым выходом 15 повторителя тока 3, предусмотрены новые элементы и связи - в схему введен дополнительный транзистор 16, эмиттер которого подключен к первому источнику опорного тока 12, база соединена с выходом дифференциального усилителя 14, а коллектор подключен к базовому входу 4 повторителя тока 3.

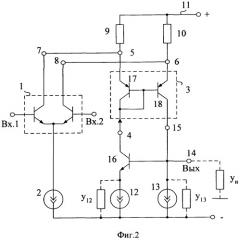

Схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения показана на фиг.2.

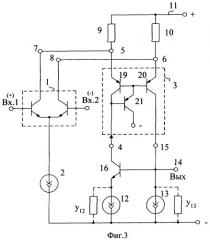

На фиг.3 показан заявляемый ДУ с другим частным вариантом построения повторителя тока 3.

На фиг.4 представлен ДУ, соответствующий п.3 формулы изобретения.

На фиг.5 показана схема известного и заявляемого (при условии соединения базы транзистора VT10 с коллектором транзистора VT4) устройств в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.6 представлены результаты компьютерного расчета коэффициента усиления ДУ фиг.5 в диапазоне частот. При этом выходные проводимости источников опорного тока I5 (12) и I6 (13) моделировались резисторами R7 и R8.

На фиг.7 показана зависимость коэффициента усиления по напряжению схемы фиг.4 и ДУ-прототипа от сопротивления резистора R=R25.

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 с источником опорного тока 2 в общей эмиттерной цепи, повторитель тока 3, имеющий базовый вход 4, а также эмиттерные входы 5 и 6, которые соединены с токовыми выходами 7 и 8 входного дифференциального каскада 1 и через токостабилизирующие резисторы 9 и 10 связаны с шиной 11 источника питания, первый 12 и второй 13 источники опорного тока, причем второй источник опорного тока 13 соединен с выходом дифференциального усилителя 14 и основным токовым выходом 15 повторителя тока 3. В схему введен дополнительный транзистор 16, эмиттер которого подключен к первому источнику опорного тока 12, база соединена с выходом дифференциального усилителя 14, а коллектор подключен к базовому входу 4 повторителя тока 3.

В частном случае на фиг.2 повторитель тока реализован на транзисторах 17 и 18 в соответствии с п.2 формулы изобретения. В схеме фиг.3 этот же повторитель тока выполнен на транзисторах 19, 20 и 21.

На фиг.4 в соответствии с п.3 формулы изобретения в схему введен третий вспомогательный транзистор 22 и вспомогательный резистор 25. Причем база вспомогательного транзистора 22 соединена с источником напряжения смещения 23 (в частном случае - с общей шиной), эмиттер связан со вспомогательным источником опорного тока 24 и через вспомогательный резистор 25 соединен с эмиттером дополнительного транзистора 16.

Рассмотрим работу заявляемого ДУ.

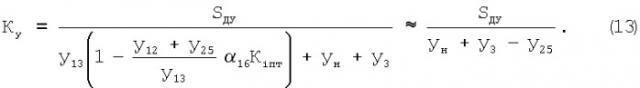

Коэффициент усиления по напряжению ДУ-прототипа фиг.1 существенно зависит от величины эквивалентного сопротивления (проводимости уэ) в цепи нагрузки:

где - крутизна усиления сигнала со входов ДУ в цепь нагрузки в режиме короткого замыкания по выходу.

Проводимость уэ складывается из трех составляющих - выходной проводимости повторителя тока 3 (у3), выходной проводимости источника опорного тока 13 (у13) и проводимости нагрузки ун:

При высокоомной нагрузке (Rн=∞) и типовом построении источника опорного тока 13 на транзисторах с малым напряжением Эрли преобладает составляющая у13. Поэтому предельный коэффициент усиления по напряжению ДУ-прототипа

В заявляемом устройстве фиг.3 обеспечивается взаимная компенсация в узле 14 двух идентичных проводимостей у12 и у13 источников опорного тока 12 и 13. Действительно, изменение выходного напряжения в узле 14 на величину uвых порождает в схеме появление токов

где α16≈1 - коэффициент усиления по току эмиттера транзистора 16.

Приращение iк16 поступает на вход 4 повторителя тока 3 и при идентичных сопротивлениях резисторов 9 и 10 (R9, R10) создает приращение тока iпт3, которое компенсирует приращение i13

где Ki пт≈1 - коэффициент передачи по току повторителя тока 3.

В результате в узле 14 суммарное приращение тока уменьшается

Или после преобразований

Таким образом, эффективное значение выходной проводимости источника опорного тока 13

где Тi=α16Кiпт≈1;

KY=у12/у13 - коэффициент асимметрии выходных проводимостей источников опорного тока 12 и 13.

Так как источники опорного тока 12 и 13 выполняются идентичными, то КY≈1. Поэтому выигрыш по предельному коэффициенту усиления, который реализуется в заявленной схеме, достигает значений NK>>1, где

На практике предельные значения Кy.max в схеме фиг.3 ограничивается величиной

где у3 - выходная проводимость повторителя тока 3.

В схеме фиг.4 предусмотрена дополнительная возможность устанавливать любое заданное значение проводимости у12.экв в эмиттерной цепи транзистора 16

где у25 - проводимость резистора 25, которая может изменяться.

Поэтому в схеме фиг.5 коэффициент усиления по напряжению

Из уравнения (13) следует, что за счет целенаправленного выбора у25 можно получить существенное увеличение предельного коэффициента усиления по напряжению ДУ фиг.4. Данный вывод подтверждается результатами (фиг.7) компьютерного моделирования схемы фиг.4 - выигрыш по Ку.max достигает 70 дБ (более чем в тысячу раз).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № 4600893

2. Операционные усилители и компараторы [Текст]. - М.: Издательский дом «Додэка-XXI», 2001. - С.243-244.

3. Матавкин В.В. Быстродействующие операционные усилители [Текст] / В.В.Матавкин. - М.: Радио и связь, 1989.

4. Патент США № 6456162.

5. Патент США № 6501333.

6. Патент США № 6542030.

7. Патент США № 4293824.

8. Патент США № 5734296.

9. Патент США № 5420540.

10. Патент США № 5523718

11. Патент США № 4644295.

1. Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению, содержащий входной дифференциальный каскад (1) с источником опорного тока (2) в общей эмиттерной цепи, повторитель тока (3), имеющий базовый вход (4), а также эмиттерные входы (5) и (6), которые соединены с токовыми выходами (7) и (8) входного дифференциального каскада (1) и через токостабилизирующие резисторы (9) и (10) связаны с шиной (11) источника питания, первый (12) и второй (13) источники опорного тока, причем второй источник опорного тока (13) соединен с выходом дифференциального усилителя (14) и основным токовым выходом (15) повторителя тока (3), отличающийся тем, что в схему введен дополнительный транзистор (16), эмиттер которого подключен к первому источнику опорного тока (12), база соединена с выходом дифференциального усилителя (14), а коллектор подключен к базовому входу (4) повторителя тока (3).

2. Устройство по п.1, отличающееся тем, что повторитель тока (3) содержит первый (17) и второй (18) вспомогательные транзисторы, эмиттеры которых являются эмиттерными входами (5) и (6) повторителя тока (3), общая точка базы первого (17), базы второго (18) и коллектора первого (17) вспомогательных транзисторов является базовым входом (4) повторителя тока (3), а коллектор второго (18) вспомогательного транзистора соединен с основным выходом (15) повторителя тока (3).

3. Устройство по п.1, отличающееся тем, что в схему введен третий вспомогательный транзистор (22), база которого соединена с источником напряжения смещения (23), эмиттер связан со вспомогательным источником опорного тока (24) и через вспомогательный резистор (25) соединен с эмиттером дополнительного транзистора (16).