Дифференциальный усилитель с малым напряжением смещения нуля

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано для усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Технический результат заключается в уменьшении составляющей напряжения смещения нуля, обусловленной влиянием токовых зеркал (ТЗ). Дифференциальный усилитель (ДУ) содержит комплементарный входной дифференциальный каскад (ДК) (1), имеющий первый (2) и второй (3) противофазные токовые выходы (ТВ), согласованные с шиной положительного источника питания (ИП) (4), третий (5) и четвертый (6) противофазные ТВ, согласованные с шиной отрицательного ИП (7), первое (8), второе (9), третье (10) ТЗ, причем вход первого ТЗ (8) соединен с первым (2) ТВ ДК (1), вход второго ТЗ (9) соединен со вторым ТВ (3) ДК (1), вход третьего ТЗ (10) соединен с четвертым (6) ТВ ДК (1), выход первого ТЗ (8) связан со входом третьего ТЗ (10), а выходы второго (9) и третьего (10) ТЗ соединены с выходом ДУ (11). В схему введено дополнительное ТЗ (12), токовый выход которого соединен со входом третьего ТЗ (10), а вход - подключен к третьему (5) ТВ ДК (1). 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах).

Известны схемы дифференциальных усилителей (ДУ) на основе входных копмлементарных дифференциальных каскадов на n-p-n и p-n-p транзисторах и выходных токовых зеркал [1-16]. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 30 патентов для ведущих производителей микроэлектронных изделий. Предлагаемое изобретение относится к данному подклассу устройств.

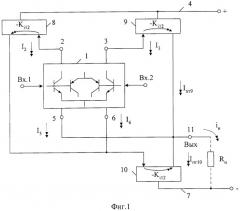

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США № 6974940, содержащий комплементарный входной дифференциальный каскад 1, имеющий первый 2 и второй 3 противофазные токовые выходы, согласованные с шиной положительного источника питания 4, третий 5 и четвертый 6 противофазные токовые выходы, согласованные с шиной отрицательного источника питания 7, первое 8, второе 9, третье 10 токовые зеркала, причем вход первого токового зеркала 8 соединен с первым 2 токовым выходом комплементарного входного дифференциального каскада 1, вход второго токового зеркала 9 соединен со вторым токовым выходом 3 комплементарного входного дифференциального каскада 1, вход третьего токового зеркала 10 соединен с четвертым 6 токовым выходом комплементарного входного дифференциального каскада 1, выход первого токового зеркала 8 связан со входом третьего токового зеркала 10, а выходы второго 9 и третьего 10 токовых зеркал соединены с выходом дифференциального усилителя 11.

Существенный недостаток известного ДУ состоит в том, что он имеет сравнительно большое значение напряжения смещения нуля Uсм (э.д.с. смещения нуля) даже при совершенно идентичных транзисторах.

Основная цель предлагаемого изобретения состоит в уменьшении составляющей напряжения смещения нуля, обусловленной влиянием токовых зеркал.

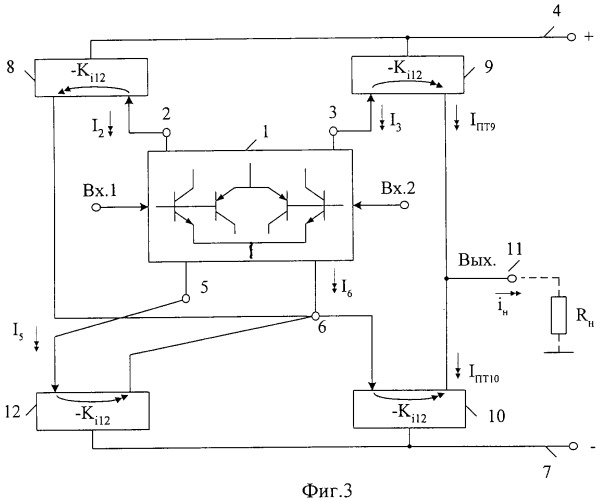

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем комплементарный входной дифференциальный каскад 1, имеющий первый 2 и второй 3 противофазные токовые выходы, согласованные с шиной положительного источника питания 4, третий 5 и четвертый 6 противофазные токовые выходы, согласованные с шиной отрицательного источника питания 7, первое 8, второе 9, третье 10 токовые зеркала, причем вход первого токового зеркала 8 соединен с первым 2 токовым выходом комплементарного входного дифференциального каскада 1, вход второго токового зеркала 9 соединен со вторым токовым выходом 3 комплементарного входного дифференциального каскада 1, вход третьего токового зеркала 10 соединен с четвертым 6 токовым выходом комплементарного входного дифференциального каскада 1, выход первого токового зеркала 8 связан со входом третьего токового зеркала 10, а выходы второго 9 и третьего 10 токовых зеркал соединены с выходом дифференциального усилителя 11, предусмотрены новые элементы и связи - в схему введено дополнительное токовое зеркало 12, токовый выход которого соединен со входом третьего токового зеркала 10, а вход - подключен к третьему 5 токовому выходу комплементарного входного дифференциального каскада 1.

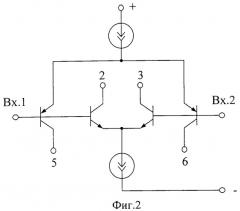

На чертеже фиг.2 показана типовая схема входного комплементарного дифференциального каскада 1 на n-p-n и p-n-p транзисторах с источниками опорного тока в общей эмиттерной цепи.

На чертеже фиг.3 показана схема заявляемого устройства и обозначены статические выходные токи основных подсхем.

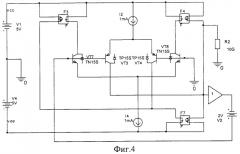

На чертежах фиг.4 - 5 показаны схемы известного (фиг.4) и заявляемого (фиг.5) устройств в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Чертеж фиг.6 характеризует зависимость напряжения смещения нуля Uсм от численных значений коэффициентов передачи по току Ki применяемых токовых зеркал 8, 9, 10, 11 заявляемого (фиг.5) и известного (фиг.4) ДУ.

Дифференциальный усилитель фиг.3 содержит комплементарный входной дифференциальный каскад 1, имеющий первый 2 и второй 3 противофазные токовые выходы, согласованные с шиной положительного источника питания 4, третий 5 и четвертый 6 противофазные токовые выходы, согласованные с шиной отрицательного источника питания 7, первое 8, второе 9, третье 10 токовые зеркала, причем вход первого токового зеркала 8 соединен с первым 2 токовым выходом комплементарного входного дифференциального каскада 1, вход второго токового зеркала 9 соединен со вторым токовым выходом 3 комплементарного входного дифференциального каскада 1, вход третьего токового зеркала 10 соединен с четвертым 6 токовым выходом комплементарного входного дифференциального каскада 1, выход первого токового зеркала 8 связан со входом третьего токового зеркала 10, а выходы второго 9 и третьего 10 токовых зеркал соединены с выходом дифференциального усилителя 11. В схему введено дополнительное токовое зеркало 12, токовый выход которого соединен со входом третьего токового зеркала 10, а вход - подключен к третьему 5 токовому выходу комплементарного входного дифференциального каскада 1.

Рассмотрим работу заявляемого ДУ фиг.3.

Если коэффициенты передачи по току всех токовых зеркал 8 и 12 равны единице (Кi=1), то в схемах фиг.1 и фиг.3 напряжение смещения нуля Uсм при идентичных транзисторах и одинаковом статическом режиме близко к нулю, т.к. отсутствует систематическая ошибка передачи статических выходных токов входного комплементарного каскада на выход 11 ДУ. Однако в практических схемах ДУ коэффициент передачи по току токовых зеркал 8-10 (особенно при их реализации по классической архитектуре (фиг.4)) всегда отличается от единицы, что приводит к появлению в цепи выхода 11 разностного тока Iн, который и обуславливает смещение нуля ДУ:

где SДУ - крутизна преобразования входного напряжения ДУ в его выходной ток.

Так, для схемы заявляемого ДУ фиг.3 ток в нагрузке Rн при нулевом входном сигнале

где Iпт9=I3Ki12.9,

I3=I2=I5=I6=I1 - выходные статические токи входного комплементарного ДУ 1,

Ki12.mn - коэффициент передачи по току nm-токового зеркала.

Таким образом, выходной статический ток ошибки ДУ, обусловленный отличием от единицы коэффициентов передачи его токовых зеркал Ki12.9=Ki12.10=Ki12.11=Ki12.8=К1, определяется формулой

При этом приращение тока в нагрузке Rн, вызванное изменением коэффициентов передач токовых зеркал

To есть при одинаковых приращениях ΔКi12, обусловленных схемотехническими особенностями токовых зеркал, влиянием температуры или напряжений питания, приращение тока в нагрузке заявляемого ДУ близко к нулю ΔIн≈0. Это свидетельствует о более высокой стабильности напряжения смещения нуля ΔIн в заявляемой схеме, которое зависит от численных значений ΔIн и крутизны преобразования входного напряжения ДУ в его выходной ток SДУ. Действительно, в ДУ-прототипе (фиг.1) чувствительность Iн к ΔKi значительно выше

Полученные выше выводы подтверждаются результатами моделирования предлагаемой (фиг.5) и известной (фиг.4) схем ДУ в среде PSpice (фиг.6). Так, при коэффициентах усиления по току токовых зеркал Ki12=0,9 выигрыш по величине Uсм достигает одного порядка.

Источники информации

1. Патент США № 6844781 В1.

2. Патентная заявка US 2006/0226908.

3. Авт. свид. СССР 530425.

4. Патент США 4757273.

5. Патентная заявка US 2001/0052818 A1.

6. Патент США № 5729177.

7. Патент США № 6642789.

8. Патент США № 6628168 В2.

9. Патент США № 4463319.

10. Патент США № 6696894 В1.

11. Патент США № 4377789.

12. Патент США № 6794940 В2.

13. Патент США № 4636743.

14. Патент WO 98/00911.

15. Патентная заявка US 2005/0024140 A1.

Дифференциальный усилитель с малым напряжением смещения нуля, содержащий комплементарный входной дифференциальный каскад (1), имеющий первый (2) и второй (3) противофазные токовые выходы, согласованные с шиной положительного источника питания (4), третий (5) и четвертый (6) противофазные токовые выходы, согласованные с шиной отрицательного источника питания (7), первое (8), второе (9), третье (10) токовые зеркала, причем вход первого токового зеркала (8) соединен с первым (2) токовым выходом комплементарного входного дифференциального каскада (1), вход второго токового зеркала (9) соединен со вторым токовым выходом (3) комплементарного входного дифференциального каскада (1), вход третьего токового зеркала (10) соединен с четвертым (6) токовым выходом комплементарного входного дифференциального каскада (1), выход первого токового зеркала (8) связан со входом третьего токового зеркала (10), а выходы второго (9) и третьего (10) токовых зеркал соединены с выходом дифференциального усилителя (11), отличающийся тем, что в схему введено дополнительное токовое зеркало (12), токовый выход которого соединен со входом третьего токового зеркала (10), а вход подключен к третьему (5) токовому выходу комплементарного дифференциального каскада (1).