Трехканальная управляющая система

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Техническим результатом изобретения является повышение надежности и контролепригодности системы. Для этого система содержит три управляющих канала, каждый из которых содержит вычислительный блок и блок ввода-вывода. Вычислительный блок содержит ЭВМ, основной и резервный приемопередатчики последовательного интерфейса, основную и резервную магистрали межпроцессорного обмена. ЭВМ выполнена с первым и вторым входами синхронизации и первым (9) и вторым (10) выходами синхронизации, являющимися первым и вторым входами синхронизации и первым и вторым выходами синхронизации вычислительного блока (2) соответственно, и первым и вторым (12) входами контроля, являющимися первым и вторым входами контроля вычислительного блока (2) соответственно, первым (13) и вторым (14) выходами контроля, являющимися первым и вторым выходами контроля вычислительного блока соответственно. Вычислительный блок и блок ввода-вывода в каждом канале соединены шиной. Блок ввода-вывода выполнен с возможностью формирования на своих выходах, под управлением вычислительного блока, сигналов управления и импульсных сигналов исправности канала системы. 4 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано при построении управляющих вычислительных устройств высокой надежности.

Известна трехканальная резервированная микропроцессорная система (а.с. №1494761, МПК G06F 11/16, опубл. 1994.03.30), состоящая из трех однотипных резервных каналов, работающих строго синхронно, каждый из которых содержит микропроцессор, блок памяти, блок ввода-вывода, регистр адреса, блок управления, блок исправления информации в двунаправленной магистрали, первый и второй блоки исправления информации. Синхронизация работы каналов обеспечивается с помощью внешних тактовых сигналов синхронных и синфазных между собой. В системе организовано мажоритарное восстановление информации между микропроцессорами, блоками ввода-вывода и блоками памяти каналов системы.

Недостатками такого технического решения являются:

- для функционирования системы необходимо формирование в каналы системы внешних тактовых сигналов высокой частоты, синхронизированных между собой;

- низкая надежность системы из-за невозможности функционировать при одном исправном канале;

- низкая контролепригодность системы, так как каналы системы не способны информировать смежные каналы и внешнюю аппаратуру о своей исправности.

Из патента №2054710 (МПК G06F 15/16, опубл. 1996.02.20) известна трехканальная управляющая система, содержащая три управляющих канала, каждый из которых содержит вычислительный блок и блок ввода-вывода. Система обеспечивает синхронное формирование выходных сигналов. Синхронное формирование выходных сигналов каналами обеспечивается с помощью межпроцессорного обмена. В системе организовано мажоритарное восстановление информации между вычислительными блоками и блоками ввода-вывода каналов системы.

Указанное устройство является наиболее близким по технической сущности и принято за прототип.

Недостатками такого технического решения являются:

- низкая надежность системы из-за невозможности функционировать при одном исправном канале;

- низкая контролепригодность системы, так как каналы системы не способны информировать смежные каналы и внешнюю аппаратуру о своей исправности.

Техническим результатом изобретения является повышение надежности и контролепригодности системы.

Для достижения указанного технического результата в трехканальной управляющей системе, содержащей три управляющих канала, каждый из которых содержит вычислительный блок и блок ввода-вывода, вычислительные блоки содержат ЭВМ, выполненную с первым и вторым входами синхронизации и первым и вторым выходами синхронизации, являющимися первым и вторым входами синхронизации и первым и вторым выходами синхронизации вычислительного блока соответственно, первым и вторым входами контроля, являющимися первым и вторым входами контроля вычислительного блока соответственно, первым и вторым выходами контроля, являющимися первым и вторым выходами контроля вычислительного блока соответственно, и основной и резервный приемопередатчики последовательного интерфейса, предназначенные для организации межпроцессорного обмена между каналами системы и соединенные с ЭВМ, вычислительный блок и блок ввода-вывода в каждом канале соединены шиной, основные приемопередатчики последовательного интерфейса вычислительных блоков каналов системы соединены основной магистралью межпроцессорного обмена, резервные приемопередатчики последовательного интерфейса вычислительных блоков каналов системы соединены резервной магистралью межпроцессорного обмена, первый выход синхронизации вычислительного блока первого канала системы соединен со вторым входом синхронизации вычислительного блока третьего канала системы, второй выход синхронизации вычислительного блока первого канала системы соединен с первым входом синхронизации вычислительного блока второго канала системы, первый выход контроля вычислительного блока первого канала системы соединен со вторым входом контроля вычислительного блока третьего канала системы, второй выход контроля вычислительного блока первого канала системы соединен с первым входом контроля вычислительного блока второго канала системы, первый выход синхронизации вычислительного блока второго канала системы соединен со вторым входом синхронизации вычислительного блока первого канала системы, второй выход синхронизации вычислительного блока второго канала системы соединен с первым входом синхронизации вычислительного блока третьего канала системы, первый выход контроля вычислительного блока второго канала системы соединен со вторым входом контроля вычислительного блока первого канала системы, второй выход контроля вычислительного блока второго канала системы соединен с первым входом контроля вычислительного блока третьего канала системы, первый выход синхронизации вычислительного блока третьего канала системы соединен со вторым входом синхронизации вычислительного блока второго канала системы, второй выход синхронизации вычислительного блока третьего канала системы соединен с первым входом синхронизации вычислительного блока первого канала системы, первый выход контроля вычислительного блока третьего канала системы соединен со вторым входом контроля вычислительного блока второго канала системы, второй выход контроля вычислительного блока третьего канала системы соединен с первым входом контроля вычислительного блока первого канала системы, а блок ввода-вывода выполнен с возможностью формирования на своих выходах, под управлением вычислительного блока, сигналов управления и импульсных сигналов исправности канала системы.

Повышение надежности достигается за счет способности системы функционировать при одном исправном канале, так как выполнение межпроцессорного обмена с помощью основных и резервных приемопередатчиков последовательного интерфейса вычислительных блоков каналов системы, соединенных вышеописанным способом, и обмен сигналами через первый и второй входы синхронизации и первый и второй выходы синхронизации вычислительных блоков каналов системы, соединенных с входами и выходами синхронизации вычислительных блоков смежных каналов системы вышеописанным способом, и первый и второй входы контроля и первый и второй выходы контроля вычислительных блоков каналов системы, соединенных с входами и выходами контроля вычислительных блоков смежных каналов системы вышеописанным способом, не блокируют работу канала при отказе двух смежных каналов. Повышение контролепригодности системы достигается за счет того, что каналы системы способны информировать смежные каналы и внешнюю аппаратуру о своей исправности для чего вычислительные блоки системы имеют первый и второй входы контроля и первый и второй выходы контроля, соединенных с входами и выходами контроля вычислительных блоков смежных каналов системы вышеописанным способом, а блок ввода-вывода выполнен с возможностью формирования на своих выходах, под управлением вычислительного блока, сигналов управления и импульсных сигналов исправности канала системы.

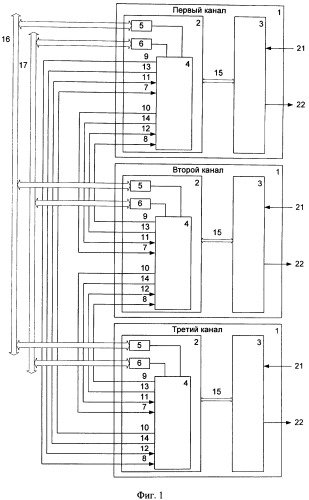

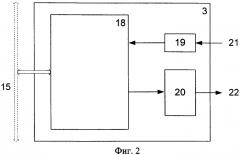

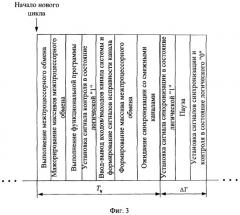

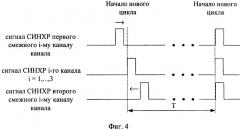

На фиг.1 представлена структурная схема трехканальной управляющей системы; на фиг.2 - структурная схема блока ввода-вывода; на фиг.3 - последовательность выполнения управляющей программы в канале системы; на фиг.4 - схема синхронизации циклов выполнения управляющих программ в каналах системы.

Трехканальная управляющая система (фиг.1) содержит три управляющих канала 1, каждый из которых содержит вычислительный блок 2 и блок ввода-вывода 3. Вычислительный блок 2 содержит ЭВМ 4 и основной 5 и резервный 6 приемопередатчики последовательного интерфейса. ЭВМ 4 выполнена с первым 7 и вторым 8 входами синхронизации и первым 9 и вторым 10 выходами синхронизации, являющимися первым и вторым входами синхронизации и первым и вторым выходами синхронизации вычислительного блока 2 соответственно, и первыми и вторым 12 входами контроля и первым 13 и вторым 14 выходами контроля, являющимися первым и вторым входами контроля и первым и вторым выходами контроля вычислительного блока 2 соответственно. Вычислительный блок 2 и блок ввода-вывода 3 в каждом канале 1 соединены шиной 15. Основные 5 приемопередатчики последовательного интерфейса вычислительных блоков 2 каналов 1 системы соединены основной 16 магистралью межпроцессорного обмена. Резервные 6 приемопередатчики последовательного интерфейса вычислительных блоков 2 каналов 1 системы соединены резервной 17 магистралью межпроцессорного обмена. Первый 9 выход синхронизации вычислительного блока 2 первого канала системы соединен со вторым входом 8 синхронизации вычислительного блока 2 третьего канала системы, второй 10 выход синхронизации вычислительного блока 2 первого канала системы соединен с первым 7 входом синхронизации вычислительного блока второго канала системы, первый 13 выход контроля вычислительного блока 2 первого канала системы соединен со вторым 12 входом контроля вычислительного блока 2 третьего канала системы, второй 14 выход контроля вычислительного блока 2 первого канала системы соединен с первым 11 входом контроля вычислительного блока 2 второго канала системы, первый 9 выход синхронизации вычислительного блока 2 второго канала системы соединен со вторым 8 входом синхронизации вычислительного блока 2 первого канала системы, второй 10 выход синхронизации вычислительного блока 2 второго канала системы соединен с первым 7 входом синхронизации вычислительного блока 2 третьего канала системы, первый 13 выход контроля вычислительного блока 2 второго канала системы соединен со вторым 12 входом контроля вычислительного блока 2 первого канала системы, второй 14 выход контроля вычислительного блока 2 второго канала системы соединен с первым 11 входом контроля вычислительного блока 2 третьего канала системы, первый 9 выход синхронизации вычислительного блока 2 третьего канала системы соединен со вторым 8 входом синхронизации вычислительного блока 2 второго канала системы, второй 10 выход синхронизации вычислительного блока 2 третьего канала системы соединен с первым 7 входом синхронизации вычислительного блока 2 первого канала системы, первый 13 выход контроля вычислительного блока 2 третьего канала системы соединен со вторым 12 входом контроля вычислительного блока 2 второго канала системы, второй 14 выход контроля вычислительного блока 2 третьего канала системы соединен с первым 11 входом контроля вычислительного блока 2 первого канала системы. Блок ввода-вывода 3 выполнен с возможностью формирования на своих выходах 18, под управлением вычислительного блока 2, сигналов управления и импульсных сигналов исправности канала системы.

Входящие в трехканальную управляющую систему блоки выполняют следующие основные функции, описанные ниже.

В качестве ЭВМ 4 в вычислительном блоке 2 используется микроконтроллер SAF-C167CR-LM_stepBA из семейства 16-ти разрядных микроконтроллеров фирмы Siemens. Микроконтроллеры этой серии имеют 16-ти разрядный центральный процессор и развитую интегрированную периферию, включающую последовательные интерфейсы, порты дискретного ввода-вывода с возможностью генерации прерываний, таймеры, аналого-цифровые преобразователи, блоки захвата и сравнения и т.д.

Основной 5 и резервный 6 приемопередатчики последовательного интерфейса вычислительного блока 2 предназначены для организации межпроцессорного обмена между каналами системы через основную 16 и резервную 17 магистрали межпроцессорного обмена. В качестве основного 5 приемопередатчика последовательного интерфейса используется интегрированный в структуру микроконтроллера SAF-C167CR-LM_stepBA приемопередатчик последовательного интерфейса USART. В качестве резервного 6 приемопередатчика последовательного интерфейса используется интегрированный в структуру микроконтроллера SAF-C167CR-LM_stepBA приемопередатчик последовательного интерфейса CAN.

Первый 7 и второй 8 входы синхронизации и первый 9 и второй 10 выходы синхронизации ЭВМ 4, являющиеся первым и вторым входами синхронизации и первым и вторым выходами синхронизации вычислительного блока 2 соответственно, предназначены для синхронизации выполнения управляющих программ в ЭВМ 4 вычислительных блоков 2 каналов 1 системы. Первый 11 и второй 12 входы контроля ЭВМ 4, являющиеся первым и вторым входами контроля вычислительного блока 2 соответственно, предназначены для контроля исправности ЭВМ 4 вычислительных блоков 2 смежных каналов. Первый 13 и второй 14 выходы контроля ЭВМ 4, являющиеся первым и вторым выходами контроля вычислительного блока 2 соответственно, предназначены для информирования смежных каналов об исправности ЭВМ 4 вычислительного блока 2 канала 1. Первый 7 и второй 8 входы синхронизации и первый 11 и второй 12 входы контроля ЭВМ 4 построены на базе интегрированных в структуру микроконтроллера SAF-C167CR-LM_stepBA портов дискретного ввода-вывода, работающих в режиме ввода с генерацией прерываний. Первый 9 и второй 10 выходы синхронизации и первый 13 и второй 14 выходы контроля ЭВМ 4 построены на базе интегрированных в структуру микроконтроллера SAF-C167CR-LM_stepBA портов дискретного ввода-вывода, работающих в режиме вывода.

Блок ввода-вывода 3 (фиг.2) содержит контроллер ввода-вывода и шины 19, блок согласования входов 20 и блок согласования выходов 21. Контроллер ввода-вывода и шины 19 обеспечивает прием сигналов от блока согласования входов 20 и передачу их значений в вычислительный блок 2 через шину 15 и управление работой блока согласования выходов 21 в соответствии с командами, поступающими от вычислительного блока 2 через шину 15. Контроллер ввода-вывода и шины 19 реализован на программируемой логической интегральной микросхеме EPM7128SQI100 фирмы Altera. Блок согласования входов 20, входы которого являются входами 22 блока, предназначен для согласования электрических характеристик входов 22 блока и контроллера ввода-вывода и шины 18. Входы 22 блока предназначены для приема сигналов от внешней аппаратуры и являются входами канала 1 системы. Блок согласования выходов 21 предназначен для согласования электрических характеристик выходов 18 блока и контроллера ввода-вывода и шины 19. Выходы 18 блока предназначены для выдачи сигналов управления и импульсных сигналов исправности канала во внешнюю аппаратуру и являются выходами канала 1 системы.

Шина 15 предназначена для обмена информацией между вычислительным блоком 2 и блоком ввода-вывода 3 и соединяет ЭВМ 4 вычислительного блока 2 и контроллер ввода-вывода и шины 19 блока ввода-вывода 3 в канале 1 системы.

Трехканальная управляющая система функционирует следующим образом.

После включения питания системы ЭВМ 4 вычислительного блока 2 каждого канала 1 системы начинает выполнять управляющую программу (фиг.3). В течение каждого цикла выполнения в ЭВМ 4 канала 1 системы управляющая программа выполняет следующие операции:

- выполнение межпроцессорного обмена через основную 16 и/или резервную 17 магистрали межпроцессорного обмена;

- мажорирование массивов межпроцессорного обмена своего канала и принятых от смежных каналов;

- выполнение функциональной программы, причем в качестве исходных данных для выполнения функциональной программы используются результаты мажорирования массивов межпроцессорного обмена;

- установка сигнала контроля на первом 13 и втором 14 выходах контроля ЭВМ 4 вычислительного блока 2 в состояние логической «1»;

- ввод состояния входов 22 блока ввода-вывода 3, вывод сигналов управления на выходы 18 блока ввода-вывода 3 и формирование импульсных сигналов исправности канала и вывод их на выходы 18 блока ввода-вывода 3;

- формирование массива межпроцессорного обмена своего канала;

- ожидание синхронизации со смежными каналами в течение времени ΔT;

- установка сигнала синхронизации на первом 9 и втором 10 выходах синхронизации ЭВМ 4 вычислительного блока 2 в состояние логической «1», через время Тц (требуемый период выполнения управляющей программы), сформированное таймером своего канала от начала нового цикла, при этом таймер перезапускается на время Тц;

- пауза, необходимая для обработки сигнала синхронизации смежными каналами;

- установка сигнала синхронизации на первом 9 и втором 10 выходах синхронизации и сигнала контроля на первом 13 и втором 14 выходах контроля ЭВМ 4 вычислительного блока 2 в состояние логического «0».

Для синхронизации выполнения управляющих программ ЭВМ 4 вычислительного блока 2 каждого канала 1 системы принимает сигналы синхронизации СИНХР от смежных каналов через первый 7 и второй 8 входы синхронизации вычислительного блока 2 и через время Тц, сформированное таймером своего канала от момента запуска нового цикла выполнения управляющей программы, устанавливает в состояние логической «1» сигнал синхронизации СИНХР на время ΔT, передаваемый в другие каналы через первый 9 и второй 10 выходы синхронизации вычислительного блока 2. Время ΔT определяется величиной паузы, необходимой для обработки сигнала синхронизации смежными каналами, и составляет несколько микросекунд. Три сигнала синхронизации (сигнал своего канала и от двух смежных каналов) программно мажорируются и по каждому второму принятому сигналу синхронизации управляющая программа в ЭВМ 4 вычислительного блока 2 канала 1 перезапускается на новый цикл выполнения, одновременно с управляющими программами в других каналах (фиг.4). Таким образом, управляющая программа в канале выполняется с периодом Тц+ΔТ, но время ΔT пренебрежимо мало по сравнению с Тц. Использование для синхронизации выполнения управляющих программ ЭВМ 4 вычислительных блоков 2 каналов 1 системы первого 7 и второго 8 входов синхронизации и первого 9 и второго 10 выходов синхронизации вычислительных блоков 2 каналов 1 системы, соединенных с входами и выходами синхронизации вычислительных блоков смежных каналов системы вышеописанным способом, повышает надежность системы за счет способности системы функционировать при одном исправном канале, так как канал 1 системы (вычислительный блок 2 и блок ввода-вывода 3) не блокируется при выполнении синхронизации даже при отказе двух смежных каналов.

Каждый канал передает смежным каналам свой массив межпроцессорного обмена и принимает массивы межпроцессорного обмена от смежных каналов по основной 16 и/или резервной 17 магистралям межпроцессорного обмена. В состав массива межпроцессорного обмена входят входные сигналы (результаты ввода состояния входов 22 блока ввода-вывода 3) и сигналы результатов выполнения управляющей программы в канале. Мажорирование массивов межпроцессорного обмена своего канала и принятых от смежных каналов позволяет выполнять функциональную программу в каналах системы с одинаковыми исходными данными и 11 маскировать единичные отказы на входах каналов системы. Это обеспечивает синхронное формирование каналами по времени (обеспечивается синхронизацией выполнения управляющих программ в каналах системы) и значениям (обеспечивается мажорированием массивов межпроцессорного обмена своего канала и принятых от смежных каналов) сигналов управления и импульсных сигналов исправности каналов на выходах 18 блоков ввода-вывода 3 каналов 1 системы. Использование для организации межпроцессорного обмена между каналами системы основных 5 и резервных 6 приемопередатчиков последовательного интерфейса вычислительных блоков 2 каналов 1 системы, соединенных вышеописанным способом, повышает надежность системы за счет способности системы функционировать при одном исправном канале, так как канал 1 системы способен функционировать при отказе двух смежных каналов независимо от результатов выполнения межпроцессорного обмена.

Сигнал исправности канала на выходах 18 блока ввода-вывода 3 формируется управляющей программой импульсно, в каждом цикле ее выполнения (например, в одном цикле выполнения управляющей программы сигнал исправности устанавливается в состояние логической «1», в другом - в состояние логического «0») и информирует внешнюю аппаратуру об исправности аппаратно-программных средств этого канала системы. В случае отказа вычислительного блока 2, шины 15, блока ввода-вывода 3 или управляющей программы сигнал исправности канала становится потенциальным, а не импульсным, как при нормальной работе канала. Переход сигналов исправности канала на выходах 18 блока ввода-вывода 3 из импульсной формы в потенциальную позволяет внешней аппаратуре выявить отказ этого канала системы и исключить сигналы управления от этого канала из своей схемы голосования. Выполнение блока ввода-вывода 3 с возможностью формирования на своих выходах 18, под управлением вычислительного блока 2, сигналов управления и импульсных сигналов исправности канала системы повышает контролепригодность системы за счет того, что каналы 1 системы способны информировать внешнюю аппаратуру о своей исправности с помощью импульсного сигнала исправности канала, формируемого управляющей программой.

Сигнал контроля на первом 13 и втором 14 выходах контроля вычислительного блока 2 формируются управляющей программой импульсно, в каждом цикле ее выполнения и информирует смежные каналы системы об исправности аппаратно-программных средств этого канала системы. Каждый канал 1 принимает сигналы контроля от смежных каналов через первый 11 и второй 12 входы контроля вычислительного блока 2 канала 1 системы. В случае, если результаты выполнения управляющей программы в канале отличаются от результатов выполнения управляющих программ в смежных каналах, а смежные каналы работают синхронно и подтверждают свою исправность формированием своих сигналов контроля, канал прекращает формирование сигнала исправности канала на выходах 18 блока ввода-вывода 3. Выполнение вычислительного блока 2 с первым 11 и вторым 12 входами контроля и первым 13 и вторым 14 выходами контроля, соединенных с входами и выходами контроля вычислительных блоков смежных каналов системы вышеописанным способом, повышает надежность системы за счет способности системы функционировать при одном исправном канале, так как обмен сигналами контроля, формируемыми управляющими программами каналов системы, через первый 11 и второй 12 входы контроля и первый 13 и второй 14 выходы контроля вычислительных блоков 2 каналов 1 системы не блокирует работу канала 1 при отказе двух смежных каналов и повышает контролепригодность системы за счет того, что каналы системы способны информировать смежные каналы о своей исправности.

При отсутствии сигналов контроля и межпроцессорного обмена по основной 16 и резервной 17 магистралям межпроцессорного обмена от смежных каналов канал 1 переходит в одноканальный режим работы и прекращает выполнение мажорирования перед выполнением функциональной программы, формируя сигналы управления на выходы 18 блока ввода-вывода на основе собственных значений входов канала 22. Смежная аппаратура выявляет исправный канал на основе сигналов исправности канала, формируемых на выходах 18 блока ввода-вывода 3, и может выбирать сигналы управления от единственного исправного канала.

Трехканальная управляющая система, содержащая три управляющих канала, каждый из которых содержит вычислительный блок и блок ввода-вывода, отличающаяся тем, что вычислительный блок содержит ЭВМ, выполненную с первым и вторым входами синхронизации и первым и вторым выходами синхронизации, предназначенными для синхронизации выполнения управляющих программ в ЭВМ вычислительных блоков каналов системы и являющимися первым и вторым входами синхронизации и первым и вторым выходами синхронизации вычислительного блока соответственно, первым и вторым входами контроля, предназначенными для контроля исправности ЭВМ вычислительных блоков смежных каналов и являющимися первым и вторым входами контроля вычислительного блока соответственно, первым и вторым выходами контроля, предназначенными для информирования смежных каналов об исправности ЭВМ вычислительного блока канала и являющимися первым и вторым выходами контроля вычислительного блока соответственно, и основной и резервный приемопередатчики последовательного интерфейса, предназначенные для организации межпроцессорного обмена между каналами системы и соединенные с ЭВМ, вычислительный блок и блок ввода-вывода в каждом канале соединены шиной, основные приемопередатчики последовательного интерфейса вычислительных блоков каналов системы соединены основной магистралью межпроцессорного обмена, резервные приемопередатчики последовательного интерфейса вычислительных блоков каналов системы соединены резервной магистралью межпроцессорного обмена, первый выход синхронизации вычислительного блока первого канала системы соединен со вторым входом синхронизации вычислительного блока третьего канала системы, второй выход синхронизации вычислительного блока первого канала системы соединен с первым входом синхронизации вычислительного блока второго канала системы, первый выход контроля вычислительного блока первого канала системы соединен со вторым входом контроля вычислительного блока третьего канала системы, второй выход контроля вычислительного блока первого канала системы соединен с первым входом контроля вычислительного блока второго канала системы, первый выход синхронизации вычислительного блока второго канала системы соединен со вторым входом синхронизации вычислительного блока первого канала системы, второй выход синхронизации вычислительного блока второго канала системы соединен с первым входом синхронизации вычислительного блока третьего канала системы, первый выход контроля вычислительного блока второго канала системы соединен со вторым входом контроля вычислительного блока первого канала системы, второй выход контроля вычислительного блока второго канала системы соединен с первым входом контроля вычислительного блока третьего канала системы, первый выход синхронизации вычислительного блока третьего канала системы соединен со вторым входом синхронизации вычислительного блока второго канала системы, второй выход синхронизации вычислительного блока третьего канала системы соединен с первым входом синхронизации вычислительного блока первого канала системы, первый выход контроля вычислительного блока третьего канала системы соединен со вторым входом контроля вычислительного блока второго канала системы, второй выход контроля вычислительного блока третьего канала системы соединен с первым входом контроля вычислительного блока первого канала системы, а блок ввода-вывода выполнен с возможностью формирования на своих выходах, под управлением вычислительного блока, сигналов управления и импульсных сигналов исправности канала системы, предназначенных для информирования внешней аппаратуры об исправности канала системы.