Декодер трехуровневого кодированного сигнала

Иллюстрации

Показать всеПредлагаемым изобретением решается задача комплексного расширения функциональных возможностей декодера и обеспечение его помехоустойчивости с помощью непрерывной последовательности входных тактовых импульсов IC за счет помехоустойчивого формирования выходного синхронизированного сигнала OZ последовательного двоичного кода и выходных синхросигналов битовой синхронизации OCZ, паузы OPZ и начала паузы ОРС для кода RZ или ВТК с помощью заградительной фильтрации асинхронного трехуровневого кодированного сигнала Z(1:0) как помехи при длительности каждого изменения этого сигнала, не превышающей пороговой длительности P·Tic для Р≥1, где Р - пороговое число, Tic - длительность периода тактовых импульсов IC. Декодер содержит триггеры (1-4), приемник-преобразователь (5), вход (6) трехуровневого кодированного сигнала, элементы ИЛИ-НЕ (7-9), синхронный счетчик (10), элементы ИЛИ (11-13), элемент задержки (14), элементы И (15-16), элементы Исключающее ИЛИ (17-18), регистр (19), компаратор (20), элементы И-НЕ (21-24), вход (25) выбора типа декодируемого трехуровневого кодированного сигнала, тактовый вход (26), кодовый вход (27) порога обнаружения паузы, кодовый вход (28) порога обнаружения синхросигнала, первый выход, являющийся выходом триггера (1) и синхронизированного сигнала OZ последовательного двоичного кода, и второй, третий и четвертый выходы, являющиеся соответственно выходами элемента (15), триггера (3) и элемента (9) и выходами синхросигналов битовой синхронизации OCZ, паузы OPZ и начала паузы ОРС соответственно. 1 ил.

Реферат

Изобретение относится к области вычислительно техники, предназначено для приема входного электрического или оптического трехуровневого кодированного сигнала (ТКС) IZ последовательного двоичного самосинхронизирующегося кода (ПДСК) с преобразованием в двухразрядный асинхронный трехуровневый кодированный сигнал Z(1:0), определяющий асинхронные сигналы Z1 и Z0 соответственно информации и битовой синхронизации для последующего помехоустойчивого декодирования и синхронизации ТКС за счет формирования выходного синхронизированного сигнала OZ двухуровневого последовательного двоичного кода (ПДК) без возврата к нулю и выходных синхросигналов битовой синхронизации OCZ, паузы OPZ и начала паузы ОРС с помощью входной непрерывной последовательности тактовых импульсов IC, и может быть использовано при построении любых синхронных автоматов с памятью для помехоустойчивого ввода асинхронных данных с помощью ТКС кода RZ или высокоскоростного трехуровневого кода (ВТК), в частности, может использоваться в качестве полного помехоустойчивого синхронного декодера кода RZ с возвратом к нулю по ГОСТ 18977-79 и РТМ 1495-75.

Известно [1, с.48], что в современных информационно-измерительных радиоэлектронных системах для обмена информацией с помощью ТКС наиболее рационально использовать код RZ, поскольку по сравнению с ним другие известные ПДСК никакими преимуществами не обладают и могут использоваться иногда в связи с недостатком сведений у разработчиков о преимуществах и недостатках различных методов кодирования (модулирования) двухуровневого ПДК, стандартный вид которого имеет англоязычную аббревиатуру NRZ - Non Return to Zero.

Однако трехуровневый код RZ как и любой двухуровневый код класса 1В2В (например, манчестерский, Миллера и т.п.) требует удвоенной полосы пропускания по сравнению с NRZ - см., например, [2, с.260]. В этой связи для повышения скорости обмена в [2, с.260-263] предложен ВТК, имеющий такую же полосу пропускания как и NRZ. Предложенный ВТК является самосинхронизирующимся, поскольку в нем на каждой границе между битами присутствует перепад уровня входного ТКС IZ, при этом передача логического «0» осуществляется минимальным уровнем сигнала IZ или следующим после него нулевым (средним) уровнем, а передача логической «1» - максимальным уровнем сигнала IZ или следующим после него нулевым уровнем.

В коде RZ по ГОСТ 18977-79 и РТМ 1495-75 (см., например, [3, с.57-54]) информация передается двоичными словами с помощью ТКС IZ при длительности паузы Тп между словами

так, что каждый бит слова передается в течение битового интервала - периода Tiz битовой синхронизации

где Fiz - реальная частота импульсов битовой синхронизации передачи информации в передатчике ТКС IZ;

TXiz - при TXiz=T1iz длительность минимального или максимального информационного уровня сигнала IZ, а при TXiz=T0iz длительность нулевого уровня сигнала IZ;

Т (или F=1/T) - номинальная длительность периода Tiz (или номинальная частота) импульсов битовой синхронизации передачи информации ТКС IZ.

С учетом (1) и (2) отметим, что длительность информационной фазы в коде RZ равна T1iz=Tiz/2 при T1iz=T0iz, а в ВТК - равна T1iz=Tiz или T0iz=Tiz, и в каждом из этих кодов момент начала синхросигнала паузы ОРС, отсчитываемый от начала информационной фазы последнего принимаемого перед паузой бита в слове, следует выбирать при условии

где Т1орс - время обнаружения начала паузы, отсчитываемое от начала режима обнаружения паузы до начала синхросигнала начала паузы ОРС.

Если входной ТКС IZ является электрическим дифференциальным (разностным) кодированным сигналом

кода RZ или ВТК, то в качестве приемника-преобразователя можно использовать один из двух приемников-преобразователей микросхемы 1567АП1 [2, с.80-83], формирующий сигналы выходного прямого кода Z(1:0)=Z1Z0, означающего следующее:

прием бита «0» кода RZ или ВТК при

прием бита «1» кода RZ или ВТК при

пауза в любом коде или возврат к нулю в RZ или прием в ВТК второго бита «0» (или «1») после приема (5) (или (6)) при

где IZa и IZb - первая и вторая компоненты дифференциального ТКС IZ, каждая из которых измеряется относительно общей шины (корпуса) приемника-преобразователя;

Z1 - сигнал информации, являющийся признаком максимального уровня трехуровневого кодированного сигнала IZ (4);

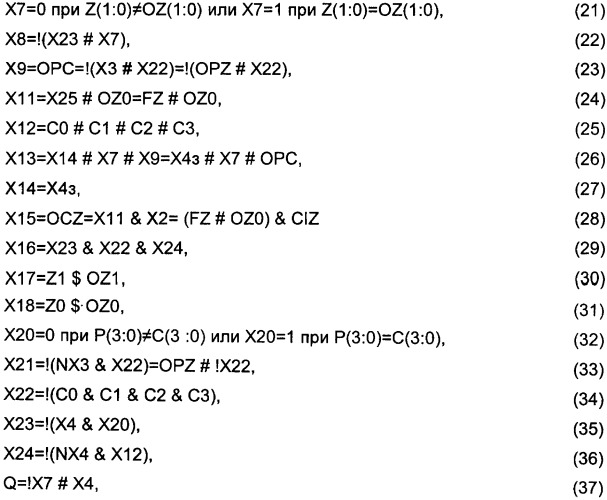

Z0 - сигнал синхронизации, являющийся признаком минимального или максимального уровня трехуровневого кодированного сигнала IZ (4).

Известно [1, с.41], что практически никакие методы экранирования и разнесения проводов линий цифровой связи от энергетических проводов не могут гарантировать отсутствие в линии связи (ЛС) помех (наводок). Это означает, что полезный сигнал IZ (4) всегда существует совместно с помехами, и задача заключается в гарантированном, т.е. с определенным запасом устойчивости, выделении сигнала на фоне помех.

Для упрощения технической реализации передача сигнала IZ (4) кода RZ производится по несогласованной ЛС при Ri>R, где Ri и R - входное сопротивление приемника-преобразователя сигнала IZa (или IZb) и волновое сопротивление ЛС соответственно. Поэтому при прямоугольной форме сигнала IZ (4) на выходе передатчика сигнал IZa (или IZb) на входе декодера в начале и в конце фазы приема (5) или (6) имеет форму затухающих колебаний в течение длительности Тпп переходного процесса - см., например, [4, с.117, рис.4.7].

Известно также [1, с.32-35; 5], что при передаче информации кодированными (модулированными) импульсными сигналами существенное значение имеет форма сигнала IZ (4). В этой связи в коде RZ при Т1iz=T0iz=Tiz./2 считают целесообразным формировать сигнал IZ (4) трапецеидальной формы с длительностью как нарастания, так и спада сигнала IZ (4), равной Tiz/4 - см. в [1, с.34, рис.2.3].

С кодового выхода приемника-преобразователя кодовый сигнал Z(1:0) вводится в цифровую систему (сложный асинхронный или синхронный автомат с памятью), которая функционирует обычно по непрерывной последовательности тактовых импульсов IC единого системного тактового генератора, по отношению к частоте которого сигнал Z(1:0) является асинхронным и искаженным помехами, поскольку следует также учитывать (см., например, [6]), что в самой цифровой системе (как любом микроэлектронном устройстве) можно выделить каналы связи для передачи сигналов, каждый из которых содержит источник сигнала, ЛС и приемник сигнала. Любой канал связи может быть как источником, так и приемником помех. В реальных условиях на каналы связи могут воздействовать несколько источников внешних индустриальных или естественных помех и внутренних помех с различными видами паразитных связей: емкостной, индуктивной, резистивной или комплексной.

Таким образом, синхронизируемый кодированный сигнал Z(1:0) маскируется помехами, и в общем случае задача его синхронизации и декодирования должна решаться с учетом возможного искажения его различными помехами, в их числе фазовыми помехами [7, с.103] - джиттером (jitter-дрожание) и вандером (wander - странствие), обусловленными, например, перекрестными помехами от других ЛС, пульсациями напряжений питания передатчика и приемника-преобразователя сигнала IZ (4), неблагоприятными кодовыми комбинациями при формировании сигнала IZ (4) линейным передатчиком, дневными-ночными перепадами температуры (сверхнизкочастотным вандером).

На основании изложенного выше можно сказать, что при построении современных цифровых систем обработки информации и управления и их составных частей проблема учета помех практически всегда актуальна вследствие наличия различных внешних и внутренних помех, снижения энергетического уровня информационных сигналов и усложнения систем.

Таким образом, при вводе информации в цифровую систему с помощью ТКС IZ возникает необходимость декодирования и синхронизации сигнала Z(1:0) с учетом длительностей (1)-(3) для кода RZ или ВТК и возможного искажения сигнала Z(1:0) различными помехами.

С учетом изложенного выше (см. (1)-(7)) определяем, что функция декодирования и синхронизации сигнала Z(1:0) кода RZ или ВТК, осуществляемая с помощью входной непрерывной последовательности тактовых импульсов IC, заключается в формировании синхронизированного сигнала OZ двухуровневого ПДК в сопровождении синхросигналов битовой синхронизации OCZ, начала паузы ОРС и паузы OPZ.

Здесь следует отметить, что в асинхронной системе синхронизация (изменение состояния асинхронного автомата с памятью при установленных входных информационных сигналах) производится с помощью соответствующих синхроимпульсов (при формировании с помощью тактовых импульсов IC длительность синхроимпульса совпадает с длительностью T0ic нулевой при IC=0 или с длительностью T1ic единичной фазы при IC=1 периода Tic=T0ic+T1ic тактовых импульсов IC), а в синхронной системе синхронизация (изменение состояния синхронного автомата с памятью при установленных входных информационных сигналах) осуществляется логически по функции «И», т.е. по фронтам (переходам из «0» в «1») или срезам (переходам из «1» в «0») тактовых импульсов IC и соответствующим синхросигналам, установленным до прихода фронта или среза IC, причем длительность каждого синхросигнала обычно кратна целому числу периодов тактовых импульсов IC, период которых (см., например, [8]) для декодера кода RZ или ВТК определяют из условия

при выборе K≥4 с учетом быстродействия элементной базы декодера и реальных допусков на джиттер (дрожание переключений) сигнала Z(1:0).

Принимая во внимание (4)-(8) для дальнейшего описания выполнение полной функции тактовой синхронизации асинхронного сигнала Z(1:0) с помощью тактовых импульсов IC в общем случае определим как формирование синхронизированного цифрового кодированного сигнала OZ(1:0) приема (5) или (6) или (7) длительностью

при переключении OZ(1:0) по фронту синхросигнала CIZ кодированного сигнала при формировании CIZ длительностью

при каждом пороговом обнаружении перехода синхронизируемого сигнала Z(1:0) из любого состояния в другое состояние, формирование выходного синхросигнала начала паузы ОРС длительностью Topc=Tic при пороговом обнаружении перехода сигнала Z(1:0) из состояния «01» или «11» в состояние «00» и, после окончания синхросигнала ОРС, формирование выходного синхросигнала паузы OPZ длительностью Topz, кратной целому числу периодов Tic, где Т1о - длительность единичной фазы сигнала OZ(1:0) при OZ(1:0)=01 или OZ(1:0)=11; T0o - длительность нулевой (возвратной) фазы сигнала OZ(1:0) при OZ(1:0)=00; k - целое число, не меньшее «2».

Далее реальную длительность каждого изменения сигнала Z(1:0) обозначим через Ti, и в процессе синхронизации изменение сигнала Z(1:0), в зависимости от длительности Ti, определим как помеху при

как корректный информационный сигнал при

или как сигнал с неопределенным (искаженным) временным параметром

который в процессе обработки может быть отнесен к помехе (11) или к корректному сигналу (12),

где I - десятичное число «1», «2» и «0» соответственно определяющее значение «01», «11» и «00» сигнала IZ(1:0) согласно (5), (6) и (7);

Р - пороговое целое число, не меньшее «1», выбираемое с учетом (8).

Очевидно, что из-за искажения сигнала Z(1:0) всевозможными помехами наличие интервала неопределенности типа (13), длительностью Tic, неустранимо, так как обусловлено асинхронностью любых изменений сигнала Z(1:0) относительно тактовых импульсов IC.

Согласно [7, с.258, рис.9.23] при построении декодеров ПДСК полагают, что джиттер Ti не превышает Tiz/4, и при отсутствии других помех определяет значение величины Ti согласно выражению

где Tmin=(TXiz-Tiz/4) - нижняя граница величины Ti;

Tmax=(TXiz+Tiz/4) - верхняя граница величины Ti.

На основании (2), (8) и (14) величины Tmin и Tmax определяем формулами

и на основании (15) и (12) при Tic=T/K, для выбора в общем случае чисел «Р» и «К» составляем уравнение

где FZ - признак типа ТКС, определяющий при FZ=0 кодирование в коде RZ, а при FZ=1 кодирование в ВТК;

«!» - оператор логической операции «НЕ» на языке ABEL.

Подставляя в уравнение (17) величины FZ=0 и Р=1, вычисляем К=10 и определяем, что корректное декодирование кода RZ возможно при величине Tic, равной

Подставляя в уравнение (17) величины FZ=1 и Tic=T/10, вычисляем Р=5, и при условии (18) пороговое число «Р» определяем формулой

В настоящее время и на длительную перспективу в процессе обработки информации основным методом синхронизации в цифровых системах является синхронный метод тактирования по фронтам или срезам единого генератора тактовых импульсов с помощью синхросигналов - см., например, [9, с.121-123: 3.5. Введение в проблематику и методику проектирования автоматов с памятью].

На основании изложенного выше можно сказать, что создание декодера трехуровневого кодированного сигнала кода RZ или ВТК для ввода информации в синхронную цифровую систему с требуемыми характеристиками с учетом длительностей (1)-(3), Тпп и определений (5)-(17) при приемлемых аппаратурных затратах представляет актуальную техническую задачу, решение которой позволит в целом повысить качество разрабатываемых синхронных цифровых систем для ввода и обработки информации, являющихся составными частями современных информационно-измерительных комплексов.

Известен декодер [10], содержащий два компаратора, триггер с инверсными асинхронными входами сброса и установки, первый и второй формирователи коротких импульсов CD1 и CD0 соответственно, элемент ИЛИ, вход одномерного трехуровневого кодированного сигнала IU с максимальным, средним и минимальными уровнями, соединенный с инвертирующим входом первого компаратора и неинвертирующим входом второго компаратора, входы первого Е1 и второго Е0 пороговых напряжений, соединенных соответственно с неинвертирующим входом первого и инвертирующим входом второго компараторов, выход сигнала OTD двухуровневого ПДК, являющийся прямым выходом триггера, и выход сигнала битовой синхронизации OCD, являющийся выходом элемента ИЛИ, первый и второй входы которого соединены с выходами первого и второго формирователей, вход установки триггера соединен с входом первого формирователя и выходом первого компаратора, являющегося выходом инверсного сигнала ND1 приема «1» ВТК, а выход второго компаратора, являющегося выходом инверсного сигнала NDO приема «0» ВТК, соединен с входом сброса триггера и входом второго формирователя, причем каждый из формирователей содержит элемент задержки, элемент Исключающее ИЛИ, вход, являющийся первым входом элемента Исключающее ИЛИ, и выход являющийся выходом элемента Исключающее ИЛИ, второй вход которого через элемент задержки связан с входом формирователя.

По сигналам ND1 и ND0 (при необходимости) сигналы Z1 и Z0 можно получить по логическим формулам Z1=!ND1=D1, Z0=!(ND1&ND0)=D1#D0, где «!=N», «&» и «#» - на языке ABEL операторы операций «НЕ», «И» и «ИЛИ» соответственно.

Декодер [10] при Е1>Е0 по входному электрическому ТКС IU, соответствующему ВТК, работает так, что первый и второй компараторы вырабатывают инверсные сигналы ND1 приема «1» и ND0 приема «0» ВТК согласно выражениям

ND1=0 при IU>E1 или ND1=1 при IU<E1,

ND0=0 при IU<E0 или ND0=1 при IU>E1,

триггер по ND1=0 (или ND0=0) устанавливается в OTD=1 (или сбрасывается в OTD=0), первый (или второй) формирователь по каждому срезу или фронту сигнала ND1 (или ND0) формирует короткий импульс CD1=1 (или CD0=1), а элемент ИЛИ по импульсам CD1 и CD0 формирует выходные импульсы битовой синхронизации OCD=(CD1 # CD0) выходного сигнала OTD двухуровневого ПДК.

Основным недостатком декодера [10] является ограниченность функциональных возможностей (он предназначен для работы в асинхронном устройстве с тактированием выходного сигнала OTD двухуровневого ПДК по асинхронным импульсам битовой синхронизации OCD с определением начала паузы и паузы в процессе последующего анализа частоты следования OCD) и низкая помехоустойчивость, если сигнал IU маскируется помехами.

С учетом изложенного можно сказать, что декодер [10] имеет смысл применять в том случае, когда входной сигнала IU помехоустойчив, например, формируется в процессе помехоустойчивого преобразования оптического трехуровневого кодированного сигнала IZ в электрический сигнал IU.

Известен декодер [11], являющийся частью технического решения [11], и содержащий приемник-декодер, обнаружитель паузы, два элемента НЕ, триггер, входы цифрового дифференциального сигнала IZ (4) кода RZ, соединенные с входами приемника-декодера, кодовый вход кода порога Y(3:0) обнаружения паузы и тактовый вход, соединенные соответственно с кодовым и тактовым входами обнаружителя, выходы инверсного потенциального сигнала ONPZ паузы и инверсного синхроимпульса ONCP начала паузы, являющиеся первым и вторым выходами обнаружителя соответственно, выход сигнала OZ двухуровневого ПДК, соединенный с выходом триггера, инверсный асинхронный вход установки которого через первый элемент НЕ связан с информационным выходом сигнала Z1 приемника-декодера, и выход инверсного сигнала ONZ0 битовой синхронизации, соединенный с входом асинхронной установки обнаружителя в режим обнаружения и выходом второго элемента НЕ, вход которого соединен с выходом асинхронного сигнала Z0 битовой синхронизации приемника-декодера и тактовым входом триггера, информационный вход которого соединен с шиной Логического «0».

В течение паузы приемник-декодер вырабатывает сигналы Z1=0 и Z0=0, на выходах декодера [11] установлены сигналы OZ=0 (или OZ=1), ONZ0=!Z0=1 (где !=N - на языке ABEL оператор операции НЕ), ONPZ=0, ONCP=1.

При поступлении информации в начале каждой информационной фазы T1iz при Z1=1 триггер по сигналу NZ1=0 с выхода первого элемента НЕ асинхронно фиксируется в OZ=1, а при Z1=0 триггер по фронту сигнала Z0=1 сбрасывается в OZ=0. В течение Т1iz сигнал ONZ0=0 асинхронно устанавливает обнаружитель в режим обнаружения (в счетчик обнаружителя записывается код порога Y(3:0) обнаружения), а по фронту сигнала ONZ0 (по срезу сигнала Z0, т.е. переходу Z0 из «1» в «0») с декодера [11] считывается значение последовательного бита OZ информации, установленного в триггере согласно приему бита «0» (5) или приему бита «1» (6).

С наступлением паузы, в зависимости от значений кода порога Y(3:0)=Y3Y2Y1Y0 и периода Tic, через время обнаружения начала паузы Т1орс=(8·Y3+4·Y2+2·Y1+Y0-1)·Tic обнаружитель генерирует по IC=1 синхроимпульс начала паузы ONCP=0 и после его окончания выставляет потенциальный сигнал паузы ONPZ=0, который не является синхросигналом, так как сбрасывается в ONPZ=1 асинхронно по ONZ0=0. Код Y(3:0) порога загружается в обнаружитель асинхронно сигналом ONZO=0, длительность Ti которого из (15) и (16) определяется ограничением 0,2·Т<<Ti<0,99·T, с учетом которого значение Y(3:0) должно быть выбрано при условии (18) так, чтобы величина

удовлетворяла ограничению (3).

Далее из (3) и (20) получаем приближенное равенство Т1орс≈1,34·Т, которое при условии (18) преобразуется в ограничение 13,4<(8·Y3+4·Y2+2·Y1+Y0-1), на основании которого выбираем код Y(3:0)=1110, и рассчитываем длительность Т1орс=14·Tic=1,4·Т, удовлетворяющую ограничению (3).

Основным недостатком декодера [11] является ограниченность функциональных возможностей (он предназначен для работы в асинхронном устройстве с тактированием по асинхронному сигналу ONZ0 битовой синхронизации, синхроимпульсам ONCP начала паузы и потенциальному сигналу паузы ONPZ, который не является синхросигналом) и низкая помехоустойчивость при передаче сигнала IZ (4) от передатчика на приемник-декодер по несогласованной ЛС при Ri>R, где Ri и R - входное сопротивление приемника-декодера сигнала IZa (или IZb) и волновое сопротивление ЛС соответственно.

Из известных технических решений наиболее близким по технической сущности к предлагаемому является декодер [12], представляющий собой часть технического решения [12], и содержащий демодулятор (т.е. приемник-преобразователь), вход трехуровневого кодированного сигнала, являющегося дифференциальным сигналом IZ (4) кода RZ, входы компонент которого являются входами демодулятора, генератор одиночных импульсов, специализированный счетчик, четыре выхода и тактовый вход сигнала IC, соединенный с тактовыми входами генератора и счетчика, выход сигнала Z1=OZ последовательного двоичного кода, являющийся первым выходом устройства и информационным выходом демодулятора, выход асинхронного сигнала битовой синхронизации Z0 которого соединен с асинхронными входами генератора и счетчика, второй выход, соединенный с выходом генератора и являющийся выходом синхроимпульса CZ1 битовой синхронизации сигнала Z1 двухуровневого ПДК, третий выход, являющийся синхросигналом готовности GPC при обнаружении паузы, соединенный с первым выходом счетчика, и четвертый выход, соединенный с вторым выходом счетчика и являющийся синхроимпульсом конца обнаружения паузы СР.

В процессе функционирования декодер [12] по сигналу IZ (4) кода RZ на первом выходе формирует сигнал Z1 двухуровневого ПДК информации, принимаемой 32-разрядными словами, на втором выходе синхроимпульсы CZ1 битовой синхронизации каждого бита Z1 двухуровневого ПДК, на третьем выходе синхросигнал готовности GCP длительностью Tic для чтения введенного с систему 32-разрядного слова, на четвертом синхроимпульс конца обнаружения паузы СР, формируемый по окончании GCP и предназначенный для установки системы в исходное состояние для приема следующего 32-разрядного слова сообщения,

По входному сигналу IZ (4) кода RZ демодулятор декодера [12] через время Тпп<<Т/4 каждого переходного процесса на своих выходах формирует кодовый сигнал Z(1:0)=Z1Z0 согласно (5)-(7) так, что в течение паузы Тп (1) или фазы T0iz возврата к нулю сигнал Z(1:0)=00, а в течение информационной фазы T1iz при приеме (5) бита «0» сигнал Z(1:0)=01, а при приеме (6) бита «1» сигнал Z(1:0)=11.

При поступлении на входы декодера [12] сигнала IZ (4) кода RZ в течение каждого битового периода Tiz (2) при Т1iz=T0iz=Tiz/2=0,5·Т работу декодера [12] при приеме 32-разрядного слова можно описать следующим образом.

В течение информационной фазы T1iz сигнал Z0=1 асинхронно сбрасывает счетчик, а по каждому фронту (переходу из «0» в «1») сигнала Z0 генератор каждый раз с помощью входных тактовых импульсов IC, следующих с периодом Tic=Т/4, функционирует так, что при Z0=1 в ближайшем промежутке времени от 0·Т до 0,5·Т формирует единичный синхроимпульс CZ1=1 битовой синхронизации бита Z1 кода NRZ.

После приема каждого слова в течение каждой паузы демодулятор вырабатывает сигналы Z1=0 и Z0=0, а после начала паузы, через время обнаружения паузы ТОП≈4·Т, счетчик формирует сначала один синхросигнал готовности GCP для чтения введенного в систему 32-разрядного слова, а затем формирует синхроимпульс конца обнаружения паузы СР.

Основным недостатком декодера [12] является ограниченность функциональных возможностей, поскольку он предназначен для декодирования только кода RZ в асинхронном устройстве с тактированием по синхроимпульсам CZ1 и СР при фиксированной (а не программно выбираемой) длительности Tmin=0,5·T при обнаружении паузы через ТОП≈4·Т после окончания каждого 32 импульса битовой синхронизации Z0=1, а в общем случае в процессе декодирования следует декодировать информационную фазу кода RZ при Tmin=0,2·T и Tic=T/10 согласно (15) и (18), а начало или конец паузы обнаруживать с максимальным быстродействием на основе ограничения (3) и выражения типа (20).

Предлагаемым изобретением решается задача комплексного расширения функциональных возможностей декодера и обеспечение его помехоустойчивости с помощью непрерывной последовательности входных тактовых импульсов IC за счет помехоустойчивого формирования выходного синхронизированного сигнала OZ двухуровневого ПДК и выходных синхросигналов битовой синхронизации OCZ, паузы OPZ и начала паузы ОРС для кода RZ или ВТК с помощью заградительной фильтрации асинхронного кодированного сигнала Z(1:0) как помехи при длительности Ti каждого изменения этого сигнала, не превышающей пороговой длительности P·Tic с учетом (5)-(17) для P≥1, где Р - пороговое число, Tic - длительность периода тактовых импульсов IC.

Для достижения этого технического результата в декодер трехуровневого кодированного сигнала, содержащий приемник-преобразователь, разрядные выходы старшего и младшего разрядов кодового выхода которого являются выходами асинхронных сигналов информации и синхронизации соответственно, вход трехуровневого кодированного сигнала, являющийся входом приемника-преобразователя, двоичный счетчик, тактовый вход и четыре выхода, дополнительно введены четыре триггера, три элемента ИЛИ-НЕ, три элемента ИЛИ, элемент задержки, два элемента И, два элемента Исключающее ИЛИ, двухразрядный регистр с параллельным вводом и выводом информации, компаратор, четыре элемента И-НЕ, вход выбора типа декодируемого трехуровневого кодированного сигнала, являющийся первым входом первого элемента ИЛИ, кодовый вход порога обнаружения паузы и кодовый вход порога обнаружения синхросигнала кодированного сигнала, причем выход старшего разряда приемника-преобразователя соединен с информационным входом первого триггера, первым входом первого элемента Исключающее ИЛИ и входом старшего разряда регистра, выход старшего разряда которого соединен с вторым входом первого элемента Исключающее ИЛИ, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом второго элемента Исключающее ИЛИ, первый вход которого соединен с входом разрешения записи первого триггера, выходом младшего разряда приемника-преобразователя и входом младшего разряда регистра, выход младшего разряда которого соединен с вторыми входами второго элемента Исключающее ИЛИ и первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с тактовыми входами первого триггера и регистра и прямым выходом второго триггера, инверсный выход которого соединен с входом сброса третьего триггера, инверсный выход которого соединен с первым входом первого элемента И-НЕ, выход которого соединен с информационным входом третьего триггера, тактовый вход декодера соединен с тактовыми входами второго, третьего и четвертого триггеров и тактовым входом счетчика, который является синхронным и содержит прямой вход разрешения счета, инверсный вход разрешения записи, являющийся приоритетным относительно входа разрешения счета, доминирующий асинхронный инверсный вход сброса, кодовый выход и кодовый вход, являющийся кодовым входом порога обнаружения паузы декодера, кодовый вход порога обнаружения синхросигнала кодированного сигнала которого соединен с первым кодовым входом компаратора, второй кодовый вход которого соединен с кодовым выходом счетчика, разрядные выходы которого соединены с входами вторых элементов И-НЕ и ИЛИ, первый выход декодера является выходом синхронизированного сигнала последовательного двоичного кода и соединен с выходом первого триггера, информационный вход второго триггера соединен с выходом второго элемента ИЛИ-НЕ, первый вход которого соединен с входом разрешения записи счетчика, выходом третьего элемента И-НЕ и первым входом второго элемента И, выход которого соединен с информационным входом четвертого триггера, инверсный выход которого соединен с первым входом четвертого элемента И-НЕ, второй вход которого соединен с выходом второго элемента ИЛИ, второй выход декодера является выходом синхросигнала битовой синхронизации и соединен с выходом первого элемента И, третий выход декодера является выходом синхросигнала паузы и соединен с прямым выходом третьего триггера и первым входом третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ, входом разрешения счета счетчика и вторыми входами первого элемента И-НЕ и второго элемента И, третий вход которого соединен с выходом четвертого элемента И-НЕ, вход сброса счетчика соединен с выходом третьего элемента ИЛИ, первый вход которого через элемент задержки связан с прямым выходом четвертого триггера и первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом компаратора, выход первого элемента ИЛИ-НЕ соединен с вторыми входами второго элемента ИЛИ-НЕ и третьего элемента ИЛИ, третий вход которого соединен с выходом третьего элемента ИЛИ-НЕ, являющегося выходом синхросигнала начала паузы и четвертым выходом декодера, в котором входы сброса и установки всех триггеров являются доминирующими асинхронными инверсными, причем неиспользуемые из них соединены с шиной Логической «1» декодера.

Авторам не известны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение четырех триггеров, трех элементов ИЛИ-НЕ, трех элементов ИЛИ, элемента задержки, двух элементов И, двух элементов Исключающее ИЛИ, двухразрядного регистра, компаратора, четырех элементов И-НЕ, входа выбора типа декодируемого трехуровневого кодированного сигнала, кодового входа порога обнаружения паузы и кодового входа порога обнаружения синхросигнала кодированного сигнала), предлагаемого декодера, которые (по сравнению с прототипом [12]) комплексно расширяют функциональные возможности декодера и обеспечивают его помехоустойчивость за счет помехоустойчивого формирования выходного синхронизированного сигнала OZ последовательного двоичного кода и выходных синхросигналов битовой синхронизации OCZ, паузы OPZ и начала паузы ОРС для трехуровневого кода RZ или ВТК с помощью заградительной фильтрации асинхронного кодированного сигнала Z(1:0) как помехи при длительности Ti каждого изменения этого сигнала, не превышающей пороговой длительности P·Tic с учетом (5)-(17) для P≥1.

В настоящее время для приема и преобразования входного электрического трехуровневого кодированного сигнала IZ (4) трехуровневого кода RZ или ВТК можно использовать один из приемников-преобразователей микросхемы 1567АП1 [2, с.80-83], являющейся двухканальным приемником-преобразователем последовательного кода RZ по ГОСТ 18977 (ARING), который предназначен для приема двух дифференциальных цифровых сигналов IZ (4) с разрешаемой коммутацией любого из них на два цифровых выхода с открытым коллектором: выход Z1 - информации и выход Z0 - синхронизации. При использовании микросхемы 1567АП1 выходы ее сигналов Z1 и Z0 необходимо через согласующие резисторы подключить к шине напряжения питания +5В.

Если трехуровневый кодированный сигнал IZ является оптическим, то он сначала преобразуется соответствующим оптическим приемником в подобный электрический одномерный IU, который далее, например, с помощью двух компараторов технического решения [10] преобразуется сначала в сигналы ND1 и ND0, а затем, с помощью элементов НЕ и И-НЕ, в сигналы Z1=D1 и Z0=(D1#D) - см. изложенное ранее описание технического решения [10].

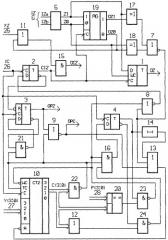

На чертеже приведена электрическая функциональная схема декодера трехуровневого кодированного сигнала, реализованного при условиях (18) и (19) с четырехразрядным счетчиком для входного электрического трехуровневого кодированного сигнала IZ (4) и содержащего триггеры с первого 1 по четвертый 4, приемник-преобразователь 5, разрядные выходы старшего и младшего разрядов кодового выхода которого являются выходами асинхронных сигналов информации и синхронизации соответственно, вход 6 трехуровневого кодированного сигнала, соединенный с входом приемника-преобразователя 5, элементы ИЛИ-НЕ с первого 7 по третий 9, двоичный счетчик 10, элементы ИЛИ с первого 11 по третий 13, элемент задержки 14, первый 15 и второй 16 элементы И, первый 17 и второй 18 элементы Исключающее ИЛИ, двухразрядный регистр 19 с параллельным вводом и выводом информации, компаратор 20, элементы И-НЕ с первого 21 по четвертый 24, четыре выхода, вход 25 выбора типа декодируемого трехуровневого кодированного сигнала, являющийся первым входом первого элемента 11 ИЛИ, тактовый вход 26, кодовый вход 27 порога обнаружения паузы и кодовый вход 28 порога обнаружения синхросигнала кодированного сигнала, причем выход старшего разряда приемника-преобразователя 5 соединен с информационным входом первого триггера 1, первым входом первого элемента 17 Исключающее ИЛИ и входом старшего разряда регистра 19, выход старшего разряда которого соединен с вторым входом первого элемента 17 Исключающее ИЛИ, выход которого соединен с первым входом первого элемента 7 ИЛИ-НЕ, второй вход которого соединен с выходом второго элемента 18 Исключающее ИЛИ, первый вход которого соединен с входом разрешения записи первого триггера 1, выходом младшего разряда приемника-преобразователя 5 и входом младшего разряда регистра 19, выход младшего разряда которого соединен с вторыми входами второго элемента 18 Исключающее ИЛИ и первого элемента 11 ИЛИ, выход которого соединен с первым входом первого элемента 15 И, второй вход которого соединен с тактовыми входами первого триггера 1 и регистра 19 и прямым выходом второго триггера 2, инверсный выход которого соединен с входом сброса третьего триггера 3, инверсный выход которого соединен с первым входом первого элемента 21 И-НЕ, выход которого соединен с информационным входом третьего триггера 3, тактовый вход 26 декодера соединен с тактовыми входами триггеров 2-4 и тактовым входом счетчика 10, который является синхронным и содержит прямой вход разрешения счета, инверсный вход разрешения записи, являющийся приоритетным относительно входа разрешения счета, доминирующий асинхронный инверсный вход сброса, кодовый выход и кодовый вход, являющийся кодовым входом 27 порога обнаружения паузы декодера, кодовый вход 28 порога обнаружения синхросигнала кодированного сигнала которого соединен с первым кодовым входом компаратора 20, второй кодовый вход которого соединен с кодовым выходом счетчика 10, разрядные выходы которого соединены с входами второго элемента 22 И-НЕ и второго элемента 12 ИЛИ, первый выход декодера является выходом синхронизированного сигнала последовательного двоичного кода и соединен с выходом первого триггера 1, информационный вход второго триггера 2 соединен с выходом второго элемента 8 ИЛИ-НЕ, первый вход которого соединен с входом разрешения записи счетчика 10, выходом третьего элемента 23 И-НЕ и первым входом второго элемента 16 И, выход которого соединен с информационным входом четвертого триггера 4, инверсный выход которого соединен с первым входом четвертого элемента 24 И-НЕ, второй вход которого соединен с выходом второго элемента 12 ИЛИ, второй выход декодера является выходом синхросигнала битовой синхронизации и соединен с выходом первого элемента 15 И, третий выход декодера является выходом синхросигнала паузы и соединен с прямым выходом третьего триггера 3 и первым входом третьего элемента 9 ИЛИ-НЕ, второй вход которого соединен с выходом второго элемента 22 И-НЕ, входом разрешения счета счетчика 10 и вторыми входами первого элемента 21 И-НЕ и второго элемента 16 И, третий вход которого соединен с выходом четвертого элемента 24 И-НЕ, вход сброса счетчика 10 соединен с выходом третьего элемента 13 ИЛИ, первый вход которого через элемент задержки 14 связан с прямым выходом четвертого триггера 4 и первым входом третьего элемента 23 И-НЕ, второй вход которого соединен с выходом компаратора 20, выход первого элемента 7 ИЛИ-НЕ соединен с вторыми входами второго элемента 8 ИЛИ-НЕ и третьего элемента 13 ИЛИ, третий вход которого соединен с выходом третьего элемента 9 ИЛИ-НЕ, являющегося выходом синхросигнала начала паузы и четвертым выходом декодера, в котором входы сброса и установки всех триггеров являются доминирующими асинхронными инверсными, причем неиспользуемые из них соединены с шиной Логической «1» декодера, что на чертеже не показано.

Как синхронный автомат с памятью четырехразрядный сче