Вероятностный декодер для dvd

Иллюстрации

Показать всеИзобретение относится к области кодирования, декодирования или преобразования кода и может применяться для исправления ошибок в цифровом битовом потоке, считанном с головки привода DVD. Техническим результатом является упрощение устройства, осуществляющего вероятностную коррекцию ошибок правила RLL (2, 10) в битовом потоке DVD. Устройство содержит последовательный синхронный сдвиговый регистр данных, регистр запрета сдвига, логику управления с цепями обнаружения ошибок, настроенными на поиск ошибок правила RLL (2, 10), и цепями исправления ошибок, логический элемент И. 2 ил., 7 табл.

Реферат

Изобретение относится к области кодирования, декодирования или преобразования кода и может применяться для исправления ошибок в цифровом битовом потоке, считанном с головки привода для цифровых дисков DVD общего назначения.

Работа вероятностных декодеров PRML (Partial Response, Maximum Likehood) основана на принципе максимального правдоподобия и базируется на том, что считанный с канала или диска битовый поток подчиняется определенным правилам, если в потоке встречается нарушение таких правил, то вероятностный декодер исправляет каждую некорректную комбинацию бит на наиболее похожую корректную, т.е. на ту, из которой, скорее всего, образовалась ошибочная комбинация. Вероятностная коррекция не может обеспечить 100% исправления ошибок, однако улучшает поток статистически (уменьшает количество ошибок в нем). Это уменьшает число ошибок на выходе декодера EFM+, который осуществляет окончательное декодирование непрерывного битового потока DVD в байтовые сектора.

Битовый поток, оцифрованный после считывания с головки привода DVD и подвергнутый обратному преобразованию NRZI, подчиняется правилу RLL (2, 10), состоящему в том, что между двумя соседними битами со значением «1» должно быть не менее 2 и не более 10 битов со значением «0» (исключение составляют синхрослова, в которых встречается последовательность из 13 битов со значением «0», считающаяся корректной). Таким образом, если в битовом потоке встречаются комбинации, когда между двумя соседними «1» нет битов «0», либо есть 1, 11, 12, 14 или более 14 бит «0», то такая комбинация является ошибочной и может быть исправлена вероятностными методами.

Удобно для восприятия представлять последовательности битов в виде чисел, соответствующих числу непрерывно идущих битов «0» между битами «1» (например, последовательность битов «10001» удобно обозначить «3», последовательность «10010100000000001» - «2 1 10», последовательность «100110000001» - «2 0 6» и так далее). Ниже применяется подобная система обозначений. В таблице 1 приведены примеры битовых комбинаций.

| Таблица 1 | ||

| Примеры комбинаций в битовом потоке DVD | ||

| Комбинация | Обозначение | Корректность |

| ...00011000... | ...0... | Не корректна |

| ...000101000... | ...1... | Не корректна |

| ...0001001000... | ...2... | Корректна |

| ...00010001000... | ...3... | Корректна |

| ...00010000000001000... | ...9... | Корректна |

| ...000100000000001000... | ...10... | Корректна |

| ...0001000000000001000... | ...11... | Не корректна |

| ...00010000000000001000... | ...12... | Не корректна |

| ...000100000000000001000... | ...13... | Корректна |

| ...0001000000000000001000... | ...14... | Не корректна |

| ...00010000000000000001000... | ...15... | Не корректна |

Также в битовом потоке могут встречаться сочетания таких ошибок. (Сочетанием ошибок считаются такие комбинации, когда две или более ошибочных комбинации следуют непосредственно друг за другом или расположены так, что исправление одной комбинации влияет на корректность соседней). Например, последовательности «...10101...» (обозначение «...1 1...») и «...10100101...» (обозначение «...1 2 1...») считаются сочетанием двух ошибочных последовательностей «101» (ошибок «1»). Сочетания одиночных ошибок называются групповыми ошибками.

Наиболее универсальным алгоритмом исправления ошибок в подобном потоке является модифицированный алгоритм Витерби. Устройства на его основе имеют высокую сложность, однако способны исправить все типы одиночных и групповых ошибок. Из аналогов, реализующих такой алгоритм, известен декодер Витерби для DVD-плеера «Raptor 1b» [1].

Статистические исследования потоков, считанных с реальных приводов DVD трех различных моделей, показывают следующее:

1. Подавляющее большинство ошибок образуются путем сдвига битов «1» вправо или влево относительно своей исходной позиции, при этом число бит в комбинации не изменяется; практически не встречаются ошибки, образующиеся «выпадением» или «добавлением» отдельных битов «0» или «1». Как следствие, под исправлением ошибки подразумевается сдвиг битов «1» таким образом, чтобы число бит комбинации не изменялось, а результирующая комбинация подчинялась правилу RLL (2, 10).

2. Ошибки в битовом потоке носят преимущественно одиночный характер.

3. Подавляющее большинство групповых ошибок сводятся к нескольким основным типам. Исправление остальных ошибок не имеет смысла, поскольку не оказывает значимого влияния на статистическое содержание ошибок в потоке.

Основные типы одиночных и групповых ошибок в потоке (по данным исследований) имеют процентные соотношения, приведенные в таблице 2.

| Таблица 2 | ||||||

| Соотношение основных типов ошибок в битовом потоке DVD для различных типов приводов | ||||||

| Источник сигнала | DVD "Panda" | DVD "Samsung" | DVD "Sanyo" | |||

| Всего бит: | 61281792 | 10523136 | 19189248 | |||

| Тип ошибки | Количество | Процент | Количество | Процент | Количество | Процент |

| 1 | 25314 | 68,773% | 61 | 64,211% | 43 | 89,583% |

| 2 1 | 7735 | 21,014% | 14 | 14,737% | 5 | 10,417% |

| 1 2 | 2065 | 5,610% | 6 | 6,316% | 0,000% | |

| 0 | 1191 | 3,236% | 6 | 6,316% | 0,000% | |

| 2 1 2 | 61 | 0,166% | 0,000% | 0,000% | ||

| 11 | 16 | 0,043% | 0,000% | 0,000% | ||

| 1 11 | 176 | 0,478% | 0,000% | 0,000% | ||

| 11 1 | 28 | 0,076% | 0,000% | 0,000% | ||

| 0 11 | 16 | 0,043% | 1 | 1,053% | 0,000% | |

| 11 0 | 2 | 0,005% | 0,000% | 0,000% | ||

| 1 11 1/0 11 0/0 11 1 | 4 | 0,011% | 0,000% | 0,000% | ||

| 1 1 2/2 1 1 | 9 | 0,024% | 0,000% | 0,000% | ||

| 1 1 | 53 | 0,144% | 0,000% | 0,000% | ||

| 2 0 2/2 0/0 2 | 26 | 0,071% | 0,000% | 0,000% | ||

| Другие ошибки до 11 | 2 | 0,005% | 3 | 3,158% | 0,000% | |

| 12 и 14 | 37 | 0,101% | 3 | 3,158% | 0,000% | |

| Выше 14 | 73 | 0.198% | 1 | 1,053% | 0,000% | |

| Всего ошибок: | 36808 | 95 | 48 | |||

| Плотность ошибок: | 1:1664,904 | 1:110769,853 | 1:399776,000 |

Исправление ошибок «12», «14» и выше вероятностными методами крайне нежелательно, поскольку это затрудняет распознавание синхрослов декодером EFM+.

Из таблицы 2 с учетом природы образования ошибок следует, что практически все ошибки, подлежащие исправлению, можно исправить за три шага - с помощью корректоров ошибок трех основных типов (поэтому такой алгоритм коррекции и декодер на его основе названы «пошаговыми»). При этом порядок шагов подбирается определенным образом, таким, что сначала исправляются ошибки, метод исправления которых наиболее очевиден, а затем те, метод исправления которых менее очевиден (таблица 3).

| Таблица 3 | ||

| Порядок шагов работы пошагового вероятностного декодера | ||

| Ошибка | Метод коррекции | Примеры |

| «0» | Сдвиг двух единиц в противоположные | - 001100 в 010010 |

| стороны друг от друга, причем движение в каждую сторону осуществляется при условии, что рядом с этой стороны находится не менее двух нулей. | - 101100 в 101010- 101101 не корректируется | |

| «1» и «2 1 2» | Сдвиг одной из единиц или одной из комбинаций бит «1001», образующих ошибку, в сторону от противоположной при условии, что рядом в направлении | Для приоритетного направления сдвига к более поздним значениям: |

| сдвига содержится от 3 до 11 нулей. Если это условие соблюдается для обеих | - 000101000 в 000100100 | |

| сторон, то сдвиг производится в задаваемом приоритетном направлении. | - 000101001 в 001001001 | |

| Могут быть также задействованы дополнительные параметры коррекции: | - 100101001 не корректируется | |

| - Если с одной из сторон находится «11», то сдвиг производить к ней; | - 000100101001000 в 000100100100100 | |

| - Всегда сдвигать единицы в задаваемом приоритетном направлении, даже если сдвигать приходится «1001», а в противоположном приоритетному направлении - только одна единица | - 000100101001001 в 001001001001001- 100100101001001 не корректируется | |

| «11» | Сдвиг одной из единиц, образующих ошибку, в сторону к противоположной при условии, что рядом со сдвигаемой единицей в направлении, противоположном сдвигу, содержится не более 9 нулей. Если это условие соблюдается для обеих сторон, то сдвиг производится в задаваемом приоритетном направлении. | Для приоритетного направления сдвига к более поздним значениям:- 1000000000001 в 0100000000001 |

Такой подход позволяет корректировать достаточно сложные на первый взгляд комбинации. Например, ошибка «5 2 0 2 5» исправляется сначала в «5 1 2 1 5» узлом коррекции «0», а затем в «4 2 2 2 4» узлом коррекции «1», что, по всей видимости, является наиболее корректным вариантом исправления данной ошибки.

Приоритетное направление коррекции ошибок выбирается, исходя из свойств аналогового канала чтения информации с диска. Например, для DVD «Panda» установлено, что образование ошибок сдвигом единицы к более ранним значениям происходит в несколько раз чаще, чем к более поздним. Поэтому для аналогичных систем в качестве приоритетного направления сдвига при исправлении ошибок должен задаваться сдвиг единиц к более поздним значениям. Далее сдвиг единиц к более ранним значениям называется «сдвигом вправо», а сдвиг единиц к более поздним значениям - сдвигом влево.

Коррекция ошибок «2 1 2» и «11» должна иметь возможность отключаться, так как экспериментально обнаружено, что иногда коррекция этих ошибок приводит к статистическому ухудшению потока.

Недостатками аналога-прототипа [1] на основе модифицированного алгоритма Витерби являются сложность, отсутствие гибкости в программировании параметров декодирования, а также невозможность учесть природу и метод возникновения каждой конкретной ошибки. На основании приведенной статистики и ввиду перечисленных недостатков можно заключить, что применение для коррекции ошибок битового потока DVD-устройств, основанных на модифицированном алгоритме Витерби, не оправдано.

Сущность изобретения заключается в следующем. Задачей заявляемого изобретения является упрощение устройства, осуществляющего вероятностную коррекцию ошибок правила RLL (2, 10) в битовом потоке DVD. При этом объектом обнаружения и коррекции являются ошибки трех типов: «0», «1»/«2 1 2» и «11».

Поставленная задача решается следующим образом.

В вероятностный декодер для DVD, содержащий шину входных и шину выходных данных, введены последовательный синхронный сдвиговый регистр данных фиксированной длины и логика управления с цепями обнаружения ошибок и с цепями исправления ошибок, причем вход регистра данных подключен к шине входных данных, выход регистра данных подключен к шине выходных данных, а цепи обнаружения ошибок выполнены настроенными на поиск ошибок правила RLL (2, 10), по крайней мере, двух основных типов из фиксированного набора по значению регистра данных, при этом регистр данных содержит элементы синхронного сдвига единиц по сигналам коррекции ошибок, формируемым логикой управления.

Рассмотрим реализацию устройства для случая с корректорами трех приведенных выше типов ошибок: «0», «1»/«2 1 2» и «11».

Корректор каждого из трех типов ошибок содержит последовательный синхронный сдвиговый регистр фиксированной длины, вход которого подключается к источнику данных, могущих содержать ошибки соответствующего типа, а выход регистра подключен к приемнику скорректированных данных. Значения битов сдвигового регистра подключены к логике управления корректором, которая включает в себя цепи детектирования ошибки и возможностей ее исправления и цепи формирования сигналов коррекции ошибки. Сдвиговый регистр оснащен элементами синхронного сдвига единиц по сигналам коррекции ошибок, формируемыми логикой управления.

Для упрощения структуры всего устройства и уменьшения создаваемой им временной задержки все три регистра корректоров объединены в один регистр, называемый регистром данных, причем неизменяемые части регистров корректоров совмещены друг с другом. Корректоры расположены в регистре данных в следующем порядке: «0»; «1»/«2 1 2»; «11». Таким образом, каждый фрагмент сигнала последовательно проверяется и корректируется каждым из этих корректоров. Суммарная длина регистра данных составляет 58 бит, а его биты пронумерованы как d0÷d57. Ко входу регистра данных (биту d0) подключена шина входных данных устройства; выход изменяемой части последнего корректора (бит d48) - к шине выходных данных устройства.

Пошаговый вероятностный декодер имеет шесть управляющих сигналов (таблица 4).

| Таблица 4 | |

| Управляющие сигналы пошагового вероятностного декодера | |

| Сигнал | Воздействие на декодер |

| CORR_EN | 1 - общая коррекция ошибок разрешена0 - коррекция всех ошибок запрещена |

| PR_LEFT | 1 - приоритет имеет сдвиг битов к более поздним значениям0 - приоритет имеет сдвиг битов к более ранним значениям |

| PR_1TO11 | 1 - если с одной из сторон ошибок «1» или «2 1 2» стоит ошибка «11», то сдвиг битов ошибки производится в сторону ошибки «11» независимо от значения PR_LEFT (при сигнале PR_21TOPR=1 в сторону ошибки «11» сдвигаются любые из комбинаций «1», «2 1» и «1 2»)0 - сдвиг битов ошибок «1» и «2 1 2» всегда производится в направлении, выбранном сигналом PR_LEFT |

| CORR_212 | 1 - коррекция ошибок «2 1 2» разрешена0 - коррекция ошибок «2 1 2» запрещена |

| PR_21TOPR | 1 - ошибки «1 2» и «2 1» исправляются сдвигом в направлении, выбранном сигналом PR_LEFT0 - ошибки «1 2» и «2 1» исправляются сдвигом «1» от «2»Замечание: сигнал действителен только при высоком уровне сигнала CORR_212, иначе считается равным нулю |

| CORR_11 | 1 - коррекция ошибок «11» разрешена0 - коррекция ошибок «11» запрещена |

Для взаимосвязи работы трех корректоров путем передачи информации о достоверности исправления ошибок в схему введен синхронный сдвиговый регистр, называемый регистром запрета сдвига. Биты регистра запрета сдвига пронумерованы как n0÷n57, а к его входу (биту n0) подключено значение «0». Регистр запрета сдвига оснащен элементами установки битов n1 и n4 в значении «1» по сигналам логики управления корректором ошибки «0» (единственной ошибки, исправляемой достоверно). Регистр данных и регистр запрета сдвига подключены к общему сигналу синхронного сдвига их значений. Значение «1» в каком-либо бите регистра запрета сдвига может появляться только в случае, когда соответствующий бит регистра данных также содержит значение «1», и указывает на то, что соответствующий бит со значением «1» в регистре данных является достоверным и не может более изменяться (сдвигаться как ошибочный) логикой управления.

Логика управления корректорами построена в соответствии с изложенными выше предпосылками, в частности таблицей 3, и имеет двухуровневую структуру. На первом уровне находятся цепи формирования сигналов детектирования ошибок (DET_0, DET_1, DET_11) и сигналов возможности их исправления (CAN_0L, CAN_0R, CAN_1L, CAN_1R, CAN_1L11, CAN_1R11, CAN_12L, CAN_12R, CAN_1L211, CAN_1R211, CAN_11L, CAN_11R) по значениям битов регистра данных d0÷d57, регистра запрета сдвига n0÷n57, сигналов управления декодером PR_1TO11, CORR_212 и CORR_11, а также некоторых сигналов коррекции ошибок предыдущих корректоров (C1, C5). Назначение и метод формирования сигналов первого уровня сведены в таблицу 5. На втором уровне логики управления находятся цепи формирования сигналов коррекции ошибок С0÷С7 по значениям сигналов, сформированных на первом уровне логики управления, а также сигналов управления декодером PR_LEFT и PR_21TOPR. Назначение и метод формирования сигналов второго уровня сведены в таблицу 6.

| Таблица 5 | |||

| Назначение и метод формирования сигналов первого уровня логики управления пошаговым вероятностным декодером | |||

| Тип ошибки | Сигнал | Формула расчета значения сигнала | Логический смысл сигнала |

| «0» | DET_0 | (d2=1) и (d3=1) | Обнаружена ошибка «0» (в d2, d3) |

| CAN_0L | (d0=0) и (d1=0) | Есть возможность исправления ошибки «0» влево | |

| CAN_0R | (d4=0) и (d5=0) | Есть возможность исправления ошибки «0» вправо | |

| «1» и «2 1 2» | DET_1 | (d19=1) и (d21=1) и (d20=0) | Обнаружена ошибка «1» (в d19÷d21) |

| CAN_1L | (d16÷d18=0) и (d7÷d15<>0) и (n19=0) | Есть возможность исправления ошибки «1» влево | |

| CAN_1R | (d22÷d24=0)и (d25÷d33<>0) и (n21=0) | Есть возможность исправления ошибки «1» вправо | |

| CAN_1L11 | PR_1TO11 и (d8÷d18=0) и (d7=1) | Слева от ошибки «1» обнаружена ошибка «11» и ее исправление возможно | |

| CAN_1R11 | PR_1TO11 и (d22÷d32=0) и (d33=1) | Справа от ошибки «1» обнаружена ошибка «11» и ее исправление возможно | |

| CAN_12L | CORR_212 и (d17÷d18=0) и (d16=1) и (d13÷d15=0) и ((d4÷d12<>0) или (C1=1)) и (n19=0) и (n16=0) | Слева от ошибки «1» обнаружена комбинация «2» и есть возможность исправления ошибки «1 2» влево | |

| CAN_12R | CORR_212 и (d22÷d23=0) и (d24=1) и (d25÷d27=0) и (d28÷d36<>0) и (n21=0) и (n24=0) | Справа от ошибки «1» обнаружена комбинация «2» и есть возможность исправления ошибки «2 1» вправо | |

| CAN_1L211 | PR_1TO11 и (d5÷d15=0) и ((d4=1) или (С1=1)) | Слева от ошибки «1 2» обнаружена ошибка «11» и ее исправление возможно | |

| CAN_1R211 | PR_1TO11 и (d25÷35=0) и (d36=1) | Справа от ошибки «2 1» обнаружена ошибка «11» и ее исправление возможно | |

| «11» | DET_11 | (d35=1) и (d47=1) и (d36÷d46=0) | Обнаружена ошибка «11» (в d35÷d47) |

| CAN_11L | CORR_11 и (n47=0) и (d48÷d57<>0) | Есть возможность исправления ошибки «11» влево | |

| CAN_11R | CORR_11 и (n35=0) и ((d25÷d34<>0) или С5) | Есть возможность исправления ошибки «11» вправо |

Под равенством диапазона бит нулю (например, «d16÷d18=0») подразумевается равенство нулю каждого из его битов, а под неравенством (например, «d7÷d15<>0») - неравенство нулю хотя бы одного из его битов.

| Таблица 6 | |||

| Назначение и метод формирования сигналов второго уровня логики управления пошаговым вероятностным декодером | |||

| Тип ошибки | Сигнал | Вызывает сдвиг единиц... | Формула расчета значения сигнала |

| «0» | С0 | Из d2 в d1 | DET_0 и CAN_0L |

| С1 | Из d3 в d4 | DET_0 и CAN_0R | |

| «1» и «2 1 2» | С2 | Из d16 в d15; Из d19 в d18 | DET_1 и CAN_12L и не ((CAN_12R и ((не PR_LEFT и (не CAN_1L211 или CAN_1R211))или (PR_LEFT и (не CAN_1L211 и CAN_1R211)))) или (CAN_1R и (не PR_21TOPR или ((не PR_LEFT и (не CAN_1L211 или CAN_1R11)) или (PR_LEFT и (не CAN_1L211 и CAN_1R11)))))) |

| С3 | Из d19 в d18 | DET_1 и CAN_1L и не ((CAN_1R и ((не PR_LEFT и (не CAN_1L11 или CAN_1R11)) или (PR_LEFT и (не CAN_1L11 и CAN_1R11)))) или (CAN_12R и PR_21TOPR и ((не PR_LEFT и (не CAN_1L11 или CAN_1R211))или(PR_LEFT и (не CAN_1L11 и CAN_1R211))))) | |

| «1» и «2 1 2» | С4 | Из d21 в d22 | DET_1 и CAN_1R и не ((CAN_1L и ((PR_LEFT и (не CAN_1R11 или CAN_1LI1)) или (не PR_LEFT и (не CAN_1R11 и CAN_1L11)))) или (CAN_12L и PR_21TOPR и ((PR_LEFT и (не CAN_1R11 или CAN_1L211))или (не PR_LEFT и (не CAN_1R11 и CAN_1L211))))) |

| С5 | Из 24 в 25; из 21 в 22 | DET_1 и CAN_12R и не ((CAN_12L и ((PR_LEFT и (не CAN_1R211 или CAN_1L211)) или (не PR_LEFT и (не CAN_1R211 и CAN_1L211)))) или (CAN_1L и (не PR_21TOPR или ((PR_LEFT и (не CAN_1R211 или CAN_1LI1)) или (не PR_LEFT и (не CAN_1R211 и CAN_1L11)))))) | |

| «11» | С6 | Из d35 в d36 | DET_11 и CAN_11R и (не PR_LEFT или не CAN_11L) |

| С7 | Из d47 в d46 | DET_11 и CAN_11L и (PR_LEFT или не CAN_11R) |

Каждый из сигналов С0÷С7 через узел умножения (логическим «И») с сигналом CORR_EN подключен к соответствующему элементу синхронного сдвига единиц регистра данных. Также сигналы С0 и С1 через узел умножения с сигналом CORR_EN подключены соответственно к элементам установки в значение «1» битов n1 и n4 регистра запрета сдвига.

Сущность технического решения поясняется графическими материалами, описанием и примерами конкретного исполнения.

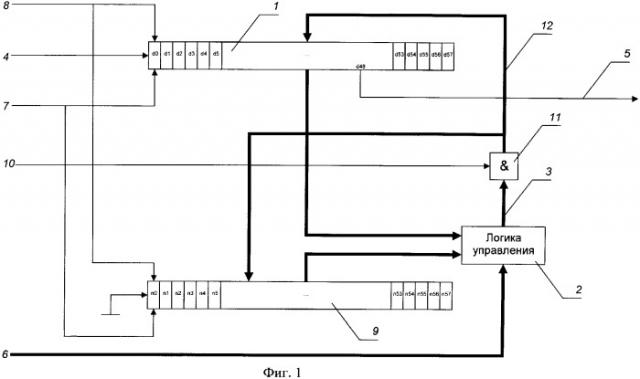

На фиг.1 изображена структурная схема вероятностного декодера для DVD. Символом «&» обозначен элемент поразрядное логическое «И».

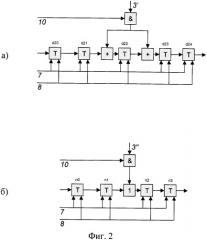

На фиг.2 изображена детализированная схема элементов: а) синхронного сдвига единиц регистра данных на примере сдвига единицы из d21 в d22 по сигналу С4; б) установки в значение «1» битов регистра запрета сдвига на примере установки бита n1 по сигналу С0. Символом «&» обозначен элемент логическое «И»; символом «+» - элемент исключающее «ИЛИ»; символом «1» - элемент логическое «ИЛИ»; символом «Т»-триггер.

На чертежах приняты следующие обозначения:

7 - регистр данных;

2 - логика управления;

3 - сигналы коррекции ошибок (С0÷С7);

3'- сигнал коррекции С4;

3'' - сигнал коррекции С0;

4 - шина входных данных;

5 - шина выходных данных;

6 - сигналы управления режимами декодирования PR_LEFT, PR_1TO11, CORR_212, PR_21TOPR, CORR_11;

7 - входной тактовый сигнал;

8 - сигнал сброса;

9 - регистр запрета сдвига;

10 - сигнал разрешения коррекции CORR_EN;

11 - элемент для поразрядного умножения (логическим «И») сигналов коррекции ошибок 3 и сигнала разрешения коррекции 10;

12 - сигналы коррекции ошибок 3 после поразрядного умножения (логическим «И») с сигналом разрешения коррекции 10.

Пошаговый вероятностный декодер для DVD содержит регистр данных 7, состоящий из битов d0÷d57, причем ко входу бита d0 подключена шина входных данных 4, ко входу бита d1 - выход бита d0, ко входу бита d2 - выход бита d1 (и так далее), ко входу бита d57 - выход бита d56, а шина выходных данных 5 подключена к выходу бита d48; регистр запрета сдвига 9, состоящий из битов n0÷n57, причем ко входу бита n0 подключено значение «0», ко входу бита n1 - выход бита n0, ко входу бита n2 - выход бита n1 (и так далее), ко входу бита n57 - выход бита n56; асинхронную логику управления 2; асинхронный элемент 77 для поразрядного умножения сигналов коррекции ошибок 3 и сигнала разрешения коррекции 10.

Функционирование предлагаемого устройства происходит следующим образом. Все триггеры устройства (биты d0÷d57 и n0÷n57) работают синхронно по положительному фронту входного тактового сигнала 7 и асинхронно сбрасываются в значение «0» высоким уровнем сигнала сброса 8. Таким образом, при низком уровне сигнала сброса 8 по положительному фронту входного тактового сигнала 7 производится сдвиг регистра данных 7 и регистра запрета сдвига 9, при этом в бит d0 записывается очередной бит данных с шины входных данных 4, а в бит n0 записывается значение «0».

Также по положительному фронту тактового сигнала 7 приемником данных с шины выходных данных 5 декодера должно фиксироваться значение очередного бита данных.

Так как вся логика управления 2 и элемент поразрядного умножения 11 асинхронные, то свои выходные значения (сигналы 3 и 12 соответственно) они изменяют через короткое время после сдвига регистра данных 1 и регистра запрета сдвига 9. При этом сигналы коррекции ошибок 3 и 12 сформированы в соответствии с таблицами 5 и 6 для текущей комбинаций данных регистра данных 7, текущих значений регистра запрета сдвига 9 и текущих значений сигналов управления 6. При следующем сдвиге регистров 7 и 9 по положительному фронту тактового сигнала 7 также производится коррекция ошибок (сдвиг единиц) и установка в значение «1» битов n1 и n4 в соответствии с сигналами 12 (при условии, что сигнал разрешения коррекции 10 имеет высокий уровень).

Значения входных сигналов управления 6, задающих режимы декодирования, должны подбираться исходя из свойств аналогового канала чтения информации с диска таким образом, чтобы статистический уровень ошибок на выходе декодера был минимальным.

Сигнал разрешения коррекции 10 позволяет отключить коррекцию ошибок декодером в случаях, когда это необходимо, однако для нормальной работы декодера он должен удерживаться в высоком уровне.

Сигнал сброса 8 предназначен для очистки регистра данных 7 и регистра запрета сдвига 9, что исключает появление «мусора» на выходе декодера в начале работы. Сброс декодера осуществляется высоким уровнем сигнала 8, однако он не является обязательным, а для нормальной работы декодера сигнал 8 должен удерживаться в низком уровне.

Технический эффект от использования предлагаемого устройства заключается в статистическом уменьшении числа ошибок правила RLL (2, 10) в битовом потоке DVD, что уменьшает число ошибок на выходе декодера EFM+ и, как следствие, существенно повышает эффективность и снижает время работы декодера ЕСС, корректирующего ошибки в байтовых секторах, выдаваемых декодером EFM+.

Для DVD-плееров, рассмотренных в таблице 2, после работы вероятностного декодера суммарная плотность ошибок ЕСС уменьшается соответственно в 2,52, 1,59 и 3,1 раза. Также после работы вероятностного декодера увеличилось число синхрослов, корректно распознанных декодером EFM+.

При этом для DVD-плеера «Panda» число ошибок правила RLL (2, 10) в битовом потоке до декодера составляла 1:1664,904, а после декодера - 1:453939,2. Таким образом, число указанных ошибок уменьшается ориентировочно в 273 раза. (Для DVD-плееров «Samsung» и «Sanyo» эта цифра составляет 13,571 раза и бесконечность соответственно, однако ввиду малой плотности ошибок RLL в потоках этих плееров эти цифры статистически не столь значимы.)

Согласно описанию DVD-плеера «Raptor 1b» [1] декодер Витерби способен уменьшить суммарную плотность ошибок RLL от 1:1000 до 1:100000, т.е. в 100 раз. В случае работы пошагового вероятностного декодера на сигнале с DVD-плеера «Panda» этот показатель улучшен почти втрое.

Основные типы ошибок в потоках, рассмотренных в таблице 2, после работы пошагового вероятностного декодера имеют процентные соотношения, приведенные в таблице 7.

| Таблица 7 | ||||||

| Соотношение основных типов ошибок в битовом потоке DVD для различных типов приводов после работы вероятностного декодера | ||||||

| Источник сигнала | DVD "Panda" | DVD "Samsung" | DVD "Sanyo" | |||

| Тип ошибки | Количество | Процент | Количество | Процент | Количество | Процент |

| 1 | 10 | 7,407% | 0,000% | Нет ошибок | ||

| 2 1 | 0,000% | 0,000% | ||||

| 1 2 | 2 | 1,481% | 0,000% | |||

| 0 | 0,000% | 0,000% | ||||

| 21 2 | 2 | 1,481% | 0,000% | |||

| 11 | 0,000% | 0,000% | ||||

| 1 11 | 0,000% | 0,000% | ||||

| 11 1 | 0,000% | 0,000% | ||||

| 0 11 | 0,000% | 0,000% | ||||

| 11 0 | 0,000% | 0,000% | ||||

| 1 11 1/0 11 0/0 11 1 | 0,000% | 0,000% | ||||

| 1 1 2/2 1 1 | 0,000% | 0,000% | ||||

| 1 1 | 0,000% | 0,000% | ||||

| 2 0 2/2 0/0 2 | 0,000% | 1 | 14,286% | |||

| Другие ошибки до 11 | 8 | 5,926% | 2 | 28,571% | ||

| 12 и 14 | 38 | 28,148% | 3 | 42,857% | ||

| Выше 14 | 75 | 55,556% | 1 | 14,286% | ||

| Всего ошибок: | 135 | 7 | 0 | |||

| Всего бит: | 61281792 | 10523136 | 19189248 | |||

| Плотность ошибок: | 1:453939,200 | 1:1503305,143 | 1: - |

Источники информации

1. Raptor 1b: User's manual. Part II [Электронный ресурс]. - Infineon Technologies AG, 2001. - P.3-40, 3-41, 3-48, 3-76, 3-77, 3-108-3-111.

Вероятностный декодер для DVD, содержащий шину входных данных и шину выходных данных, отличающийся тем, что в него введены последовательный синхронный сдвиговый регистр данных фиксированной длины, вход которого подключен к шине входных данных, а выход - к шине выходных данных, регистр запрета сдвига, вход которого подключен к нулевой шине, логика управления с цепями обнаружения ошибок и цепями исправления ошибок, причем цепи обнаружения ошибок выполнены настроенными на поиск ошибок правила RLL (2, 10), по крайней мере, двух основных типов из фиксированного набора по значению регистра данных, при этом сигналы коррекции ошибок С0÷С7 формируются логикой управления на основании текущей комбинации данных регистра данных, текущих значений регистра запрета сдвига и текущих значений сигналов управления режимами декодирования, выход логики управления соединен с входом логического элемента И, осуществляющего поразрядное умножение с сигналом разрешения коррекции, с выхода элемента И сигналы коррекции С0÷С7 поступают на соответствующий элемент синхронного сдвига единиц регистра данных, а сигналы коррекции С0 и С1, исправляющие ошибку "0" - к соответствующим битам регистра запрета сдвига.