Управляемый источник опорного тока

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве функционального узла различных устройств усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Управляемый источник опорного тока содержит первый (1) входной и первый (2) выходной транзисторы с объединенными базами, эмиттеры которых соединены с шиной (3) источника питания через соответствующие первый (4) и второй (5) вспомогательные резисторы, дифференциальный усилитель (6), имеющий потенциальный (7) и токовый (8) входы, а также основной токовый выход (9), согласованный с шиной (3) источника питания, причем потенциальный вход (7) дифференциального усилителя (6) соединен с коллектором первого (1) входного транзистора и основным входом (10) управляемого источника опорного тока, токовый вход (8) дифференциального усилителя (6) подключен к базам первого (1) входного и первого (2) выходного транзисторов, коллектор первого (2) выходного транзистора связан с выходом (11) управляемого источника опорного тока. Основной токовый выход (9) дифференциального усилителя (6) соединен с эмиттером выходного транзистора (2). Технический результат - увеличение выходного сопротивления. 1 з.п. ф-лы, 13 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве функционального узла различных устройств усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах).

Основой большинства современных операционных усилителей, стабилизаторов напряжения, компараторов являются так называемые «токовые зеркала» (повторители тока), которые по существу являются управляемыми источниками опорного тока [1-56]. В патентной литературе эти устройства с одним и тем же функциональным назначением присутствуют в классе H03F, а также классах G05F, Н03К МПК. Качественные показатели многих аналоговых устройств определяются динамическими параметрами токовых зеркал. Именно этим объясняется большое число патентов, посвященных данному подклассу функциональных узлов [1-56].

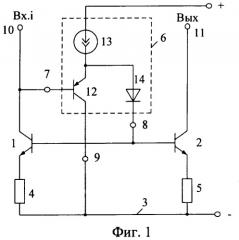

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте фирмы Analog Devices (США) №6.573.795, фиг.2-5, содержащий первый 1 входной и первый 2 выходной транзисторы с объединенными базами, эмиттеры которых соединены с шиной 3 источника питания через соответствующие первый 4 и второй 5 вспомогательные резисторы, дифференциальный усилитель 6, имеющий потенциальный 7 и токовый 8 входы, а также основной токовый выход 9, согласованный с шиной 3 источника питания, причем потенциальный вход 7 дифференциального усилителя 6 соединен с коллектором первого 1 входного транзистора и основным входом 10 управляемого источника опорного тока, токовый вход 8 дифференциального усилителя 6 подключен к базам первого 1 входного и первого 2 выходного транзисторов, коллектор первого 2 выходного транзистора связан с выходом 11 управляемого источника опорного тока.

Существенный недостаток известного ДУ состоит в том, что он имеет недостаточно высокое выходное сопротивление, что ограничивает предельный коэффициент усиления по напряжению входных каскадов ОУ и стабилизаторов напряжения.

Основная цель предлагаемого изобретения состоит в увеличении в 8÷15 раз выходного сопротивления рассматриваемого функционального узла.

Поставленная цель достигается тем, что в управляемом источнике опорного тока (фиг.1), содержащем первый 1 входной и первый 2 выходной транзисторы с объединенными базами, эмиттеры которых соединены с шиной 3 источника питания через соответствующие первый 4 и второй 5 вспомогательные резисторы, дифференциальный усилитель 6, имеющий потенциальный 7 и токовый 8 входы, а также основной токовый выход 9, согласованный с шиной 3 источника питания, причем потенциальный вход 7 дифференциального усилителя 6 соединен с коллектором первого 1 входного транзистора и основным входом 10 управляемого источника опорного тока, токовый вход 8 дифференциального усилителя 6 подключен к базам первого 1 входного и первого 2 выходного транзисторов, коллектор первого 2 выходного транзистора связан с выходом 11 управляемого источника опорного тока, предусмотрены новые элементы и связи - основной токовый выход 9 дифференциального усилителя 6 соединен с эмиттером выходного транзистора 2.

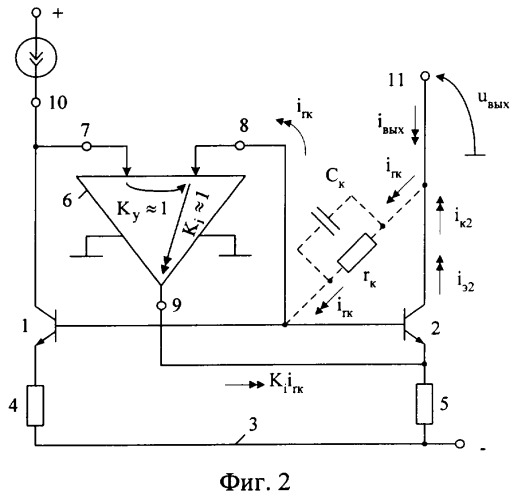

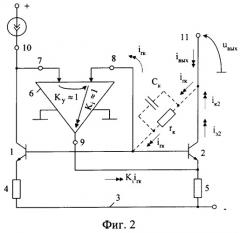

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

На фиг.3 показана УИТ фиг.2 с частным вариантом построения дифференциального усилителя 6.

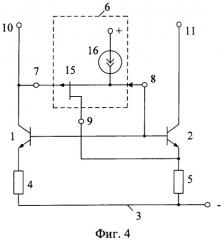

На фиг.4 изображен вариант построения дифференциального усилителя тока 6 в соответствии с п.2 формулы изобретения.

Схема фиг.5 иллюстрирует применение заявляемого УИТ в структуре входного каскада операционного усилителя (ОУ).

На фиг.6 и 7 показаны схемы заявляемого (фиг.6) и известного (фиг.7) устройств в среде компьютерного моделирования PSpice, а на фиг.8 - частотная зависимость их выходного сопротивления.

Схемы ОУ на основе заявляемого УИТ фиг.9, 10 и 11 в среде PSpice и результаты их компьютерного моделирования - зависимость коэффициента усиления по напряжению от частоты - показаны на фиг.12 и 13.

Управляемый источник опорного тока фиг.2 (п.1 формулы изобретения) содержит первый 1 входной и первый 2 выходной транзисторы с объединенными базами, эмиттеры которых соединены с шиной 3 источника питания через соответствующие первый 4 и второй 5 вспомогательные резисторы, дифференциальный усилитель 6, имеющий потенциальный 7 и токовый 8 входы, а также основной токовый выход 9, согласованный с шиной 3 источника питания, причем потенциальный вход 7 дифференциального усилителя 6 соединен с коллектором первого 1 входного транзистора и основным входом 10 управляемого источника опорного тока, токовый вход 8 дифференциального усилителя 6 подключен к базам первого 1 входного и первого 2 выходного транзисторов, коллектор первого 2 выходного транзистора связан с выходом 11 управляемого источника опорного тока. Основной токовый выход 9 дифференциального усилителя (6) соединен с эмиттером выходного транзистора 2.

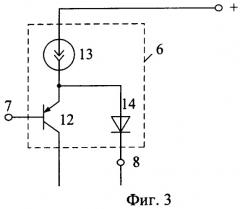

В соответствии с п.2 формулы изобретения (фиг.3) дифференциальный усилитель 6 содержит второй 12 входной транзистор, первый дополнительный источник опорного тока 13 и первый дополнительный p-n переход 14, причем база второго входного транзистора 12 соединена с потенциальным входом 7 дифференциального усилителя 6, эмиттер подключен к первому дополнительному источнику опорного тока 13 и через первый дополнительный p-n переход 14 связан с токовым входом 8 дифференциального усилителя 6.

В частном случае (фиг.4) дифференциальный усилитель 6 выполнен на основе полевого транзистора 15 и источника тока 16.

В схеме фиг.5 роль источника тока 13 и источника входного тока УИТ выполняет дифференциальный каскад 17 на транзисторах 18, 19 и токостабилизирующем двухполюснике 20.

Рассмотрим работу заявляемого ДУ (фиг.2).

При изменении выходного напряжения uвых и достаточно высокоомном резисторе 5 приращения тока через закрытый коллекторный переход транзистора 2 на низких частотах определяются формулой

irк≈укuвых,

где - сопротивление закрытого коллекторного перехода транзистора 2.

Ток irк поступает на токовый вход 8 дифференциального усилителя 6. Поэтому его выходной ток

где Ki≈1 - коэффициент передачи по току дифференциального каскада со входа 8 на выход 9.

Если сопротивление эмиттерного перехода транзистора 2 rэ2<<R5, то его коллекторный ток

где α2≈1 - коэффициент усиления по току эмиттера транзистора 2.

Таким образом, выходной ток УИТ (фиг.2) и его выходная проводимость

где Тi=α2Ki≈1.

Из формулы (4) следует, что в заявляемом устройстве выходное сопротивление (в сравнении с прототипом) увеличивается в N-раз, где

Данные теоретические выводы подтверждаются результатами моделирования схем фиг.6 и 7. Как следствие, коэффициент усиления по напряжению ОУ фиг.10, 11 на основе заявляемого УИТ также повышается (фиг.12, 13).

Таким образом, заявляемый УИТ имеет более высокое значение одного из важнейших параметров - выходного сопротивления.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент РФ №1.329.639.

2. Патент США №3.681.623.

3. Патент США №3.813.607.

4. Патент США №3.835.410.

5. Патент США №4.008.441, H03F 3/16.

6. Патент США №4.013.973.

7. Патент США №4.030.044 (фиг.3).

8. Патент США №4.057.763.

9. Патент США №4.095.189.

10. Патент США №4.117.417.

11. Патент США №4.241.315.

12. Патент США №4.345.213.

13. Патент США №4.412.186, H03f 3/04.

14. Патент США №4.462.005, H03f 3/04.

15. Патент США №4.471.236.

16. Патент США №4.473.794.

17. Патент США №4.567.444.

18. Патент США №4.591.804, H03f 3/04.

19. Патент США №4.769.619.

20. Патент США №4.855.686.

21. Патент США №4.879.524, H03f 3/26.

22. Патент США №4.897.614.

23. Патент США №4.937.515, G05f 3/26.

24. Патент США №4.990.864.

25. Патент США №5.053.718.

26. Патент США №5.079.518, Н03K 3/16.

27. Патент США №5.164.658.

28. Патент США №5.357.188, G05f 3/26.

29. Патент США №5.373.253.

30. Патент США №5.394.079, G05f 3/16.

31. Патент США №5.399.991.

32. Патент США №5.512.815, G05f 3/16.

33. Патент США №5.572.114.

34. Патент США №5.633.612.

35. Патент США №5.721.512.

36. Патент США №5.933.055.

37. Патент США №5.969.574.

38. Патент США №5.986.507.

39. Патент США №6.016.050.

40. Патент США №6.570.438.

41. Патент США №6.573.795.

42. Патент США №6.586.918.

43. Патент США №6.606.001.

44. Патент США №6.291.977.

45. Патент США №6.300.803.

46. Патент США №6.528.981.

47. Патент США №6.630.818.

48. Патент США №6.633.198.

49. Патент США №6.639.452.

50. Патент США №6.657.481.

51. Патент США №6.677.807.

52. Патент США №6.680.605.

53. Патент США №6.816.014.

54. Патент РФ RU 2193273.

55. Патентная заявка США 2004/081688.

56. Патентная заявка США 2003/0030492.

1. Управляемый источник опорного тока, содержащий первый (1) входной и первый (2) выходной транзисторы с объединенными базами, эмиттеры которых соединены с шиной (3) источника питания через соответствующие первый (4) и второй (5) вспомогательные резисторы, дифференциальный усилитель (6), имеющий потенциальный (7) и токовый (8) входы, а также основной токовый выход (9), согласованный с шиной (3) источника питания, причем потенциальный вход (7) дифференциального усилителя (6) соединен с коллектором первого (1) входного транзистора и основным входом (10) управляемого источника опорного тока, токовый вход (8) дифференциального усилителя (6) подключен к базам первого (1) входного и первого (2) выходного транзисторов, коллектор первого (2) выходного транзистора связан с выходом (11) управляемого источника опорного тока, отличающийся тем, что основной токовый выход (9) дифференциального усилителя (6) соединен с эмиттером выходного транзистора (2).

2. Устройство по п.1, отличающееся тем, что дифференциальный усилитель (6) содержит второй (12) входной транзистор, первый дополнительный источник опорного тока (13) и первый дополнительный p-n переход (14), причем база второго входного транзистора (12) соединена с потенциальным входом (7) дифференциального усилителя (6), а его эмиттер подключен к первому дополнительному источнику опорного тока (13) и через первый дополнительный p-n переход (14) связан с токовым входом (8) дифференциального усилителя (6).