Двухтактный каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, дифференциальных операционных усилителях (ОУ)). Технический результат заключается в повышении стабильности статического режима двухтактного каскодного дифференциального усилителя (КДУ). КДУ содержит первый (1) и второй (2) входные транзисторы (Т), базы которых связаны с первой (3) и второй (4) цепями установления статического режима, первый (5) и второй (6) токостабилизирующие двухполюсники, соединенные с соответствующими эмиттерами Т (1) и Т (2), а также первым (7) и вторым (8) входами КДУ, первый (9) и второй (10) выходные усилители тока (УТ), основные выходы которых (11) и (12) связаны друг с другом и подключены к выходу (13) КДУ, причем вход (14) УТ (10) связан с коллектором Т (1), а вход (15) УТ (9) связан с коллектором Т (2). Первый УТ (9) и второй УТ (10) снабжены дополнительными выходами (16) и (17), дополнительный выход (16) УТ (9) соединен с эмиттером Т (2) через первый (18) нелинейный делитель тока (НДТ), а дополнительный выход (17) УТ (10) соединен с эмиттером Т (1) через второй НДТ (19). 4 з.п. ф-лы, 10 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, дифференциальных операционных усилителях (ОУ)).

Известны схемы двухтактных каскодных дифференциальных усилителей (КДУ) [1-22]. По такой архитектуре, на модификации которой выдано около 100 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.).

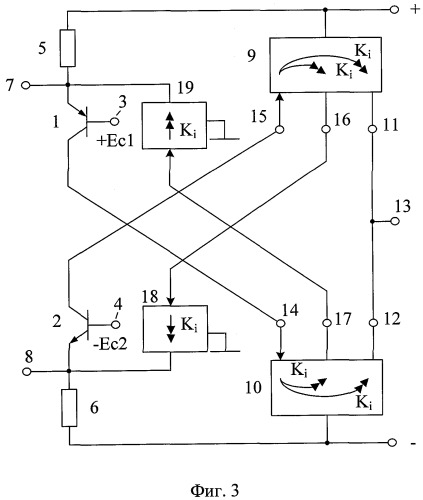

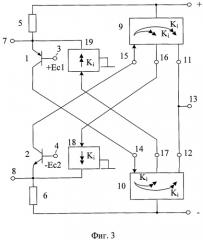

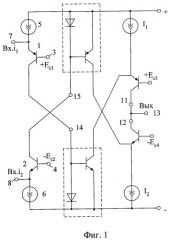

В схеме известного КДУ фиг.1, описанного в статье "On the Common Mode Rejection Ratio in Low Voltage Operational Amplifiers with Complementary N-P Input Pairs" (authors Fan You, Sherif H.K. Embabi and Edgar Sanchez-Sinencio, IEEE Transactions on circuits and systems-II: Analog and Digital signal processing, vol.44, NO.8, August 1997, p.679), обеспечивается высокая стабильность статического режима. Это положительно сказывается на его высокочастотных характеристиках. Однако данный вариант построения КДУ не обеспечивает ток в нагрузке больше, чем статический ток двухполюсников I1 и I2. To есть этот КДУ имеет неудовлетворительные энергетические характеристики. Данный режим характерен для каскадов класса «А». С другой стороны, для получения повышенных значений выходного тока в микроэлектронике применяются КДУ (фиг.2), у которых выходной каскад работает в режиме класса АВ (патент США 5.455.535). Однако для данных устройств характерна проблема обеспечения стабильности статического режима и сквозных токов выходного каскада.

Ближайшим прототипом (фиг.1) заявляемого устройства является двухтактный каскодный дифференциальный усилитель, представленный в структуре схемы по патенту США 5455535, содержащий первый 1 и второй 2 входные транзисторы, базы которых связаны с первой 3 и второй 4 цепями установления статического режима, первый 5 и второй 6 токостабилизирующие двухполюсники, соединенные с соответствующими эмиттерами первого 1 и второго 2 входных транзисторов, а также первым 7 и вторым 8 входами двухтактного каскодного дифференциального усилителя, первый 9 и второй 10 выходные усилители тока, основные выходы которых 11 и 12 связаны друг с другом и подключены к выходу 13 двухтактного каскодного дифференциального усилителя, причем вход 14 второго выходного усилителя тока 10 связан с коллектором первого входного транзистора 1, а вход 15 первого 9 выходного усилителя тока связан с коллектором второго входного транзистора 2.

Существенный недостаток известного КДУ (фиг.1) состоит в том, что он не обеспечивает высокую стабильность статического режима выходного каскада («выходной усилитель тока 12 - второй выходной транзистор 11»), что отрицательно сказывается на его частотных характеристиках, а также работоспособности и токопотреблении при изменениях температуры и разбросе параметров элементов.

Основная цель предлагаемого изобретения состоит в повышении стабильности статического режима КДУ фиг.2 при сохранении на прежнем уровне его главного параметра - относительно высоких значениях максимального выходного тока.

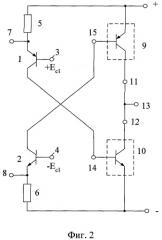

Поставленная цель достигается тем, что в двухтактном каскодном дифференциальном усилителе фиг.2, содержащем первый 1 и второй 2 входные транзисторы, базы которых связаны с первой 3 и второй 4 цепями установления статического режима, первый 5 и второй 6 токостабилизирующие двухполюсники, соединенные с соответствующими эмиттерами первого 1 и второго 2 входных транзисторов, а также первым 7 и вторым 8 входами двухтактного каскодного дифференциального усилителя, первый 9 и второй 10 выходные усилители тока, основные выходы которых 11 и 12 связаны друг с другом и подключены к выходу 13 двухтактного каскодного дифференциального усилителя, причем вход 14 второго выходного усилителя тока 10 связан с коллектором первого входного транзистора 1, а вход 15 первого 9 выходного усилителя тока связан с коллектором второго входного транзистора 2, предусмотрены новые связи - первый 9 и второй 10 выходные усилители тока снабжены дополнительными выходами 16 и 17, дополнительный выход 16 первого 9 выходного усилителя тока соединен с эмиттером второго 2 входного транзистора через первый 18 нелинейный делитель тока, а дополнительный выход 17 второго 10 выходного усилителя тока соединен с эмиттером первого 1 входного транзистора через второй 19 нелинейный делитель тока.

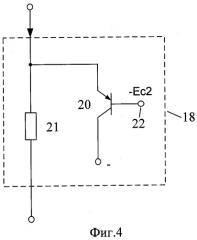

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.3. На фиг.4-5 показаны частные варианты построения нелинейных делителей тока 18 и 19, соответствующие пп.2-3 формулы изобретения.

На фиг.6-7 показаны схемы выходных усилителей тока 9 и 10, соответствующие пп.4-5 формулы изобретения.

На фиг.8 приведена схема заявляемого устройства с конкретным выполнением подсхем 9, 10, 18, 19.

На фиг.9 показана схема заявляемого КДУ (фиг.8), а на фиг.6 - результаты ее компьютерного моделирования в среде PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Двухтактный каскодный дифференциальный усилитель фиг.3 содержит первый 1 и второй 2 входные транзисторы, базы которых связаны с первой 3 и второй 4 цепями установления статического режима, первый 5 и второй 6 токостабилизирующие двухполюсники, соединенные с соответствующими эмиттерами первого 1 и второго 2 входных транзисторов, а также первым 7 и вторым 8 входами двухтактного каскодного дифференциального усилителя, первый 9 и второй 10 выходные усилители тока, основные выходы которых 11 и 12 связаны друг с другом и подключены к выходу 13 двухтактного каскодного дифференциального усилителя, причем вход 14 второго выходного усилителя тока 10 связан с коллектором первого входного транзистора 1, а вход 15 первого 9 выходного усилителя тока связан с коллектором второго входного транзистора 2. Первый 9 и второй 10 выходные усилители тока снабжены дополнительными выходами 16 и 17, дополнительный выход 16 первого 9 выходного усилителя тока соединен с эмиттером второго 2 входного транзистора через первый 18 нелинейный делитель тока, а дополнительный выход 17 второго 10 выходного усилителя тока соединен с эмиттером первого 1 входного транзистора через второй 19 нелинейный делитель тока.

В частном случае фиг.4 (п.2 формулы изобретения) первый 18 нелинейный делитель тока содержит первый 20 вспомогательный транзистор и первый 21 вспомогательный резистор, причем первый вспомогательный резистор 21 включен между входом и выходом первого 18 нелинейного делителя тока, эмиттер первого 20 вспомогательного транзистора подключен ко входу нелинейного делителя тока 18, а его база соединена с первым 22 дополнительным источником напряжения смещения.

В частном случае фиг.5 (п.3 формулы изобретения) второй 19 нелинейный делитель тока содержит второй 23 вспомогательный транзистор и второй 24 вспомогательный резистор, причем второй вспомогательный резистор 24 включен между входом и выходом второго нелинейного делителя тока 19, эмиттер второго 23 вспомогательного транзистора подключен ко входу второго нелинейного делителя тока 19, а его база соединена со вторым 25 дополнительным источником напряжения смещения.

В частном случае фиг.6 (п.4 формулы изобретения) первый 9 выходной усилитель тока содержит первый 26 и второй 27 дополнительные транзисторы, базы которых соединены с первым источником опорного тока 28 и входом 15 первого 9 выходного усилителя тока, коллектор второго дополнительного транзистора 27 соединен с основным 11 выходом первого 9 выходного усилителя тока, а коллектор первого дополнительного транзистора 26 соединен с дополнительным 16 выходом первого 9 выходного усилителя тока.

В частном случае фиг.7 (п.5 формулы изобретения) второй 10 выходной усилитель тока содержит третий 29 и четвертый 30 дополнительные транзисторы, базы которых соединены со вторым источником опорного тока 31 и входом 14 второго 10 выходного усилителя тока, коллектор четвертого дополнительного транзистора 30 соединен с основным 12 выходом второго 10 выходного усилителя тока, а коллектор третьего дополнительного транзистора 29 соединен с дополнительным 17 выходом второго 10 выходного усилителя тока.

Рассмотрим работу заявляемого КДУ с конкретным выполнением подсхем 9, 10, 18 и 19 (фиг.8.).

В статическом режиме за счет выбора сопротивлений резисторов 24 и 21 обеспечивается закрытое состояние транзисторов 20 и 23. Поэтому в схеме фиг.8 в статическом режиме и при малых изменениях входных токов iвх.7 и iвх.8 работает глубокая отрицательная обратная связь по петле «эмиттер транзистора 2 - база транзистора 26, коллектор транзистора 26, резистор 21, эмиттер транзистора 2». Как следствие, коллекторные токи всех транзисторов стабильны и не зависят от разброса их параметров. Величина сквозного тока, протекающего между шинами питания в выходном каскаде, определяется напряжением на базах транзисторов 2 и 20, а также резистором 6. Поэтому практически все приращение входного тока iвх.8 поступает в резистор 21 и по параллельной цепи - на выход усилителя 13

iк26=iвх.8

iн=iк27≈iвх.8

По мере увеличения тока через резистор 21 увеличивается напряжение Uэб.20 на эмиттерно-базовом переходе транзистора 20. Как только это напряжение достигает уровня 0,6÷0,7 В, в активный режим переходит транзистор 20, что обеспечивает выключение обратной связи. В этом режиме приращения входного тока iвх.8 передаются в эмиттер транзистора 2 и далее с помощью транзистора 27 - в нагрузку Rн:

iн.max=iвх.8.maxβ27,

где β27 - коэффициент усиления по току базы транзистора 27;

iвх.8.max - максимальный входной ток КДУ;

iн.max - максимальный выходной ток КДУ.

Таким образом, в заявляемом КДУ обеспечивается большой максимальный выходной ток при высокой стабильности статического режима (фиг.10).

Компьютерное моделирование заявляемого и известного КДУ на моделях интегральных транзисторов ФГУП НПП «Пульсар» подтверждает полученные выше выводы.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент РФ №2193273, H03F 3/45.

2. Патент Японии №53-25232, H03F 3/26, 98(5) А332.

3. Патент US 2001/0052818A1, H03F, 3/45.

4. Патент Японии № JP 8222972.

5. Авт. св. СССР №611288.

6. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - стр.103. Рис.6.11.

7. Патент США №6366170 B1 H03 F/45.

8. Патент США №6268769 H03 F/45.

9. Патент США №3974455 H03 F/45.

10. Патент США №3968451 H03 F/45.

11. Патент США №4837523 H03 F/45.

12. Патент США №5291149 H03 F/45.

13. Патент США №4636743 H03 F/45.

14. Патент США №4783637 H03 F/45.

15. Патент США №5515005 H03 F/45.

16. Патент США №5291149 H03 F/45.

17. Патент США №5140280 H03 F/45.

18. Патент США №5455535 H03 F/45.

19. Патент США №5523718 H03 F/45.

20. Патент США №4600893 H03 F/45.

21. Патент США №5.374.897, фиг.3

22. П.Шкритек. Справочное руководство по звуковой схемотехнике. - М.: Мир, 1991, с.71, рис.5.8.2в.

1. Двухтактный каскодный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, базы которых связаны с первой (3) и второй (4) цепями установления статического режима, первый (5) и второй (6) токостабилизирующие двухполюсники, соединенные с соответствующими эмиттерами первого (1) и второго (2) входных транзисторов, а также первым (7) и вторым (8) входами двухтактного каскодного дифференциального усилителя, первый (9) и второй (10) выходные усилители тока, основные выходы которых (11) и (12) связаны друг с другом и подключены к выходу (13) двухтактного каскодного дифференциального усилителя, причем вход (14) второго выходного усилителя тока (10) связан с коллектором первого входного транзистора (1), а вход (15) первого (9) выходного усилителя тока связан с коллектором второго входного транзистора (2), отличающийся тем, что первый (9) и второй (10) выходные усилители тока снабжены дополнительными выходами (16) и (17), дополнительный выход (16) первого (9) выходного усилителя тока соединен с эмиттером второго (2) входного транзистора через первый (18) нелинейный делитель тока, а дополнительный выход (17) второго (10) выходного усилителя тока соединен с эмиттером первого (1) входного транзистора через второй (19) нелинейный делитель тока.

2. Устройство по п.1, отличающееся тем, что первый (18) нелинейный делитель тока содержит первый (20) вспомогательный транзистор и первый (21) вспомогательный резистор, причем первый вспомогательный резистор (21) включен между входом и выходом первого (18) нелинейного делителя тока, эмиттер первого (20) вспомогательного транзистора подключен ко входу нелинейного делителя тока (18), а его база соединена с первым (22) дополнительным источником напряжения смещения.

3. Устройство по п.1, отличающееся тем, что второй (19) нелинейный делитель тока содержит второй (23) вспомогательный транзистор и второй (24) вспомогательный резистор, причем второй вспомогательный резистор (24) включен между входом и выходом второго нелинейного делителя тока (19), эмиттер второго (23) вспомогательного транзистора подключен ко входу второго нелинейного делителя тока (19), а его база соединена со вторым (25) дополнительным источником напряжения смещения.

4. Устройство по п.1, отличающееся тем, что первый (9) выходной усилитель тока содержит первый (26) и второй (27) дополнительные транзисторы, базы которых соединены с первым источником опорного тока (28) и входом (15) первого (9) выходного усилителя тока, коллектор второго дополнительного транзистора (27) соединен с основным (11) выходом первого (9) выходного усилителя тока, а коллектор первого дополнительного транзистора (26) соединен с дополнительным (16) выходом первого (9) выходного усилителя тока.

5. Устройство по п.1, отличающееся тем, что второй (10) выходной усилитель тока содержит третий (29) и четвертый (30) дополнительные транзисторы, базы которых соединены со вторым источником опорного тока (31) и входом (14) второго (10) выходного усилителя тока, коллектор четвертого дополнительного транзистора (30) соединен с основным (12) выходом второго (10) выходного усилителя тока, а коллектор третьего дополнительного транзистора (29) соединен с дополнительным (17) выходом второго (10) выходного усилителя тока.