Дифференциальный усилитель с повышенным коэффициентом усиления по напряжению

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Технический результат - повышение коэффициента усиления по напряжению. Дифференциальный усилитель (ДУ) содержит первый (1) и второй (2) входные транзисторы (Т), токовое зеркало (3), вход которого соединен с коллектором Т (1), а выход подключен к коллектору Т (2) и базе первого выходного Т (4), цепь установления статического режима (5), первый (6) и второй (7) выходы которой соединены с эмиттерами Т (1, 2), имеющую также неинвертирующий вход (8) относительно первого выхода (6). В схему введен дополнительный выходной Т (9), эмиттер которого соединен с коллектором Т (4), база подключена к неинвертирующему входу (8) цепи установления статического режима (5), а коллектор является токовым выходом (10) ДУ. 2 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах).

Известны схемы двухкаскадных дифференциальных усилителей (ДУ) с несимметричной активной нагрузки в коллекторной цепи транзисторов входного дифференциального каскада и вторым каскадом усиления, выполненным по схеме с общим эмиттером [1-20]. Такая архитектура ДУ является классической - на ее основе реализованы сотни аналоговых микросхем в различных странах мира.

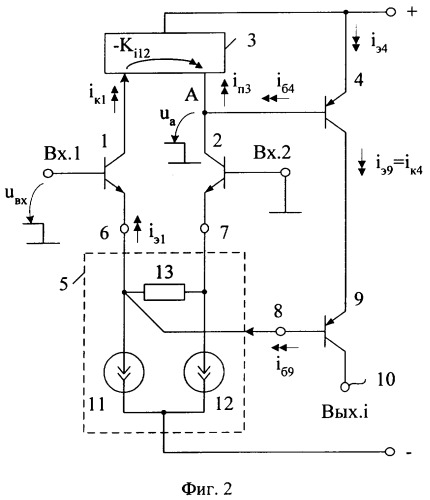

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №5.365.191, фиг.7, содержащий первый 1 и второй 2 входные транзисторы, токовое зеркало 3, вход которого соединен с коллектором первого входного транзистора 1, а выход подключен к коллектору второго входного транзистора 2 и базе первого выходного транзистора 4, цепь установления статического режима 5, первый 6 и второй 7 выходы которой соединены с эмиттерами первого 1 и второго 2 входных транзисторов, имеющую также неинвертирующий вход 8 относительно первого выхода 6.

Существенный недостаток известного ДУ состоит в том, что он характеризуется недостаточно высокой крутизной преобразования (S=iн/uвх) входного напряжения (uвх) в выходной ток (iн). Это отрицательно сказывается на общем коэффициенте усиления аналоговых устройств на его основе.

Основная цель предлагаемого изобретения состоит в повышении крутизны преобразования входного напряжения ДУ в его выходной ток и, как следствие, повышении коэффициента усиления по напряжению аналоговых микросхем на его основе.

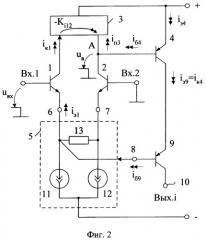

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, токовое зеркало 3, вход которого соединен с коллектором первого входного транзистора 1, а выход подключен к коллектору второго входного транзистора 2 и базе первого выходного транзистора 4, цепь установления статического режима 5, первый 6 и второй 7 выходы которой соединены с эмиттерами первого 1 и второго 2 входных транзисторов, имеющую также неинвертирующий вход 8 относительно первого выхода 6, предусмотрены новые элементы и связи - в схему введен дополнительный выходной транзистор 9, эмиттер которого соединен с коллектором первого выходного транзистора 4, база подключена к неинвертирующему входу 8 цепи установления статического режима 5, а коллектор является токовым выходом 10 дифференциального усилителя.

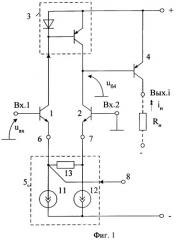

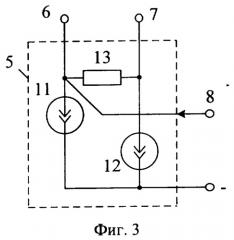

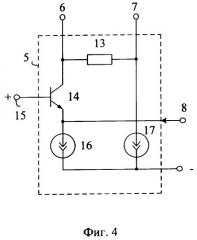

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2. На фиг.3, соответствующей п.2 формулы изобретения, и фиг.4, соответствующей п.3 формулы изобретения, показаны частные случаи выполнения цепи установления статического режима 5.

На фиг.5 представлена схема стабилизатора напряжения на основе предлагаемого ДУ, а на фиг.6 - схема стабилизатора на основе ДУ-прототипа в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.7 показан график зависимости от частоты петлевого усиления схем фиг.6 и фиг.5, который показывает, что предлагаемый ДУ обеспечивает более высокий (+26 дБ) уровень усиления по петле обратной связи.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, токовое зеркало 3, вход которого соединен с коллектором первого входного транзистора 1, а выход подключен к коллектору второго входного транзистора 2 и базе первого выходного транзистора 4, цепь установления статического режима 5, первый 6 и второй 7 выходы которой соединены с эмиттерами первого 1 и второго 2 входных транзисторов, имеющую также неинвертирующий вход 8 относительно первого выхода 6. В схему введен дополнительный выходной транзистор 9, эмиттер которого соединен с коллектором первого выходного транзистора 4, база подключена к неинвертирующему входу 8 цепи установления статического режима 5, а коллектор является токовым выходом 10 дифференциального усилителя.

В соответствии с п.2 формулы изобретения (фиг.3) цепь установления статического режима 5 содержит первый 11 и второй 12 источники опорного тока, между которыми включен резистор местной обратной связи 13, причем общий узел первого источника опорного тока 11 и резистора местной обратной связи 13 является первым выходом 6 цепи установления статического режима 5, общий узел второго 12 источника опорного тока и резистора 13 является вторым выходом 7 цепи установления статического режима 5, а неинвертирующий вход 8 соединен с общим узлом первого источника опорного тока 11 и резистора местной обратной связи 13.

В соответствии с п.3 формулы изобретения (фиг.4) цепь установления статического режима 5 содержит первый вспомогательный транзистор 14, коллектор которого соединен с первым выходом 6 цепи установления статического режима 5 и первым выводом резистора местной обратной связи 13, база связана с источником напряжения смещения 15, а эмиттер соединен с токовым входом 8 цепи установления статического режима 5 и вспомогательным источником тока 16, второй токостабилизирующий двухполюсник 17 соединен со вторым токовым выходом 7 цепи установления статического режима 5 и вторым выводом резистора местной обратной связи 13.

Рассмотрим работу заявляемого ДУ на примере анализа схемы фиг.2. Если напряжение на входе Вх.1 принимает отрицательное значение (uвх<0), то это вызывает увеличение тока базы транзистора 4 на величину

где β4>>1 - коэффициент усиления по току базы транзистора 4;

iэп (iкп) - приращения эмиттерного (коллекторного) токов n-го транзистора.

На основании токовых соотношений в транзисторе можно найти, что ток базы транзистора 9 и ток эмиттера транзистора 1

Поэтому коллекторный ток транзистора 1 и выходной ток токового зеркала 3

где Ki12≈1 - коэффициент усиления по току токового зеркала 3;

α1≈1 - коэффициент усиления по току эмиттера транзистора 1.

Таким образом, суммарное приращение тока в узле «А», обусловленное влиянием входного сопротивления второго каскада на транзисторе 4, определяется формулой

Учтем, что ток базы iб4

где Rвх.4=β4rэ4 - входное сопротивление транзистора 4;

rэ4 - дифференциальное сопротивление эмиттерного перехода транзистора 4.

Поэтому крутизна преобразования uвх в приращение выходного тока ДУ iн

где - коэффициент усиления по напряжению первого каскада;

rэ4 - дифференциальное сопротивление эмиттерного перехода транзистора 4;

Таким образом, крутизна преобразования uвх в выходной ток iн в заявляемом ДУ повышается:

В схеме ДУ-прототипа этот параметр определяется формулой

Таким образом, в предлагаемой схеме ДУ крутизна увеличивается в N-раз, где

Это позволяет получить более высокие параметры по предельному усилению без введения дополнительных каскадов.

Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice (фиг.7).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4.163.908.

2. Патент США №5.642.062.

3. Патент США №4.250.460.

4. Патент США №6.191.619.

5. Патент США №5.828.242.

6. Патент Канады №СА2472125.

7. Патент США №4.410.859.

8. Патент США №4.462.002.

9. Патент США №4.172.999.

10. Патент США №4.418.290.

11. Патент США №4.636.744.

12. Патент №WO 03/063344 A1.

13. А.св. СССР 1040593.

14. Патент США №4.783.637.

15. Патентная заявка US 2005/0225389 A1.

16. Патент США №5.140.281.

17. Патент США №Re. 35261.

18. Патент США №4.163.908.

19. Патент США №6.150.884.

20. Патент США №4.829.265.

1. Дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, токовое зеркало (3), вход которого соединен с коллектором первого входного транзистора (1), а выход подключен к коллектору второго входного транзистора (2) и базе первого выходного транзистора (4), цепь установления статического режима (5), первый (6) и второй (7) выходы которой соединены с эмиттерами первого (1) и второго (2) входных транзисторов, имеющая также неинвертирующий вход (8) относительно первого выхода (6), отличающийся тем, что в схему введен дополнительный выходной транзистор (9), эмиттер которого соединен с коллектором первого выходного транзистора (4), база подключена к неинвертирующему входу (8) цепи установления статического режима (5), а коллектор является токовым выходом (10) дифференциального каскада.

2. Устройство по п.1, отличающееся тем, что цепь установления статического режима (5) содержит первый (11) и второй (12) источники опорного тока, между которыми включен резистор местной обратной связи (13), причем общий узел первого источника опорного тока (11) и резистора местной обратной связи (13) является первым выходом (6) цепи установления статического режима (5), общий узел второго (12) источника опорного тока и резистора (13) является вторым выходом (7) цепи установления статического режима (5), а неинвертирующий вход (8) соединен с общим узлом первого источника опорного тока (11) и резистора местной обратной связи (13).

3. Устройство по п.1, отличающееся тем, что цепь установления статического режима (5) содержит первый вспомогательный транзистор (14), коллектор которого соединен с первым выходом (6) цепи установления статического режима (5) и первым выводом резистора местной обратной связи (13), база связана с источником напряжения смещения (15), а эмиттер соединен с токовым входом (8) цепи установления статического режима (5) и вспомогательным источником тока (16), второй токостабилизирующий двухполюсник (17) соединен со вторым токовым выходом (7) цепи установления статического режима (5) и вторым выводом резистора местной обратной связи (13).