Способ компенсации размытости изображения движущихся объектов и устройство для его реализации

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано для повышения четкости изображения, поступающего с видеодатчика, при движении видеодатчика или нахождении в кадре движущихся объектов. Задачей изобретения является компенсация размытости изображения движущихся объектов в режиме реального времени. Предложен способ компенсации размытости изображения, включающий: расчет разности между измеренной яркостью пикселей изображения и ранее полученной ее оценкой на основе последовательности предыдущих кадров, обнаружение движения путем сравнения полученной разности с пороговой величиной, определение направления движения каждого пикселя, объединение движущихся в одном направлении смежных пикселей в объект, выполнение подчеркивания контуров движущихся объектов путем сложения их исходного B(k) и градиентного ▿(В(k)) изображений и формирование выходного изображения , где k1, k2 - весовые коэффициенты. В устройство компенсации размытости изображения, содержащее датчик изображения, введены контроллер, модуль обнаружения движения мод, модуль определения объектов, модуль коррекции, первое ОЗУ, второе ОЗУ, третье ОЗУ, счетчик, первый компаратор, второй компаратор, первый мультиплексор, второй мультиплексор, третий мультиплексор, четвертый мультиплексор, пятый мультиплексор, шестой мультиплексор, седьмой мультиплексор, первый демультиплексор, второй демультиплексор. 2 н.п. ф-лы, 11 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для повышения четкости изображения, поступающего с видеодатчика, при движении видеодатчика или нахождении в кадре движущихся объектов.

Известен способ устранения размытости изображения вследствие движения объектов на цифровом изображении (Tull D.L. Preventing blur caused by motion of the subject in a digital image, 2002, патент США №6441848). Способ включает в себя получение изображения матричным фоточувствительным приемником излучения (МФПИ) в течение заданного времени накопления; вычисление значения переменной, пропорциональной интенсивности потока излучения для каждого пикселя; вычисление второй производной указанной переменной для каждого пикселя; сравнения значения второй производной указанной переменной с пороговым значением, достижение которого соответствует обнаружению движения; вычисление времени накопления для каждого пикселя в процентном соотношении к текущему времени накопления; изменение времени накопления для каждого пикселя согласно вычисленному значению процентного соотношения.

Недостатками данного способа являются:

- наличие искажений на результирующем изображении, вызванных перепадами яркости на границах областей с различным временем накопления;

- его неприменимость для приемников изображения на основе приборов с зарядовой связью (ПЗС), для которых невозможно изменение времени накопления каждого пикселя в отдельности.

Известно устройство, реализующее функцию устранения размытости изображения вследствие движения объектов на цифровом изображении (Tull D.L. Preventing blur caused by motion of the subject in a digital image, 2002, патент США №6441848), содержащее матричный фоточувствительный приемник излучения, в состав каждого элементарного фотосенсора (ЭФ) которого входит схема определения движения; фокусирующую линзу; схему памяти, подключенную к матричному фоточувствительному приемнику излучения, которая хранит значения времени накопления для каждого элементарного фотосенсора.

Недостатками данного устройства являются:

- высокая сложность его технологического исполнения, связанная с необходимостью встраивания в каждый пиксель схемы определения движения;

- снижение коэффициента заполнения пикселя (отношение светочувствительной поверхности пикселя к его общей площади) вследствие встраивания в каждый пиксель схемы определения движения, что приводит к снижению чувствительности устройства и повышению уровня геометрического шума и шума фиксированной разводки.

Наиболее близким к изобретению является способ компенсации размытости изображения, вызванной движением или насыщением элементарного фотосенсора, с одновременным расширением динамического диапазона на основе синтеза изображения по серии кадров (Liu et. all, Motion/saturation detection system and method for synthesizing high dynamic range motion blur free images from multiple captures, 2006, патент США №7061524). Согласно способу рассчитывают разность между измеренной яркостью пикселей изображения и ранее полученной ее оценкой на основе последовательности предыдущих кадров, обнаруживают движение путем сравнения полученной разности с пороговой величиной, при отсутствии движения принимают полученные измерения яркости за истинное изображение, при наличии движения измеренные значения яркости корректируются на основе полученных оценок.

Основным недостатком данного способа является обработка как минимум четырех кадров для получения изображения с достаточной степенью компенсации размытости, что накладывает значительные ограничения на быстродействие устройства, реализующего способ, и в некоторых случаях вследствие формирования современными видеодатчиками изображений с большой разрешающей способностью приводит к невозможности функционирования устройства в режиме реального времени.

Наиболее близким к предлагаемому является устройство компенсации размытости изображения, вызванной движением или насыщением ЭФ (Liu et. all, Motion/saturation detection system and method for synthesizing high dynamic range motion blur free images from multiple captures, 2006, патент США №7061524). Устройство состоит из: датчика изображения, каждый ЭФ которого содержит средства обнаружения движения/насыщения между предыдущим кадром и текущим кадром; блока обработки, определяющего, принимать ли для каждого ЭФ выборку изображения, зафиксированную в течение текущего кадра; блока оценки яркости в течение глобального времени экспозиции; блока определения разности между измеренной яркостью, полученной во время текущего кадра, и оценкой яркости, сгенерированной в течение предыдущего кадра, для каждого ЭФ; блока сравнения вычисленной разности с пороговым значением для каждого ЭФ; блока модификации оценки яркости для каждого ЭФ; блока формирования выходного изображения на основе заключительной оценки яркости для каждого ЭФ.

Недостатком данного устройства является низкий коэффициент заполнения пикселя (не более 10%), что существенно ухудшает чувствительность видеодатчика, высокая сложность его технологического исполнения и высокая структурная сложность, связанные с необходимостью встраивания в каждый пиксель схемы обнаружения движения.

Технической задачей изобретения является компенсация размытости изображения движущихся объектов в режиме реального времени для МФПИ любого типа (ПЗС, на основе полупроводниковых комплементарных пар металл-оксид-полупроводник (КМОП)) с одновременным снижением технологического исполнения устройства и снижением его структурной сложности.

Задача решается тем, что в известный способ компенсации размытости изображения, вызванной движением, включающий определение межкадровой разности яркости изображения, определение движения для каждого пикселя изображения, корректировку яркости только движущихся пикселей, согласно изобретению введены определение направления движения для каждого пикселя путем обработки смежных кадров скользящим окном 3×3 элемента и анализа суммарных значений элементов межкадровых разностей, объединение движущихся в одном направлении смежных пикселей в объект на основе анализа расстояния между двумя пикселями с одинаковым направлением движения, подчеркивание контуров движущихся объектов путем сложения исходного изображения движущегося объекта с его градиентным изображением.

Техническая задача решается тем, что в устройство, содержащее датчик изображения, введены контроллер, модуль обнаружения движения МОД, модуль определения объектов, модуль коррекции, первое ОЗУ, второе ОЗУ, третье ОЗУ, счетчик, элемент ИЛИ, первый компаратор, второй компаратор, первая константа, вторая константа, первый мультиплексор, второй мультиплексор, третий мультиплексор, четвертый мультиплексор, пятый мультиплексор, шестой мультиплексор, седьмой мультиплексор, первый демультиплексор, второй демультиплексор, третья константа.

Изобретение может быть использовано для компенсации размытости изображения движущихся объектов в режиме реального времени в различных видеодатчиках и системах технического зрения, выполненных на базе твердотельных МФПИ различных типов.

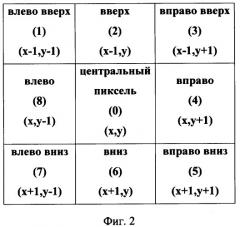

Сущность изобретения поясняется чертежами, где на фиг.1 приведен алгоритм способа компенсации размытости изображения, на фиг.2 - коды направления перемещения пикселя в восьмисвязной окрестности, на фиг.3 - структурная схема устройства компенсации размытости изображения движущихся объектов, на фиг.4 - структурная схема контроллера, на фиг.5 - структурная схема модуля обнаружения движения, на фиг.6 - структурная схема регистрового блока, на фиг.7 - структурная схема суммирующего блока, на фиг.8 - структурная схема модуля определения объектов, на фиг.9 - структурная схема модуля коррекции, на фиг.10 - структурная схема модуля подчеркивания контуров, на фиг.11 - значения констант регистрового блока.

Процесс компенсации размытости изображения (фиг.1) состоит из нескольких этапов: считывание изображения, выделение на изображении движущихся пикселей на основе анализа межкадровой разности, определение направления движения каждого пикселя, объединение движущихся в одном направлении смежных пикселей в объект, подчеркивание контуров движущихся объектов для компенсации размытия изображения путем сложения их исходного и градиентного изображений, формирование выходного изображения.

Движение каждого пикселя относительно текущего k-го кадра определяется по принципу межкадрового вычитания: значение разности яркостей статичных пикселей на смежных кадрах равно 0 (при условии неизменной освещенности). Расчет производится для восьмисвязной окрестности каждого пикселя, каждому из восьми возможных направлений движения присваивается определенный код.

Для определения номера направления перемещения r (фиг.2) каждого пикселя (х,у) кадр обрабатывается скользящим окном размера 3×3 следующим образом: для каждого пикселя (х,у) текущего кадра составляется матрица яркости В(k) смежных с ним пикселей по 8 направлениям:

Элементы матрицы В(k), индексы которых равны 0, (Х+1) или (Y+1), принимаются равными 0, где X, Y - размеры кадра по горизонтали и вертикали соответственно.

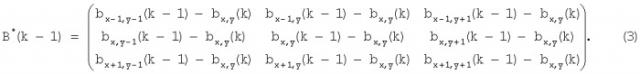

Далее матрица В(k) преобразуется в матрицу В*(k) путем вычитания из яркостей смежных пикселей яркости центрального пикселя:

Данное преобразование позволяет учесть возможные изменения внешней освещенности сцены с одним и тем же расположением объектов в текущем кадре относительно предыдущего кадра.

Аналогичным образом для обработки предыдущего (k-1)-го кадра составляется матрица В*(k-1):

Результат вычитания матрицы B*(k-1) из матрицы В*(k) позволяет судить о том, остался ли центральный пиксель неподвижным на смежных кадрах, если равен нулю центральный пиксель результирующей матрицы В**(k/k-1), т.е. выполняется следующее условие:

Если центральный пиксель результирующей матрицы В**(k/k-1) не равен 0, делается вывод о движении данного пикселя.

Далее производится определение направления движения каждого пикселя. Для этого из матрицы B*(k-1) формируются 8 матриц, сдвинутых на 1 пиксель по каждому из 8 направлений (недостающие строки и/или столбцы заполняются нулями). Матрицы определения перемещения центрального пикселя на текущем кадре относительно предыдущего задаются в общем виде следующим образом:

Для формирования 8 результирующих матриц перемещений по каждому из 8 направлений необходимо вычесть каждую матрицу определения направления из матрицы В*(k). Результирующие матрицы яркости изображения, вычисляющие перемещение пикселя на текущем кадре, задаются в общем виде следующим образом:

За направление движения пикселя принимается то направление, для которого суммарное значение изменений яркости (сумма всех элементов результирующих матриц) по модулю является минимальным.

где sup_ind(*) - функция, значением которой является величина верхнего индекса матрицы Вr(k/k-1).

Затем производится определение движущихся объектов. Для этого необходимо найти соседние пиксели с одинаковым направлением движения, поиск которых осуществляется в соответствии с формулами (8)-(13)

Соседние пиксели с одинаковым направлением движения группируются в объекты в соответствие с формулами:

где ξ,ς - координаты пикселя; Np+1 - минимальное количество точек в объекте.

Под объектом ED понимается совокупность отличных от фона точек изображения с направлением движения D, таких, что для каждой точки найдется не менее одной соседней точки, расположенной на расстоянии 1 пиксель, причем количество таких точек в объекте должно превышать пороговое значение Np.

После этого реализуется коррекция яркостей движущихся объектов путем подчеркивания их контуров (сложения исходного изображения с градиентным изображением). Выходные значения яркостей пикселей рассчитывается следующим образом:

где ▿(bx,y(k)) - градиентное изображение, такое что

Значения яркости статичных областей изображения остаются неизменными.

Устройство компенсации размытости изображения (фиг.3) содержит датчик изображения ДИ 10, контроллер 1, модуль обнаружения движения МОД 2, модуль определения объектов МОО 3, модуль коррекции МК 4, первое ОЗУ 5, второе ОЗУ 6, третье ОЗУ 7, счетчик 100, элемент ИЛИ 101, первый компаратор 102, первый мультиплексор 51, второй мультиплексор 52, третий мультиплексор 53, четвертый мультиплексор 54, пятый мультиплексор 55, шестой мультиплексор 57, седьмой мультиплексор 59, первый демультиплексор 56, второй демультиплексор 58, причем вход CLK/3 предназначен для подачи тактирующего сигнала в ДИ 10 и подключен к первому входу контроллера 1, групповой выход ДИ 10 подключен к первому групповому входу контроллера 1, второй групповой выход контроллера 1 подключен к первым групповым входам первого мультиплексора 51 и третьего мультиплексора 53, групповой выход первого мультиплексора 51 подключен к групповому входу первого ОЗУ 5, групповой вход-выход первого ОЗУ 5 подключен к групповому входу первого демультиплексора 56 и к групповому выходу пятого мультиплексора 55, первый групповой выход демультиплексора 56 подключен к четвертому групповому входу контроллера 1, групповой вход-выход второго ОЗУ 6 подключен к групповому входу второго демультиплексора 58 и к групповому выходу шестого мультиплексора 57, третий групповой выход контроллера 1 подключен к системной шине, четвертый групповой выход контроллера 1 подключен к первому групповому входу шестого мультиплексора 57, первый групповой выход контроллера 1 подключен к первому групповому входу пятого мультиплексора 55, первый выход контроллера 1 подключен к первому входу второго мультиплексора 52, выход второго мультиплексора 52 подключен к входу первого ОЗУ 5, второй выход контроллера 1 подключен к первому входу четвертого мультиплексора 54, выход которого подключен к входу второго ОЗУ 6, второй и третий групповые входы контроллера 1 предназначены для подачи констант (Х-1) и (Y-1) соответственно (где X, Y - размерность изображения по горизонтали и вертикали), второй вход контроллера 1 предназначен для подачи тактового сигнал CLK и соединен со вторым входом МОД 2, третий вход контроллера 1 подключен к выходу первого компаратора 102, первый групповой вход которого подключен к групповому выходу счетчика 100 и пятому групповому входу МОД 2, на второй групповой вход первого компаратора 102 подана константа 0, третий выход контроллера 1 подключен к первому входу элемента ИЛИ 101, первый вход МОД 2 предназначен для подачи тактового сигнала CLK/25, первый и второй групповые входы МОД 2 предназначены для подачи констант (Х-3) и (Y-3) соответственно, третий групповой вход МОД 2 подключен к групповому выходу второго демультиплексора 58, четвертый групповой вход МОД 2 подключен ко второму групповому выходу первого демультиплексора 56, первый групповой выход МОД 2 подключен ко вторым групповым входам первого мультиплексора 51 и третьего мультиплексора 53, второй групповой выход МОД 2 подключен к второму групповому входу седьмого мультиплексора 59, третий групповой выход МОД 2 подключен к групповому входу-выходу ОЗУ 7 и первому групповому входу МОО 3, первый выход МОД 2 подключен к второму входу элемента ИЛИ 101, второй выход МОД 2 подключен к входу седьмого мультиплексора 59, третий выход МОД 2 подключен к входу третьего ОЗУ 7, второй и третий групповые входы МОО 3 предназначены для подачи констант (Х-2) и (Y-2) соответственно, четвертый групповой вход МОО 3 подключен к первому групповому выходу МК 4, пятый групповой вход МОО 3 подключен к четвертому групповому выходу МК 4, шестой групповой вход МОО 3 подключен к групповому выходу счетчика 100, первый, второй и третий входы МОО 3 предназначены для подачи тактовых сигналов CLKX, CLKX6, CLKY соответственно, первый групповой выход МОО 3 подключен к первому групповому входу седьмого мультиплексора 59, групповой выход которого соединен с групповым входом третьего ОЗУ 7, второй групповой выход МОО 3 подключен к первому групповому входу МК 4, третий групповой выход МОО 3 подключен к второму групповому входу МК 4, четвертый групповой выход MOO 3 подключен к третьему групповому входу МК 4, выход МОО 3 подключен к третьему входу элемента ПЛИ 101 и к третьему входу МК 4, четвертый вход элемента ИЛИ 101 подключен к выходу МК 4, второй групповой выход МК 4 подключен к третьему групповому входу первого мультиплексора 51, третий групповой выход МК 4 подключен к второму групповому входу пятого мультиплексора 55, четвертый групповой вход МК 4 предназначен для подачи порогового значения Р, определяющего минимально допустимое количество пикселей в объекте, пятый групповой вход МК 4 подключен к третьему групповому выходу первого демультиплексора 56, первый и второй входы МК 4 предназначены для подачи тактовых сигналов CLKW и CLKZ соответственно, на второй вход второго мультиплексора 52 подана константа 0, групповой выход счетчика 100 подключен к четвертому групповому входу первого мультиплексора 51, групповому входу второго мультиплексора 52, третьему групповому входу третьего мультиплексора 53, пятому групповому входу четвертого мультиплексора 54, третьему групповому входу пятого мультиплексора 55, к второму групповому входу шестого мультиплексора 57, а также к вторым групповым входам первого демультиплексора 56 и второго демультиплексора 58, на второй, третий, четвертый входы четвертого мультиплексора 54 подается константа 0, при этом первый мультиплексор 51 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его четвертом групповом входе, со своего второго группового входа - при значении «1», со своего третьего группового входа - при значении «3», второй мультиплексор 52 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его третьем групповом входе, со своего второго группового входа - при значении «3», третий мультиплексор 53 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его третьем групповом входе, со своего второго группового входа - при значении «1», четвертый мультиплексор 54 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его пятом групповом входе, со своего второго группового входа - при значении «1», со своего третьего группового входа - при значении «2», со своего четвертого группового входа - при значении «3», пятый мультиплексор 55 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его третьем групповом входе, со своего второго группового входа - при значении «3», шестой мультиплексор 57 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его втором групповом входе, первый демультиплексор 56 обеспечивает прохождение сигнала со своего группового входа на первый групповой выход при значении «0» на его втором групповом входе, при значении «1» - на свой второй групповой выход, при значении «3» - на свой третий групповой выход, второй демультиплексор 58 обеспечивает прохождение сигнала со своего группового входа на свой групповой выход при значении «1» на его втором групповом входе, седьмой мультиплексор 59 обеспечивает прохождение сигнала со своего первого группового входа на свой групповой выход при значении «0» на его входе, и со второго группового входа - при значении «1».

Контроллер 1 (фиг.4) содержит: первый элемент ИЛИ 11, второй элемент ИЛИ 12, первый счетчик 13, второй счетчик 14, третий счетчик 15, первый компаратор 16, второй компаратор 17, формирователь адреса 18, элемент И 19, буфер 110 и демультиплексор 111, причем первый вход первого счетчика 13 является первый входом контроллера 1 и предназначен для подачи тактового сигнала CLK/3, первый групповой выход первого счетчика 13 подключен к первым групповым входам первого компаратора 16 и формирователя адреса 18, групповой выход формирователя 18 является вторым групповым выходом контроллера 1, второй групповой вход первого компаратора 16 является вторым групповым входом контроллера 1, выход первого компаратора 16 подключен ко второму входу первого элемента ИЛИ 11, к первому входу второго счетчика 14 и к первому входу элемента И 19, групповой выход второго счетчика 14 подключен к второму групповому входу формирователя адреса 18 и к первому групповому входу второго компаратора 17, второй групповой вход компаратора 17 является третьим групповым входом контроллера 1, выход компаратора 17 подключен ко второму входу элемента И 19, к второму входу второго элемента ИЛИ 12 и первому входу первого элемента ИЛИ 11, третий вход первого элемента ИЛИ 11, первый вход второго элемента ИЛИ 12 и второй вход третьего счетчика 15 подключены к третьему входу контроллера 1, первый вход третьего счетчика 15 является вторым входом контроллера 1 и предназначен для подачи тактового сигнала CLK, групповой выход третьего счетчика 15 подключен к второму групповому входу буфера 110 и второму групповому входу демультиплексора 111, первый групповой вход буфера 110 является первым групповым входом контроллера, групповой выход буфера 110 является первым групповым выходом контролера 1, первый групповой вход демультиплексора 111 является четвертым групповым входом контроллера 1, первый групповой выход демультиплексора 111 является третьим групповым выходом контроллера 1, второй групповой выход демультиплексора 111 является четвертым групповым выходом контроллера 1, старший разряд группового выхода третьего счетчика 15 является первым выходом контроллера 1, выход элемента И 19 является третьим выходом контроллера 1, младший разряд группового выхода третьего счетчика 15 является вторым выходом контроллера 1.

Модуль обнаружения движения МОД 2 (фиг.5) включает первый счетчик 21, второй счетчик 22, третий счетчик 23, четвертый счетчики 24, первый компаратор 25, второй компаратор 26, первый сумматор 27, второй сумматор 28, первый формирователь адреса 29, элемент ИЛИ 210, элемент И 211, первый регистровый блок 212, второй регистровый блок 213, третий регистровый блок 214, четвертый регистровый блок 215, пятый регистровый блок 216, шестой регистровый блок 217, седьмой регистровый блок 218, восьмой регистровый блок 219, девятый регистровый блок 220, десятый регистровый блок 221, первый суммирующий блок 222, второй суммирующий блок 223, третий суммирующий блок 223, четвертый суммирующий блок 225, пятый суммирующий блок 226, шестой суммирующий блок 227, седьмой суммирующий блок 228, восьмой суммирующий блок 229, девятый суммирующий блок 230, схема определения минимума 231, третий компаратор 233, четвертый компаратор 234, пятый компаратор 235, шестой компаратор 236, седьмой компаратор 237, восьмой компаратор 238, девятый компаратор 239, десятый компаратор 240, одиннадцатый компаратор 241, шифратор 242, третий сумматор 244, четвертый сумматор 245, второй формирователь адреса 246, двенадцатый компаратор 247, причем первый вход первого счетчика 21 является первым входом МОД 2 и предназначен для подачи тактирующего сигнала с частотой CLK/25, второй вход первого счетчика 21, являющийся входом сброса, подключен к выходу элемента ИЛИ 210, выход первого компаратора 25 подключен ко второму входу элемента ИЛИ 210 и первому входу второго счетчика 22, групповой выход первого счетчика 21 подключен к первому групповому входу первого компаратора 25, первому групповому входу первого сумматора 27 и первому групповому входу четвертого сумматора 245, групповой выход второго счетчика 22 подключен к первому групповому входу второго компаратора 26, первому групповому входу второго сумматора 28 и первому групповому входу третьего сумматора 244, второй групповой вход первого компаратора 25 является первым групповым входом МОД 2 и предназначен для подачи постоянной величины (Х-3), второй групповой вход второго компаратора 26 является вторым групповым входом МОД 2 и предназначен для подачи постоянной величины (Y-3) выход второго компаратора 26 подключен ко второму входу второго счетчика 22, являющимся входом сброса, и к первому входу элемента ИЛИ 210, вход третьего счетчика 23, являющийся вторым входом МОД 2, предназначен для подачи тактового сигнала CLK, групповой выход третьего счетчика 23 подключен ко второму групповому входу первого сумматора 27, выход третьего счетчика 23 подключен к входу четвертого счетчика 24, групповой выход которого подключен к второму групповому входу второго сумматора 28, групповой выход первого сумматора 27 подключен к первому групповому входу первого формирователя адреса 29, а групповой выход второго сумматора 28 подключен ко второму групповому входу первого формирователя адреса 29, выход первого формирователя адреса 29 является первым групповым выходом МОД 2, первый групповой вход первого регистрового блока 212 является четвертым групповым входом МОД 2, третий групповой вход МОД 2 подключен к первым групповым входам второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221, вторые групповые входы первого регистрового блока 212, второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 подключены к групповому выходу четвертого счетчика 24, третьи групповые входы первого регистрового блока 212, второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 подключены к групповому выходу третьего счетчика 23, группа выходов первого регистрового блока 212 подключена к первым группам входов первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, пятого суммирующего блока 226, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230, группы выходов второго регистрового блока 213, третьего регистрового блока 214, четвертого регистрового блока 215, пятого регистрового блока 216, шестого регистрового блока 217, седьмого регистрового блока 218, восьмого регистрового блока 219, девятого регистрового блока 220, десятого регистрового блока 221 подключены к вторым групповым входам первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, пятого суммирующего блока 226, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230, групповые выходы первого суммирующего блока 222, второго суммирующего блока 223, третьего суммирующего блока 224, четвертого суммирующего блока 225, пятого суммирующего блока 226, шестого суммирующего блока 227, седьмого суммирующего блока 228, восьмого суммирующего блока 229, девятого суммирующего блока 230 подключены соответственно к первому, второму, третьему, четвертому, пятому, шестому, седьмому, восьмому, девятому входам блока определения минимума 231, а также к первым групповым входам третьего компаратора 233, четвертого компаратора 234, пятого компаратора 235, шестого компаратора 236, седьмого компаратора 237, восьмого компаратора 238, девятого компаратора 239, десятого компаратора 240, вторые групповые входы которых подключены к групповому входу схемы определения минимума 231, групповой выход пятого суммирующего блока 226 подключен к первому групповому входу одиннадцатого компаратора 241, на второй групповой вход которого подается константа 0, выходы третьего компаратора 233, четвертого компаратора 234, пятого компаратора 235, шестого компаратора 236, седьмого компаратора 237, восьмого компаратора 238, девятого компаратора 239, десятого компаратора 240 подключены к групповому входу шифратора 242, групповой выход которого является третьим групповым выходом МОД 2, выход одиннадцатого компаратора 241 является третьим выходом МОД 2, вторые групповые входы третьего сумматора 244, четвертого сумматора 245 и двенадцатого компаратора 247 подключены к константе 2, групповые выходы третьего сумматора 244 и четвертого сумматора 245 подключены к групповым входам второго формирователя адреса 246, групповой выход которого является вторым групповым выходом МОД 2, первый групповой вход двенадцатого компаратора 247 является пятым групповым входом МОД 2, входы элемента И 211 подключены к выходам первого компаратора 25 и второго компаратора 26 соответственно, выход элемента И 211 является первым выходом МОД 2.

Каждый регистровый блок 212÷221 (фиг.6) состоит из первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89, первого регистра 810, второго регистра 811, третьего регистра 812, четвертого регистра 813, пятого регистра 814, шестого регистра 815, седьмого регистра 816, восьмого регистра 817, девятого регистра 818, первого сумматора 819, второго сумматора 820, третьего сумматора 821, четвертого сумматора 822, пятого сумматора 823, шестого сумматора 824, седьмого сумматора 825, восьмого сумматора 826, первой константы 851, второй константы 852, третьей константы 853, четвертой константы 854, пятой константы 855, шестой константы 856, седьмой константы 857, восьмой константы 858, девятой константы 859, десятой константы 860, одиннадцатой константы 861, двенадцатой константы 862, тринадцатой константы 863, четырнадцатой константы 864, пятнадцатой константы 865, шестнадцатой константы 866, семнадцатой константы 867, восемнадцатой константы 868, причем первый групповой вход регистрового блока подключен к групповым входам первого регистра 810, второго регистра 811, третьего регистра 812, четвертого регистра 813, пятого регистра 814, шестого регистра 815, седьмого регистра 816, восьмого регистра 817, девятого регистра 818, второй групповой вход регистрового блока подключен к первым групповым входам первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89, третий групповой вход регистрового блока подключен к третьим групповым входам первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89, выходы первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89 подключены ко входам первого регистра 810, второго регистра 811, третьего регистра 812, четвертого регистра 813, пятого регистра 814, шестого регистра 815, седьмого регистра 816, восьмого регистра 817, девятого регистра 818 соответственно, групповые выходы первого регистра 810, второго регистра 811, третьего регистра 812, четвертого регистра 813, шестого регистра 815, седьмого регистра 816, восьмого регистра 817, девятого регистра 818 подключены к первым групповым входам первого сумматора 819, второго сумматора 820, третьего сумматора 821, четвертого сумматора 822, пятого сумматора 823, шестого сумматора 824, седьмого сумматора 825, восьмого сумматора 826 соответственно, групповой выход пятого регистра 814 подключен ко вторым групповым входам первого сумматора 819, второго сумматора 820, третьего сумматора 821, четвертого сумматора 822, пятого сумматора 823, шестого сумматора 824, седьмого сумматора 825, восьмого сумматора 826, выходы первого сумматора 819, второго сумматора 820, третьего сумматора 821, четвертого сумматора 822, пятого сумматора 823, шестого сумматора 824, седьмого сумматора 825, восьмого сумматора 826 представляют собой группу выходов регистрового блока, выход пятого сумматора 823 является пятым выходом группы выходов регистрового блока, выход седьмого сумматора 825 является седьмым выходом группы выходов регистрового блока, первая константа 851, третья константа 853, пятая константа 855, седьмая константа 857, девятая константа 859, одиннадцатая константа 861, тринадцатая константа 863, пятнадцатая константа 865, семнадцатая константа 867 подключены ко вторым групповым входам первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89 соответственно, вторая константа 851, четвертая константа 854, шестая константа 856, восьмая константа 858, десятая константа 860, двенадцатая константа 862, четырнадцатая константа 864, шестнадцатая константа 866, восемнадцатая константа 868 подключены к четвертым групповым входам первого компаратора 81, второго компаратора 82, третьего компаратора 83, четвертого компаратора 84, пятого компаратора 85, шестого компаратора 86, седьмого компаратора 87, восьмого компаратора 88, девятого компаратора 89 соответственно. Значения первой константы 851, второй константы 852, третьей константы 853, четвертой константы 854, пятой константы 855, шестой константы 856, седьмой константы 857, восьмой константы 858, девятой константы 859, десятой константы 860, одиннадцатой константы 861, двенадцатой константы 862, тринадцатой константы 863, четырнадцатой константы 864, пятнадцатой константы 865, шестнадцатой константы 866, семнадцатой константы 867, восемнадцатой константы 868 определяется по таблице, изображенной на фиг.11.

Каждый суммирующий блок 222-230 (фиг.7) состоит из первого сумматора 91, второго сумматора 92, третьего сумматора 93, четвертого сумматора 894, пятого сумматора 95, шестого сумматора 96, седьмого сумматора 97, восьмого сумматора 98, девятого сумматора 99, причем выходы первого сумматора 91, второго сумматора 92, третьего сумматора 93, четвертого сумматора 94, пятого сумматора 95, шестого сумматора 96, седьмого сумматора 97, восьмого сумматора 98 подключены к первому, второму, третьему, четвертому, пятому, шестому, седьмому, восьмому входам девятого сумматора 99 соответственно, первые входы первого сумматора 91, второго сумматора 92, третьего сумматора 93, четвертого сумматора 94, пятого сумматора 95, шестого сумматора 96, седьмого сумматора 97, восьмого сумматора 98 являются первой группой входов суммирующего блока, вторые входы первого сумматора 91, второго сумматора 92, третьего сумматора 93, четвертого сумматора 94, пятого сумматора 95, шестого сумматора 96, седьмого сумматора 97, восьмого сумматора 98 являются второй группой входов суммирующего блока, групповой выход девятого сумматора 99 является групповым выходом суммирующего блока.

Модуль определения объектов МОО 3 (фиг.8) состоит из первого счетчика 31, второго счетчика 32, третьего счетчика 33, четвертого счетчика 34, пятого счетчика 35, шестого счетчика 36, триггера 37, первого элемента И 38, первого элемента ИЛИ 39, первого сумматора 310, второго сумматора 311, третьего сумматора 312, четвертого сумматора 313, пятого сумматора 314, первого компаратора 315, второго компаратора 316, второго формирователя адреса 318, преобразователя данных 319, первого формирователя адреса 320, второго элемента И 321, первого мультиплексора 322, первого элемента НЕ 323, первого регистра 324, третьего компаратора 325, третьего элемента И 327, четвертого