Быстродействующий аналого-цифровой преобразователь и способ его калибровки

Иллюстрации

Показать всеИзобретение относится к электронике и может быть использовано в микроэлектронных системах обработки аналоговых сигналов и преобразования аналоговой информации в цифровую, в частности, при разработке быстродействующих аналого-цифровых преобразователей (АЦП). Технический результат заключается в повышении быстродействия, уменьшении погрешности преобразования и потребляемой мощности быстродействующих АЦП, а также уменьшении площади кристалла АЦП. АЦП содержит М-разрядный АЦП1 с последовательным резистивным делителем и М-разрядный цифроаналоговый преобразователь (ЦАП), подключенные к опорному источнику Vref с синфазным уровнем Vcm, устройство выборки и хранения разностного сигнала входа АЦП и выходного напряжения ЦАП с коэффициентом усиления F и АЦП2 с дифференциальным опорным напряжением Vref2, меньшим Vref. М-разрядный ЦАП включает две группы ключей, коммутирующих к дифференциальным выходам ЦАП выбранную пару симметрично расположенных отводов последовательного резистивного делителя, выходные напряжения устройства выборки и хранения (УВХ) и дифференциальное опорное напряжение АЦП2 имеют синфазный уровень Vcm2, а Vref2 равно F·Vref/2M-1, причем F не превышает 2. 2 н. и 15 з.п. ф-лы, 14 ил., 1 табл.

Реферат

Изобретение относится к электронике и может быть использовано в микроэлектронных системах обработки аналоговых сигналов и преобразования аналоговой информации в цифровую, в частности, при разработке быстродействующих аналого-цифровых преобразователей (АЦП).

Цель изобретения - повышение быстродействия, уменьшение погрешности преобразования и потребляемой мощности быстродействующих АЦП, а также уменьшение площади кристалла АЦП.

Известно множество схем быстродействующих АЦП, однако все они сводятся к двум основным типам: параллельного преобразования и конвейерного (многокаскадного) преобразования, причем в каждом каскаде конвейерного АЦП может проводиться параллельное преобразование нескольких разрядов, что уменьшает число каскадов конвейера.

Параллельные N-разрядные АЦП имеют 2N-1 компараторов, подключенных непосредственно к входу АЦП, что обуславливает их очевидные недостатки при больших N, такие как большая входная емкость, ограничивающая скорость входного сигнала, большой ток потребления и большая площадь кристалла. Кроме того, большие импульсные токи, возникающие при одновременном срабатывании большого количества компараторов, приводят к увеличению погрешностей АЦП.

Конвейерные N-разрядные АЦП могут иметь N-последовательно включенных каскадов одноразрядного преобразования (см., Я.Мулявка, «Схемы на операционных усилителях с переключаемыми конденсаторами», изд-во «Мир», Москва, 1992 г., стр.364, Рис.10.19). В каждом каскаде этого АЦП производится одноразрядное аналого-цифровое преобразование, вычитание из входного сигнала опорного уровня при превышении входным сигналом этого уровня и умножение на 2 остаточной разности или входного сигнала, меньшего опорного уровня. Конвейерные N-разрядные АЦП могут иметь также 2N/M каскадов М-разрядного преобразования, например два N/2 разрядных каскада (см., Ф.Ален, Э.Санчес-Синенсио, «Электронные схемы с переключаемыми конденсаторами», изд-во «Радио и связь», Москва, 1989 г., стр.435, Рис.7.7.3). В каждом каскаде этого АЦП производится М-разрядное аналого-цифровое преобразование, вычитание из входного сигнала ближайшего из 2м опорных уровней и умножение остаточной разности на 2M. Для устранения ошибок аналого-цифрового преобразования предыдущего каскада часто используются избыточное кодирование в последующем каскаде преобразования и цифровая коррекция кода, полученного в предыдущем каскаде.

Недостатками конвейерных АЦП является многократное умножение сигналов схемами на переключаемых конденсаторах с операционным усилителем, ведущее к погрешностям АЦП, связанным с погрешностями коэффициентов умножения из-за погрешности отношения емкостей конденсаторов и конечного усиления операционного усилителя. Для получения максимального отношения сигнал/шум стремятся обеспечить максимально возможную амплитуду входного аналогового сигнала и соответственно величины опорного напряжения. При этом необходимо использовать высокое напряжение питания, большее величины опорного напряжения, и соответственно высоковольтных транзисторов, что ограничивает возможности повышения быстродействия и уменьшения потребляемой мощности и площади кристалла АЦП. Кроме того, конечная скорость роста выходного напряжения усилителей ограничивает быстродействие АЦП тем сильнее, чем больше амплитуда аналогового сигнала на выходе усилителей.

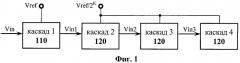

Наиболее близким к заявляемому является конвейерный АЦП, представленный в заявке на патент США №20060114141 А1, М. кл. Н03М 1/12, опубликованной 1 июня 2006 г. Описанный здесь конвейерный АЦП, приведенный на Фиг.1, включает первый каскад преобразования 110, работающий с опорным напряжением Vref, и последующие каскады преобразования 120, работающие с меньшим дифференциальным опорным напряжением Vref2 равным Vref/2K, где К - целое число.

Здесь и далее термин «дифференциальное опорное напряжение» обозначает напряжение между двумя не нулевыми опорными уровнями, в отличие от опорного напряжения, формируемого одним опорным уровнем относительно нуля.

Как видно из диаграммы опорных напряжений и масштаба аналогового сигнала в каскадах АЦП, приведенной на Фиг.2, синфазный уровень Vcm опорного напряжения остается без изменения для всех каскадов АЦП.

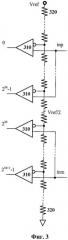

Первый каскад известного АЦП включает М-разрядный параллельный АЦП с дифференциальным входом из 2M+1 компараторов 310 и резисторов 320, приведенный на Фиг.3, и схему выборки входного сигнала, совмещенную с вычитателем-умножителем, на переключаемых конденсаторах с дифференциальным операционным усилителем 410, приведенную на Фиг.4. Схема выборки и вычитателя-умножителя выполняет функции выборки входного сигнала, М-разрядного цифроаналогового преобразователя (ЦАП), формирования остаточной разности входного сигнала и ближайшего из 2M опорных уровней ЦАП, кратных Vref/2M, и умножения остаточной разности на фактор F, равный 2M-K. Дифференциальное опорное напряжение Vret2 для второго и последующих каскадов формируется из Vref без изменения его синфазного уровня (равного Vref/2) емкостным делителем на переключаемых конденсаторах в ЦАП соответствующего каскада. Как видно из Фиг.4, схема выборки и вычитателя-умножителя включает 2M блоков 420 переключаемых конденсаторов выборки входного сигнала и формирования остаточной разности, поэтому ее реализация требует большой площади кристалла, поскольку емкости и соответственно размеры конденсаторов в первом каскаде преобразования должны быть достаточно большими для обеспечения точности АЦП. Кроме того, выборка входного сигнала разными блоками переключаемых конденсаторов приводит к дополнительным ошибкам преобразования АЦП из-за неодновременности моментов выборки переменного сигнала, связанной с рассогласованием постоянных времени заряда конденсаторов выборки 441, 442 через сопротивления ключей (431, 434, 436) в разных блоках. Эта ошибка может быть достаточно велика, поскольку сопротивления транзисторов ключей, в отличие от емкости конденсаторов, сложно согласовать с высокой точностью.

За счет уменьшения опорного напряжения для второго каскада в 2K раз коэффициент умножения умножителя остаточной разности первого каскада также уменьшается в 2K раз, при этом соответственно снижаются требования к коэффициенту усиления и частоте единичного усиления операционного усилителя умножителя. Кроме того, меньшая в 2K раз амплитуда сигналов на выходе первого каскада позволяет повысить быстродействие АЦП и за счет уменьшения времени установления напряжения на выходе умножителя.

Таким образом, основными недостатками описанного АЦП являются следующие:

- сохраняется умножение выходного сигнала первого каскада в 2M/2K, хотя и с меньшим коэффициентом умножения, приводящее к ошибкам АЦП и снижению его быстродействия;

- дифференциальный входной сигнал имеет амплитуду (Vrefp-Vrefm), в два раза меньшую, чем амплитуда полного дифференциального сигнала, поскольку в используемой схеме параллельного АЦП, приведенной на Фиг.3, напряжение на входе inp не может быть ниже середины опорного напряжения, а напряжение на входе inm не может быть выше этой середины. Соответственно в два раза ухудшается отношение сигнал/шум;

- погрешность поделенного опорного напряжения Vref/2K из-за неточности отношения емкостей делителя на переключаемых конденсаторах приводит к дополнительной некорректируемой ошибке АЦП;

- схема параллельного М-разрядного АЦП с дифференциальным входом имеет 2M+1 компараторов и резисторов вместо обычно требующихся для М-разрядного параллельного АЦП 2M-1 компараторов и 2М резисторов, что увеличивает потребляемую мощность и площадь кристалла;

- увеличенная площадь кристалла и повышенная погрешность АЦП вследствие большого количества блоков переключаемых конденсаторов выборки и формирования разности;

- уменьшается только дифференциальная величина опорного напряжения без изменения его синфазного уровня Vcm, что не позволяет использовать во втором и последующих каскадах низкое напряжение питания и быстродействующие низковольтные транзисторы.

Целями настоящего изобретения является повышение быстродействия, уменьшение погрешности преобразования и потребляемой мощности быстродействующих АЦП, а также уменьшение площади кристалла АЦП.

Поставленные цели достигаются за счет архитектуры АЦП, оптимально использующей возможности современных субмикронных технологий, совмещающих в кристалле низковольтные быстродействующие и плотноупакованные МОП транзисторы с транзисторами, работающими при повышенном напряжении питания и обеспечивающими расширенный диапазон обрабатываемых сигналов.

Поставленные цели достигаются тем, что в быстродействующем АЦП, включающем М-разрядный АЦП1 с последовательным резистивным делителем и М-разрядный ЦАП, на вход которого поступает результат преобразования АЦП1, подключенные к опорному источнику Vref с синфазным уровнем Vcm, устройство выборки и хранения (УВХ) разностного сигнала входа АЦП и выходного напряжения ЦАП с коэффициентом усиления F, причем выходной сигнал УВХ поступает на вход АЦП2 с дифференциальным опорным напряжением Vref2, меньшим Vref, а выходной код АЦП2 поступает в блок цифровой коррекции ошибок АЦП1 и формирования выходного кода АЦП, М-разрядный ЦАП включает две группы ключей, коммутирующих к дифференциальным выходам ЦАП выбранную пару симметрично расположенных отводов последовательного резистивного делителя, выходные напряжения УВХ и дифференциальное опорное напряжение АЦП2 имеют синфазный уровень Vcm2, a Vref2 равно F·(Vref/2M-1), причем F не превышает 2.

В отличие от прототипа, где F должно быть равным 2M/2K или 2M·(Vref2/Vref) и может быть большим, а Vref2 равно F·(Vref/2M) и также может быть большим, суть заявляемого АЦП, помимо снижения синфазного уровня опорного напряжения АЦП2, в ограничении F на уровне не более 2, а Vref2, равного F·(Vref/2M-1), на уровне сотен милливольт.

В частном случае исполнения быстродействующего АЦП поставленные цели в еще большей степени достигаются тем, что, по крайней мере, входные каскады компараторов АЦП1, ключи ЦАП и входные ключи УВХ разностного сигнала выполнены на высоковольтных транзисторах с повышенным напряжением питания Vdd, равным или большим Vref, а, по крайней мере, цифровые схемы АЦП, усилители и компараторы УВХ разностного сигнала и АЦП2, выполнены на низковольтных транзисторах с напряжением питания Vdd2, меньшим Vdd, но не меньшим удвоенного напряжения Vref2.

Поставленные цели в частном случае исполнения быстродействующего АЦП достигаются также тем, что М-разрядные АЦП1 и ЦАП имеют общий последовательный резистивный делитель, состоящий из 2M+1 идентичных резисторов с (2M+1+1) отводами, при этом АЦП1 является параллельным и включает 2M компараторов, а ЦАП включает две группы по 2M+1 ключей, коммутирующих к дифференциальным выходам ЦАП по одному из симметрично расположенных нечетных отводов общего резистивного делителя, причем дифференциальные опорные входы каждого компаратора подключены к двум симметрично расположенным четным отводам резистивного делителя.

В отличие от прототипа в предлагаемом АЦП1 количество компараторов уменьшено в 2 раза, а диапазон входного дифференциального сигнала увеличен в 2 раза и составляет 2Vref.

Поставленные цели в другом частном случае исполнения быстродействующего АЦП достигаются при дополнительном уменьшении потребляемой мощности и площади кристалла тем, что М-разрядные АЦП1 и ЦАП имеют общий последовательный резистивный делитель, состоящий из 2M+1 идентичных резисторов с (2M+1+1) отводами, при этом АЦП1 является последовательно-параллельным и включает компаратор одноразрядного предварительного преобразования, определяющий полярность входного дифференциального сигнала, и 2M-1 компараторов, а ЦАП включает две группы по (2M+1) ключей, коммутирующих к дифференциальным выходам ЦАП по одному из симметрично расположенных нечетных отводов общего резистивного делителя, причем дифференциальные опорные входы каждого из 2M-1 компараторов подключают прямо или инверсно к двум симметрично расположенным четным отводам резистивного делителя двумя парами ключей, управляемыми состоянием выхода компаратора предварительного преобразования.

Поставленная цель уменьшения погрешности преобразования быстродействующего АЦП достигается также тем, что схемы выборки входного дифференциального сигнала компараторов АЦП1 выполнены на переключаемых конденсаторах и подобны схеме входов устройства выборки и хранения разностного сигнала с уменьшением емкостей конденсаторов выборки и хранения и пропорциональным увеличением сопротивлений ключевых МОП транзисторов выборки.

Поставленные цели в частном случае исполнения быстродействующего АЦП достигаются тем, что АЦП2 имеет разрядность (N-M+1), где N-разрядность АЦП, выполнен по конвейерной архитектуре и содержит (N-M-1) RSD (Redundant Signed Digit) каскадов с избыточным кодом, включающих пару компараторов и схему на переключаемых конденсаторах с дифференциальным усилителем, выполняющую функции выборки входного сигнала каскада и умножающего ЦАП с напряжениями на дифференциальных входах и выходах с синфазным уровнем Vcm2 и диапазоном изменения от (Vcm2-Vref2/2) до (Vcm2+Vref2/2), а последний каскад параллельного 2-разрядного преобразования выполнен на 3 компараторах.

Поставленные цели в частном случае исполнения быстродействующего АЦП достигаются тем, что при разрядности АЦП не более 12, Vdd2=1.2 В и Vref=2 В выбирают Vcm2, равный четверти Vref, и М не менее 3, так чтобы обеспечить Vref2 не более 0.5 В при единичном усилении устройства выборки и хранения разностного сигнала АЦП2.

Поставленные цели в другом частном случае исполнения быстродействующего АЦП достигаются тем, что при разрядности АЦП, большей или равной 12, Vdd2=1.2 В и Vref=2 В выбирают Vcm2, равный четверти Vref, и М не менее 4, так чтобы обеспечить Vref2 не более 0.5 В при двукратном усилении устройства выборки и хранения разностного сигнала АЦП2.

Поставленные цели уменьшения площади кристалла и потребляемой мощности в частном случае исполнения быстродействующего АЦП достигаются тем, что отводы последовательного резистивного делителя АЦП1 с напряжениями Vcm2, равным (Vref/2M-P), где Р - целое число, меньшее М-1, (Vcm2-Vref2/2) и (Vcm2+Vref2/2) и подключенными к ним фильтрующими конденсаторами являются соответственно синфазным сm2, положительным refp2 и отрицательным refm2 выходами источника дифференциального опорного напряжения АЦП2.

Поставленная цель уменьшения погрешности преобразования в другом частном случае исполнения быстродействующего АЦП достигается тем, что источник дифференциального опорного напряжения АЦП2 включает буферные усилители, входы которых подключены к отводам последовательного резистивного делителя АЦП1 с напряжением Vcm2, равным (Vref/2M-P), где Р - целое число, меньшее М-1, (Vcm2-Vref2/2) и (Vcm2+Vref2/2), а выходы являются соответственно синфазным сm2, положительным refp2 и отрицательным refm2 выходами источника дифференциального опорного напряжения АЦП2.

Поставленная цель уменьшения погрешности преобразования в третьем частном случае исполнения быстродействующего АЦП достигается тем, что источник дифференциального опорного напряжения АЦП2 включает буферный усилитель с входом, подключенным к отводу последовательного резистивного делителя АЦП1 с напряжением 2Vcm2, равным (Vref/2M-P-1), где Р - целое число, меньшее М-1, выход которого является положительным refp2 выходом источника, буферный усилитель с входом, подключенным к отводу резистивного делителя с напряжением Vcm2, равным (Vref/2M-P), выход которого является синфазным сm2 выходом источника, а отрицательным refm2 выходом источника является отрицательный вывод источника Vref, причем напряжение 2Vcm2 дифференциального выхода источника приводят к требуемому опорному напряжению Vref2 делением на (2P/F) переключаемыми конденсаторами.

Поставленные цели уменьшения погрешности преобразования, потребляемой мощности и площади кристалла в четвертом частном случае исполнения быстродействующего АЦП достигаются тем, что источник дифференциального опорного напряжения АЦП2 включает отвод последовательного резистивного делителя АЦП1 с напряжением 2Vcm2, равным (Vref/2M-P), где Р - целое число, меньшее М-1, который вместе с подключенным к нему фильтрующим конденсатором является положительным refp2 выходом источника, буферный усилитель с входом, подключенным к отводу резистивного делителя с напряжением Vcm2, равным (Vref/2M-P), выход которого является синфазным сm2 выходом источника, а отрицательным refm2 выходом источника является отрицательный вывод источника Vref, причем напряжение 2Vcm2 дифференциального выхода источника приводят к требуемому опорному напряжению Vref2 делением на (2P/F) переключаемыми конденсаторами.

Поставленная цель уменьшения погрешности преобразования в частных случаях исполнения быстродействующего АЦП с источником дифференциального опорного напряжения АЦП2, использующим, по крайней мере, один буферный усилитель, достигается тем, что источник дифференциального опорного напряжения АЦП2 включает схему калибровки выходного напряжения подстройкой напряжения смещения буферного усилителя одного из дифференциальных выходов опорного источника АЦП2.

Поставленная цель уменьшения погрешности преобразования в частном случае исполнения быстродействующего АЦП с калибровкой источника дифференциального опорного напряжения АЦП2 достигается тем, что схема калибровки дифференциального опорного напряжения АЦП2 включает компаратор калибровки, сравнивающий остаточное напряжение на выходе последнего RSD каскада АЦП2 с напряжением Vref2, ключи, подключающие к дифференциальным входам устройства выборки и хранения разностного сигнала, по крайней мере, одну пару отводов резистивного делителя АЦП1 с дифференциальным напряжением, кратным Vref2, а к дифференциальным выходам ЦАП, по крайней мере, одну пару отводов резистивного делителя с дифференциальным напряжением, на Vref2 меньшим, калибровочный ЦАП, управляющий смещением нуля буферного усилителя источника опорного напряжения АЦП2 и блок управления калибровкой.

Поставленная цель уменьшения погрешности преобразования быстродействующего АЦП в частном случае исполнения быстродействующего АЦП с калибровкой дифференциального источника опорного напряжения АЦП2 достигается также способом калибровки, при котором к дифференциальным входам устройства выборки и хранения разностного сигнала подключают пару отводов резистивного делителя АЦП1 с дифференциальным напряжением, кратным Vref2, а к дифференциальным выходам ЦАП пару отводов с дифференциальным напряжением, на Vref2 меньшим, проводят выборку и аналого-цифровое преобразование входного сигнала, проводят методом последовательного приближения калибровочным ЦАП подстройку смещения нуля буферного усилителя опорного источника АЦП2 до достижения минимальной разности дифференциального напряжения на выходе последнего RSD каскада и напряжения Vref2, фиксируемой компаратором калибровки, и запоминают цифровой код калибровочного ЦАП.

Поставленная цель уменьшения погрешности преобразования быстродействующего АЦП в другом частном случае исполнения быстродействующего АЦП с калибровкой источника опорного напряжения АЦП2 достигается в большей степени усложненным способом калибровки, при котором проводят калибровки для двух или более пар дифференциальных входных напряжений с разными амплитудами, причем дифференциальные входные напряжения каждой пары имеют одинаковые амплитуды и противоположные полярности, определяют средний цифровой код из цифровых кодов калибровочного ЦАП для каждого дифференциального входного напряжения и подают полученный средний цифровой код на вход калибровочного ЦАП.

Поставленная цель уменьшения погрешности преобразования быстродействующего АЦП в третьем частном случае исполнения быстродействующего АЦП с калибровкой источника опорного напряжения АЦП2 достигается также в большей степени другим усложненным способом калибровки, при котором проводят калибровки для двух или более пар дифференциальных входных напряжений с разными амплитудами, причем дифференциальные входные напряжения каждой пары имеют одинаковые амплитуды и противоположные полярности, определяют средний цифровой код всех цифровых кодов калибровочного ЦАП для каждого дифференциального входного напряжения и подают полученный средний цифровой код на вход калибровочного ЦАП.

Сущность изобретения поясняется чертежами.

На Фиг.1 представлена блок схема известного многокаскадного АЦП, наиболее близкого заявляемому.

На Фиг.2 представлены диаграммы опорных напряжений и масштабов аналогового сигнала в каскадах известного АЦП, наиболее близкого заявляемому.

На Фиг.3 представлена структурная схема М-разрядного параллельного АЦП1 с дифференциальным входом, используемая в известном многокаскадном АЦП, наиболее близком заявляемому.

На Фиг.4 представлена схема выборки и вычитателя-умножителя, используемая в известном многокаскадном АЦП, наиболее близком заявляемому.

На Фиг.5а и 5b представлены упрощенные блок-схемы заявляемого быстродействующего АЦП по п.1 и 2 Формулы соответственно.

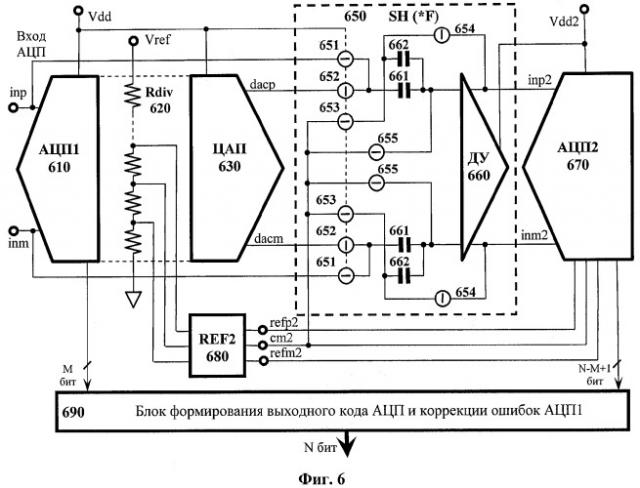

На Фиг.6 представлена детализированная схема заявляемого быстродействующего АЦП по п.2 Формулы.

На Фиг.7 представлены диаграммы напряжений питания, опорных напряжений и амплитуды напряжений аналоговых сигналов в заявляемом АЦП по п.1 (Фиг.7а), п.2 (Фиг.7b) и п.8, 9 (Фиг.7с) Формулы.

На Фиг.8а и 8b представлены структурные схемы М-разрядного параллельного АЦП1 с дифференциальным входом и М-разрядного дифференциального ЦАП с общим последовательным резистивным делителем, используемые в заявляемом АЦП по п.3 и 4 Формулы.

На Фиг.9 представлены примеры реализации УВХ разностного сигнала входа АЦП и выходного напряжения ЦАП с однократной (Фиг.9а) и двойной (Фиг.9b) выборкой входного сигнала за период тактового сигнала.

На Фиг.10 представлены структурные схемы выборки входного дифференциального сигнала компараторов АЦП1 и УВХ разностного сигнала входа АЦП и выходного напряжения ЦАП, используемые в заявляемом АЦП по п.5 Формулы.

На Фиг.11 представлена блок схема конвейерного АЦП2, используемая в заявляемом АЦП по п.6 Формулы.

На Фиг.12 представлен пример структурной схемы дифференциального RSD каскада конвейерного АЦП2, используемого в заявляемом АЦП по п.6 Формулы.

На Фиг.13 представлены схемы вариантов источников опорного напряжения АЦП2, используемые в заявляемом АЦП по п.9 (Фиг.13а), п.10 (Фиг.13b), п.11 (Фиг.13с) и п.12 (Фиг.13d) Формулы.

На Фиг.14 представлена структурная схема калибровки опорного напряжения АЦП2, используемая в заявляемом АЦП по п.14 Формулы.

Ниже, на примере чертежей, приведено описание устройства и работы заявляемого быстродействующего АЦП.

На Фиг.5а представлена блок схема заявляемого АЦП по п.1 Формулы. Дифференциальный входной сигнал 501 с синфазным уровнем Vcm=Vref/2 и диапазоном изменения от 0 до Vref на каждом входе (диапазон дифференциального сигнала 2Vref) одновременно поступает на входы АЦП1 510 и устройства 520 (SH) выборки и формирования разностного сигнала входа АЦП1 и выходного напряжения ЦАП 520. Отметим, что при необходимости смещения диапазона изменения входного сигнала опорное напряжение Vref может отсчитываться не только от нуля, но и от любого другого потенциала, при этом уровень Vcm отсчитывается от уровня с более низким потенциалом.

АЦП1, подключенный к источнику опорного напряжения Vref, производит быстрое аналого-цифровое преобразование входного сигнала и определяет М старших разрядов выходного кода АЦП. Результат преобразования АЦП1 поступает на вход М-разрядного ЦАП 520, формирующего на своем дифференциальном выходе 521 ближайшее, меньшее входного сигнала напряжение одного из 2M опорных уровней, кратных Vref/2M, или 0. УВХ формирует на своем дифференциальном выходе 531 напряжение, равное усиленной с коэффициентом F разности входного сигнала АЦП и выходного напряжения ЦАП. При этом диапазон выходных напряжений УВХ Vref2, равный F·(Vref/2M-1), и их синфазный уровень Vcm2 уменьшены относительно диапазона входного сигнала АЦП Vref и его синфазного уровня Vcm так, чтобы обеспечить оптимальные условия работы усилителей УВХ и АЦП2. Так как при входных и выходных напряжениях усилителей, близких к напряжениям земли и питания, коэффициент усиления усилителей и их быстродействие ухудшаются, выбором Vcm2, М и F задают диапазон выходных напряжений УВХ, равный (Vcm2+/-Vref2/2), с необходимыми запасами относительно уровней земли и питания Vdd2 усилителей устройства выборки и АЦП2. При этом коэффициент усиления F устройства выборки SH ограничивают на уровне не более 2 для снижения требований к коэффициенту усиления и быстродействию усилителя УВХ, и, таким образом, величина дифференциального опорного напряжения Vref2 не превышает 2(Vref/2M-1).

На Фиг.5b представлена блок схема заявляемого АЦП по п.2 Формулы.

Отличие этого АЦП в том, что помимо основного напряжения питания Vdd2, которое далее будем называть низким, используется и повышенное напряжение питания Vdd. Наличие второго источника питания Vdd с повышенным напряжением позволяет, наряду с оптимальным диапазоном аналоговых сигналов в пределах половины низкого напряжения питания Vdd2, увеличивать Vref и соответственно диапазон входного аналогового сигнала АЦП, вплоть до величины высокого напряжения питания Vdd. Соответственно увеличивается и динамический диапазон АЦП, определяемый отношением сигнал/шум. При этом появляется возможность оптимального использования низковольтных и высоковольтных транзисторов, предоставляемых современными технологиями.

Подробно устройство и работу быстродействующего АЦП, заявляемого по п.2 Формулы, рассмотрим на примере детализированной структурной схемы АЦП, представленной на Фиг.6.

Заявляемый быстродействующий АЦП включает М-разрядный АЦП1 610 с последовательным резистивным делителем Rdiv 620, подключенным к источнику опорного напряжения Vref, и дифференциальным входом (inp, inm), подключенным к аналоговому входу АЦП. АЦП1 производит быстрое аналого-цифровое преобразование входного напряжения и определяет М старших разрядов выходного кода АЦП с допустимой ошибкой преобразования до плюс/минус (Vref/2M+1), исправляемой последующей цифровой коррекцией по результату преобразования младших разрядов в АЦП2 670. Результат М-разрядного преобразования АЦП1 поступает на вход М-разрядного ЦАП 630, формирующего на дифференциальном выходе ближайшее меньшее входного сигнала напряжение одного из 2М опорных уровней, кратных Vref/2M, или 0. Входной сигнал АЦП одновременно с входом АЦП1 поступает на дифференциальный вход УВХ разностного сигнала входа АЦП и выходного напряжения ЦАП 650 (SH) на переключаемых конденсаторах с дифференциальным усилителем 660 (ДУ).

УВХ имеет две фазы работы. В фазе выборки ключи 651, 653, 655 находятся в проводящем состоянии, а ключи 652, 654 в запертом состоянии и напряжение входного сигнала АЦП запоминается на конденсаторах 661 в момент размыкания ключей 653 при переходе в фазу хранения. В фазе хранения ключи 651, 653, 655 находятся в запертом состоянии, а ключи 652, 654 в проводящем состоянии, и выходное напряжение ЦАП вычитается из напряжения входного сигнала АЦП на конденсаторах 661. Низковольтный усилитель 660 с конденсаторами обратной связи 662 формирует на своих выходах низковольтный аналоговый сигнал, соответствующий умноженному на F (1 или 2) разностному сигналу входа АЦП и выходного напряжения ЦАП, с синфазным уровнем Vcm2 и диапазоном изменения напряжений на выходах Vref2. При этом Vcm2 и Vref2 не превышают величины Vdd2/2, a Vref2 равно Vref/2M-1 при единичном (F=1) усилении устройства выборки. Низковольтный дифференциальный выходной сигнал устройства выборки поступает на входы inp2 и inm2 (N-M+1) разрядного АЦП2 670 с низким напряжением питания Vdd2 и пониженнным дифференциальным опорным напряжением Vref2. Источник опорного напряжения REF2 680 с входами, подключенными к последовательному резистивному делителю АЦП1 620, формирует на выходе сm2 пониженнное напряжение синфазного уровня Vcm2, а на выходах refp2, refm2 пониженнное дифференциальное опорное напряжение для АЦП2. (N-M+1) разрядный выходной код АЦП2 и М-разрядный выходной код АЦП1 поступают в блок 690 цифровой коррекции ошибок АЦП1 и формирования выходного кода АЦП, корректирующий за счет избыточного разряда М-разрядный выходной код АЦП1 и вырабатывающий N-разрядный выходной код АЦП.

Как видно из приведенного описания, схемы обработки входного сигнала АЦП1 (по крайней мере, входные каскады компараторов со схемами выборки входного сигнала) и выходного сигнала ЦАП (по крайней мере, выходные ключи ЦАП) и, по крайней мере, входные ключи УВХ обрабатывают напряжение в диапазоне Vref, которое задают возможно более высоким для обеспечения максимального отношения сигнал/шум. В пределе напряжение Vref и диапазон входного аналогового сигнала АЦП может быть равен напряжению повышенного питания Vdd блоков АЦП1, ЦАП и SH, так как КМОП аналоговые ключи и входные каскады компараторов, в отличие от схем прецизионных операционных усилителей, эффективно обрабатывают аналоговый сигнал в диапазоне их напряжения питания.

Ключи выборки входного сигнала 655, цепей обратной связи усилителя 654 и сам усилитель 660 блока SH, а также усилители и компараторы АЦП2 обрабатывают уже низковольтный аналоговый сигнал в диапазоне от (Vcm2-Vref2/2) до (Vcm2+Vref2/2) (например, согласно п.2 Формулы от Vdd2/4 до 3Vdd2/4), что обеспечивает оптимальный диапазон обрабатываемого сигнала прецизионных усилителей УВХ и АЦП2, выполненных на низковольтных транзисторах, с присущим им повышенным быстродействием и уменьшенной потребляемой мощностью при низком напряжении питания Vdd2. Также работа усилителей в оптимальном диапазоне выходных напряжений уменьшает ошибки выходного сигнала относительно диапазона входного сигнала АЦП и снижает погрешность АЦП.

Использование низковольтной элементной базы для большей части аналоговых блоков АЦП вместо высоковольтной обеспечивает существенное уменьшение площади кристалла АЦП.

Отметим, что, хотя ключи УВХ 655 и все ключи АЦП2 работают уже с низким уровнем сигнала, для снижения их сопротивления может использоваться высокое напряжение питания. При этом увеличится разность между напряжением питания и пороговым напряжением относительно пониженного напряжения синфазного уровня Vcm2 для более быстродействующих N-МОП транзисторов ключей, поэтому для экономии площади целесообразно использовать в ключах только N-МОП транзисторы.

На Фиг.7 представлена диаграмма напряжений питания, опорных напряжений и амплитуды напряжений аналоговых сигналов в заявляемом АЦП по п.1 (Фиг.7а), п.2 (Фиг.7b) и п.8, 9 (Фиг.7с) Формулы. Диаграммы показывают уменьшение низковольтного дифференциального опорного напряжения Vref2 и амплитуды напряжений аналоговых сигналов Vinp2, Vinm2 на выходе УВХ в (2M-1/F) раз (в 8 раз для М=4, F=1), а также уменьшение синфазного уровня опорного напряжения в 2 раза для М=4.

Так как УВХ (SH) и АЦП2 обрабатывают аналоговый сигнал, уменьшенный в (2M-1/F) раз по отношению к входному сигналу АЦП, то влияние ошибок отношения емкостей переключаемых конденсаторов этих блоков и их шумов на погрешность АЦП также уменьшается в (2M-1/F) раз. Последнее позволяет уменьшить номиналы емкостей конденсаторов и соответственно повысить быстродействие и уменьшить погрешность преобразования АЦП, а также уменьшить площадь его кристалла.

Также уменьшенный диапазон напряжений аналоговых сигналов УВХ и АЦП2 существенно уменьшает время установления выходных напряжений усилителей и соответственно снижает требования к их коэффициентам усиления, что повышает быстродействие АЦП и снижает погрешности преобразования.

На Фиг.8а представлена структурная схема М-разрядного параллельного АЦП1 с дифференциальным входом и М-разрядного дифференциального ЦАП с общим последовательным резистивным делителем, используемая в заявляемом АЦП согласно п.3 Формулы.

Здесь общий последовательный резистивный делитель 820, подключенный к источнику опорного напряжения Vref, состоит из 2M+1 идентичных резисторов от 821-1 до 821-2M+1 с (2M+1+1) отводами. Параллельный АЦП1 810 включает 2M компараторов от 811-1 до 811-2M со схемами выборки входного дифференциального сигнала и входным дифференциальным каскадом на высоковольтных МОП транзисторах с напряжением питания Vdd. Дифференциальные опорные входы каждого компаратора подключены к двум симметрично расположенным четным отводам резистивного делителя, причем один из входов подключен к отводу от нижней, а второй вход к отводу от верхней половин делителя. Выходной код компараторов определяет отводы резистивного делителя с ближайшим дифференциальным напряжением, меньшим дифференциального входного сигнала АЦП. ЦАП 830 включает две группы по 2M+1 ключей от 831-1 до 831-2M+1 на высоковольтных МОП транзисторах с напряжением питания Vdd, коммутирующих к дифференциальным выходам ЦАП по одному из симметрично расположенных нечетных отводов резистивного делителя в соответствии с выходным кодом АЦП1. При этом на дифференциальном выходе ЦАП формируется напряжение, отличающееся от дифференциального входного напряжения АЦП не более чем на Vref/2M-1 с учетом допустимой ошибки компараторов АЦП1 плюс/минус Vref/2M+1.

Последовательный резистивный делитель ЦАП при достаточно больших размерах резисторов и специальной схеме их размещения в виде свернутой матрицы с центральной симметрией обеспечивает среднеквадратичную ошибку отношения сопротивлений пар смежных резисторов в делителе 0.1% и менее. Так как указанная ошибка отношения сопротивлений в последовательном делителе из 2M+1 резисторов приводит к аналогичной ошибке напряжения на паре смежных резисторов, составляющего 1/2M+1 часть от максимального дифференциального входного сигнала АЦП, то соответствующая ошибка интегральной или дифференциальной нелинейности АЦП будет в 2M+1 раз меньше. Таким образом, например, при М=4 интегральная или дифференциальная нелинейности АЦП из-за ошибок согласования сопротивлений резистивного делителя ЦАП составит (0.1%/2M+1) или 0.003%, что позволяет реализовать 12 и более разрядные АЦП.

Недостатком описанного параллельного М-разрядного АЦП1 является относительно большое количество компараторов, например, для М=4 требуется 16 компараторов, а для М=5 количество компараторов возрастает до 32.

На Фиг.8b представлена структурная схема М-разрядного последовательно-параллельного АЦП1 с уменьшенным количеством компараторов, используемая в заявляемом АЦП по п.4 Формулы.

Здесь также используется общий последовательный резистивный делитель 820, подключенный к источнику опорного напряжения Vref. Последовательно-параллельный АЦП1 810 включает компаратор одноразрядного предварительного преобразования на высоковольтных МОП транзисторах с напряжением питания Vdd, определяющий полярность входного дифференциального сигнала, и только 2M-1 компараторов от 811-1 до 811-2M-1 со схемами выборки входного дифференциального сигнала и входным дифференциальным каскадом на высоковольтных МОП транзисторах с напряжением питания Vdd. Дифференциальные опорные входы каждого из 2M-1 компараторов подключают прямо или инверсно к двум симметрично расположенным четным отводам резистивного делителя двумя парами ключей, управляемых сигналом выхода компаратора предварительного преобразования 815. При этом один из опорных входов подключают к отводу от нижней, а второй к отводу от верхней половин делителя.

Данная схема АЦП1 позволяет почти в два раза уменьшить требуемое количество компараторов для уменьшения площади кристалла и потребляемой мощности. Это достигается ценой небольшого увеличения времени преобразования АЦП1 за счет добавления времени срабатывания компаратора предварительного преобразования. Поскольку дополнительный компаратор допускает большую погрешность (плюс/минус Vref/2M+1), не влияющую на точность преобразования АЦП, его время срабатывания может быть существенно меньше 1 нс для современных субмикронных технологий, что и обеспечивает возможность использования такой схемы АЦП1.

Важн