Устройство и способ для кодирования/декодирования кода разреженного контроля четности с переменной длиной блока

Иллюстрации

Показать всеИзобретение относится к системе мобильной связи и, в частности, к устройству и способу для кодирования/декодирования блочного кода разреженного контроля четности (LDPC), обладающего переменной длиной. Устройство и способ включают в себя прием информационного слова и кодирование информационного слова в блочный код LDPC на основании одной из первой матрицы контроля четности и второй матрицы контроля четности в зависимости от длины, которая должна применяться при формировании информационного слова в блочный код LDPC. Технический результат - обеспечить формирование блочного кода разреженного контроля четности (LDPC), который применим к различным скоростям кодирования и обладает различными длинами блока, способствуя минимизации аппаратной сложности. 4 н. и 33 з.п. ф-лы, 17 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение, в целом, относится к системе мобильной связи и, в частности, к устройству и способу для кодирования/декодирования блочных кодов разреженного контроля четности (LDPC).

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

Из-за бурного развития систем мобильной связи необходимо развивать технологию, допускающую передачу большого количества данных с приближением к пропускной способности проводной сети даже в беспроводной среде. Чтобы удовлетворить растущие потребности в высокоскоростной высокопроизводительной системе связи, допускающей обработку и передачу различных данных, таких как данные изображения и радиосвязи, вне ориентированной на голос службы, необходимо повышать эффективность передачи системы посредством использования надлежащей схемы кодирования канала, чтобы, тем самым, улучшить эксплуатационные характеристики всей системы. Однако система мобильной связи, вследствие своих характеристик, неизбежно порождает ошибки во время передачи данных, обусловленные шумами, помехами и замиранием согласно канальным условиям. Порождение ошибок служит причиной потери большого количества информационных данных.

Для того чтобы избежать потери информационных данных, обусловленной образованием ошибок, различные схемы контроля ошибок в настоящее время применяются и, отчасти, основаны на характеристиках канала, чтобы, тем самым, улучшить надежность системы мобильной связи. Наиболее типичная схема контроля ошибок использует коды с исправлением ошибок.

Со ссылкой на фиг.1 далее будет приведено описание структуры передатчика/приемника в обычной системе мобильной связи.

Фиг.1 - схема, иллюстрирующая структуру приемника/передатчика в обычной системе мобильной связи. Со ссылкой на фиг.1, передатчик 100 включает в себя кодировщик 111, модулятор 113 и радиочастотный (РЧ) процессор 115, а приемник 150 включает в себя РЧ-процессор 151, демодулятор 153 и декодер 155.

В передатчике 100, информационные данные 'u' передачи, если сформированы, поставляются в кодировщик 111. Кодировщик 111 формирует кодированный символ 'c' посредством кодирования информационных данных 'u' в зависимости от предопределенной схемы кодирования и выводит кодированный символ 'c' в модулятор 113. Модулятор 113 формирует символ 's' модуляции посредством модуляции кодированного символа 'c' в зависимости от предопределенной схемы модуляции и выводит символ 's' модуляции в РЧ-процессор 115. РЧ-процессор 115 подвергает РЧ-обработке символ 's' модуляции, выведенный из модулятора 113, и передает подвергнутый РЧ-обработке сигнал по эфиру через антенну ANT.

Сигнал, переданный по эфиру передатчиком 100 таким образом, принимается в приемнике 150 посредством антенны ANT, а сигнал, принятый посредством антенны, поставляется в РЧ-процессор 151. РЧ-процессор 151 подвергает РЧ-обработке принятый сигнал и выводит подвергнутый РЧ-обработке сигнал 'r' в демодулятор 153. Демодулятор 153 демодулирует подвергнутый РЧ-обработке сигнал 'r', выведенный из РЧ-процессора 151, с использованием схемы демодуляции, соответствующей схеме модуляции, применяемой в модуляторе 113, и выводит демодулированный сигнал 'x' в декодер 155. Декодер 155 декодирует демодулированный сигнал 'x', выведенный из демодулятора 153, с использованием схемы декодирования, соответствующей схеме кодирования, примененной в кодировщике 111, и выводит декодированный сигнал '' в качестве окончательно декодированных информационных данных.

Для того чтобы приемнику 150 без ошибок декодировать информационные данные 'u', переданные передатчиком 100, есть потребность в высокопроизводительном кодировщике и декодере. В частности, так как среда радиоканала должна приниматься во внимание из-за характеристик системы мобильной связи, ошибки, которые могут порождаться вследствие среды радиоканала, должны учитываться более серьезно.

Наиболее типичные коды исправления ошибок включают в себя турбокоды и коды разреженного контроля четности (LDPC).

Хорошо известно, что турбокоды являются превосходящими по производительности по отношению к сверточному коду, который традиционно используется для исправления ошибок во время высокоскоростной передачи данных. Турбокод является преимущественным в том, что он может эффективно исправлять ошибки, вызванные шумами, порожденными в канале передачи, тем самым повышая надежность передачи данных. Код LDPC может декодироваться с использованием итерационного алгоритма декодирования, основанного на алгоритме суммы-произведения в факторном графе. Так как декодер для кода LDPC использует основанный на алгоритме суммы-произведения итерационный алгоритм декодирования, он является менее сложным, чем декодер для турбокода. В дополнение, декодер для кода LDPC легок для реализации декодера параллельной обработки в сравнении с декодером для турбокода.

Теорема Шеннона кодирования канала иллюстрирует, что надежная связь возможна только при скорости передачи данных, не превышающей пропускную способность канала. Однако теорема Шеннона кодирования канала не предложила никакого детализированного способа кодирования/декодирования для поддержания скорости передачи данных вплоть до предела максимальной пропускной способности канала. Вообще, несмотря на то, что случайный код, обладающий очень большим размером блока, демонстрирует быстродействие, приближающееся к пределу пропускной способности канала по теореме Шеннона кодирования канала, когда используется способ декодирования MAP (с максимумом апостериорной вероятности) или ML (максимальной достоверностью), фактически невозможно реализовать способ декодирования вследствие его тяжелой вычислительной нагрузки.

Турбокод был предложен Берроу, Главиуксом и Титимаджимой в 1993 году и демонстрирует превосходное быстродействие, которое приближается к пределу пропускной способности канала по теореме Шеннона кодирования канала. Предложение турбокода дало начало активным исследованиям по итерационному декодированию и графическому представлению кодов, и коды LDPC, предложенные Галагером в 1962 году, были вновь выдвинуты на первый план в исследованиях. В факторном графе турбокода и кода LDPC существуют циклы, и хорошо известно, что итерационное кодирование в факторном графе кода LDPC, где существуют циклы, является квазиоптимальным. К тому же, было экспериментально доказано, что код LDPC обладает прекрасным быстродействием, благодаря итерационному декодированию. Код LDPC, известный как обладающий наивысшей производительностью, всегда демонстрирует рабочие характеристики, имеющие различие всего лишь в приблизительно 0,04 [дБ] с пределом пропускной способности канала по теореме Шеннона кодирования канала при частоте двоичных ошибок (BER) 10-5, с использованием размера блока 107. В дополнение, несмотря на то, что код LDPC, определенный на поле Галуа (GF) с q > 2, то есть GF(q), возрастает по сложности в последовательности операций его декодирования, он является гораздо лучшим по быстродействию по отношению к двоичному коду. Однако нет удовлетворительного теоретического описания успешного кодирования посредством алгоритма итерационного декодирования для кода LDPC, определенного на GF(q).

Код LDPC, предложенный Галагером, определен матрицей контроля четности, в которой большинство элементов имеют значение 0, и меньшинство элементов, кроме элементов, имеющих значение 0, имеют ненулевое значение, например, значение 1. В последующем описании будет принято, что ненулевым значением является значение 1.

Например, код LDPC (N, j, k) является линейным блочным кодом, имеющим длину блока N, и определен матрицей разреженного контроля четности, в которой каждый столбец содержит j элементов, имеющих значение 1, каждая строка содержит k элементов, имеющих значение 1, а все из элементов, кроме элементов, имеющих значение 1, имеют значение 0.

Код LDPC, в котором вес каждого столбца в матрице контроля четности установлен в 'j', а вес каждой строки в матрице контроля четности установлен в 'k', как описано выше, назван «регулярным кодом LDPC». Здесь «вес» относится к количеству элементов, обладающих ненулевым значением, среди элементов, составляющих матрицу контроля четности. В отличие от регулярного кода LDPC, код LDPC, в котором вес каждого столбца в матрице контроля четности и вес каждой строки в матрице контроля четности не зафиксированы, назван «нерегулярным кодом LDPC». Широко известно, что нерегулярный код LDPC является превосходным по быстродействию по отношению к регулярному коду LDPC. Однако в случае нерегулярного кода LDPC, так как вес каждого столбца и вес каждой строки в матрице контроля четности непостоянны, то есть являются нерегулярными, вес каждого столбца в матрице контроля четности и вес каждой строки в матрице контроля четности должны настраиваться надлежащим образом для того, чтобы гарантировать лучшее быстродействие.

Со ссылкой на фиг.2 далее будет приведено описание матрицы контроля четности кода LDPC (8, 2, 4) в качестве примера кода LDPC (N, j, k).

Фиг.2 иллюстрирует матрицу контроля четности обычного кода LDPC (8, 2, 4). Со ссылкой на фиг.2 матрица H контроля четности кода LDPC (8, 2,4) составлена из 8 столбцов и 4 строк, при этом вес каждого столбца установлен в 2, а вес каждой строки установлен в 4. Так как вес каждого столбца и вес каждой строки в матрице контроля четности являются постоянными, как изложено выше, код LDPC (8, 2, 4), проиллюстрированный на фиг.2, становится регулярным кодом.

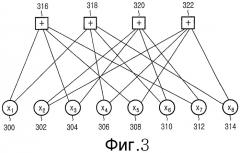

До сих пор, со ссылкой на фиг.2, описывалась матрица контроля четности кода LDPC (8, 2, 4). Затем, далее в материалах настоящей заявки, со ссылкой на фиг.3 будет описан факторный граф кода LDPC (8, 2, 4), описанного в связи с фиг.2.

Фиг.3 - схема, иллюстрирующая факторный граф кода LDPC (8, 2, 4) по фиг.2. Со ссылкой на фиг.3 факторный граф кода LDPC (8, 2, 4) составлен из 8 узлов переменных x1 300, x2 302, x3 304, x4 306, x5 308, x6 310, x7 312 и x8 314 и 4-х узлов 316, 318, 320 и 322 контроля. Когда элемент, имеющий значение 1, то есть ненулевое значение, существует в точке, где пересекаются друг с другом j-й столбец и i-я строка матрицы контроля четности кода LDPC (8, 2, 4), создана ветвь между узлом xi переменной и j-м узлом контроля.

Так как матрица контроля четности кода LDPC имеет небольшой вес, как описано выше, возможно выполнять декодирование посредством итерационного декодирования даже в блочном коде, обладающем относительно большой длиной, который демонстрирует производительность, приближающуюся к пределу пропускной способности по теореме Шеннона кодирования канала, таком как турбокод, при постоянном росте длины блока блочного кода. Маккей и Нил доказали, что процесс итерационного декодирования кода LDPC с использованием схемы потоковой передачи приближается по производительности к процессу итерационного декодирования турбокода.

Для того чтобы сформировать высокопроизводительный код LDPC, должны быть удовлетворены следующие условия.

(1) Должны приниматься во внимание циклы в факторном графе кода LDPC.

Термин «цикл» относится к замкнутой цепи, сформированной ребрами, присоединяющими узлы переменных к узлам контроля в факторном графе кода LDPC, а длина цикла определена как количество ребер, составляющих замкнутую цепь. Длинный цикл означает, что количество ребер, присоединяющих узлы переменных к узлам контроля, составляющих замкнутую цепь в факторном графе кода LDPC, является большим. В противоположность, короткий цикл означает, что количество ребер, присоединяющих узлы переменных к узлам контроля, составляющих замкнутую цепь в факторном графе кода LDPC, является небольшим.

В то время как циклы в факторном графе кода LDPC становятся длиннее, относительный уровень производительности кода LDPC возрастает по следующим причинам. То есть когда формируются длинные циклы в факторном графе кода LDPC, возможно избежать ухудшения эксплуатационных показателей, таких как минимальный уровень ошибок, возникающих, когда слишком много циклов с короткой длиной существует в факторном графе кода LDPC.

(2) Должно приниматься во внимание эффективное кодирование кода LDPC.

Для кода LDPC является затруднительным подвергаться кодированию в реальном времени в сравнении со сверточным кодом или турбокодом вследствие высокой сложности его кодирования. Для того чтобы уменьшить сложность кодирования кода LDPC, был предложен код с повторным накоплением (RA). Однако код RA также имеет предел в снижении сложности кодирования кода LDPC. Поэтому эффективное кодирование кода LDPC должно приниматься во внимание.

(3) Должно приниматься во внимание распределение степеней в факторном графе кода LDPC.

Вообще, нерегулярный код LDPC является превосходным по производительности по отношению к регулярному LDPC, так как факторный граф нерегулярного кода LDPC содержит различные степени. Термин «степень» относится к количеству ребер, присоединенных к узлам переменных и узлам контроля, в факторном графе кода LDPC. Кроме того, фраза «распределение степеней» по факторному графу кода LDPC относится к отношению количества узлов, имеющих конкретную степень, к общему количеству узлов. Ричардсоном было доказано, что код LDPC, обладающий конкретным распределением степеней, является лучшим по производительности.

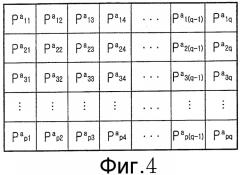

Со ссылкой на фиг.4, далее будет приведено описание матрицы контроля четности блочного кода LDPC.

Фиг.4 - таблица, иллюстрирующая матрицу контроля четности обычного блочного кода LDPC. До того, как дано описание по фиг.4, должно быть отмечено, что блочный код LDPC является новым кодом LDPC, для которого принималось во внимание не только эффективное кодирование, но также и эффективное хранение и улучшение производительности матрицы контроля четности, и блочный код LDPC является кодом LDPC, расширенным посредством обобщения структуры регулярного кода LDPC. Со ссылкой на фиг.4, матрица контроля четности блочного кода LDPC разделена на множество частичных блоков, и матрица перестановок внесена в каждый из частичных блоков. На фиг.4 'P' представляет матрицу перестановок, имеющую размер Ns ×Ns, а верхним индексом (или показателем) apq матрицы P перестановок является 0 ≤ apq ≤ Ns - 1, либо apq = ∞.

В дополнение, 'p' указывает, что соответствующая матрица перестановок расположена в p-й строке частичных блоков матрицы контроля четности, а 'q' указывает, что соответствующая матрица перестановок расположена в q-м столбце частичных блоков матрицы контроля четности. То есть представляет матрицу перестановок, расположенную в частичном блоке, где пересекаются друг с другом p-я строка и q-й столбец матрицы контроля четности, составленной из множества частичных блоков. То есть 'p' и 'q' представляют, соответственно, количество строк и количество столбцов частичных блоков, соответствующих информационной части в матрице контроля четности.

Далее со ссылкой на фиг.5 будет описана матрица перестановок.

Фиг.5 иллюстрирует матрицу P перестановок по фиг.4. Как проиллюстрировано на фиг.5, матрицей P перестановок является квадратная матрица, имеющая размер Ns ×Ns, и каждый из Ns столбцов, составляющих матрицу P перестановок, имеет вес 1, а каждая из Ns строк, составляющих матрицу P перестановок, также имеет вес 1. В материалах настоящей заявки, хотя размер матрицы P перестановок представлен как Ns ×Ns, он также будет выражаться как Ns, так как матрица P перестановок является квадратной матрицей.

На фиг.4 матрица P перестановок с верхним индексом apq =0, то есть матрица P0 перестановок представляет единичную матрицу , а матрица P перестановок с верхним индексом apq =∞, то есть матрица P∞ перестановок, представляет нулевую матрицу. Здесь представляет единичную матрицу с размером Ns ×Ns.

В полной матрице контроля четности блочного кода LDPC, проиллюстрированной на фиг.4, так как общим количеством строк является Ns ×p, а общим количеством столбцов является Ns ×q (для p≤q), когда полная матрица контроля четности кода LDPC имеет полный ранг, скорость кодирования может быть выражена в виде равенства (1), независимо от размера частичных блоков.

(1)

Если apq ≠∞ для p и q, матрицы перестановок, соответствующие частичным блокам, не являются нулевыми матрицами, а частичные блоки составляют регулярный код LDPC, в котором значением веса каждого столбца и значением веса каждой строки в каждой из матриц перестановок, соответствующих частичным блокам, являются p и q, соответственно. В материалах настоящей заявки каждая из матриц перестановок, соответствующих частичным блокам, будет упоминаться ссылкой как «частичная матрица».

Так как существуют (p - 1) независимых строк в полной матрице контроля четности, скорость кодирования является большей, чем скорость кодирования, вычисленная согласно равенству (1). В случае блочного кода LDPC, если весовая позиция первой строки каждой из частичных матриц, составляющих полную матрицу контроля четности, определена, могут быть определены весовые позиции оставшихся (Ns - 1) строк. Поэтому требуемый размер памяти снижен до 1/Ns, по сравнению со случаем, где веса выбраны нерегулярно, для хранения информации по полной матрице контроля четности.

Как описано выше, термин «цикл» относится к замкнутой цепи, сформированной ребрами, присоединяющими узлы переменных к узлам контроля в факторном графе кода LDPC, а длина цикла определена как количество ребер, составляющих замкнутую цепь. Длинный цикл означает, что количество ребер, присоединяющих узлы переменных к узлам контроля, составляющих замкнутую цепь в факторном графе кода LDPC, является большим. В то время как циклы в факторном графе кода LDPC становятся длиннее, относительный уровень производительности кода LDPC возрастает.

В противоположность, в то время как циклы в факторном графе кода LDPC становятся короче, способность исправления ошибок кода LDPC уменьшается, так как происходит ухудшение эксплуатационных характеристик, таких как минимальный уровень ошибок. То есть когда в факторном графе кода LDPC есть много циклов с короткой длиной, информация в конкретном узле, принадлежащем циклу с короткой длиной, начинающемуся из него, возвращается после небольшого количества итераций. В то время как количество итераций возрастает, информация возвращается в соответствующий узел чаще, так что информация не может корректно обновляться, тем самым, вызывая ухудшение в способности исправления ошибок кода LDPC.

Со ссылкой на фиг.6, далее будет приведено описание циклической структуры блочного кода LDPC.

Фиг.6 - схема, иллюстрирующая циклическую структуру блочного кода LDPC, по которой матрица контроля четности составлена из 4 частичных матриц. До того, как дано описание по фиг.6, должно быть отмечено, что блочный код LDPC является новым кодом LDPC, для которого были продуманы не только эффективное кодирование, но также и эффективное хранение и улучшение производительности матрицы контроля четности. Блочный код LDPC также является кодом LDPC, расширенным посредством обобщения структуры регулярного кода LDPC. Матрица контроля четности блочного кода LDPC, проиллюстрированного на фиг.6, составлена из 4-х частичных блоков, линия диагонали представляет позиции, где расположены элементы, имеющие значение 1, а части, отличные от расположенных по линии диагонали частей, представляют позиции, где расположены элементы, имеющие значение 0. В дополнение, 'P' является изображением такой же матрицы перестановок, как матрица перестановок, описанная в связи с фиг.5.

Для того чтобы проанализировать циклическую структуру блочного кода LDPC, проиллюстрированного на фиг.6, элемент, имеющий значение 1, расположенное в i-й строке частичной матрицы Pa, определен как опорный элемент, и элемент, имеющий значение 1, расположенное в i-й строке, будет упоминаться как «точка 0». В материалах настоящей заявки «частичная матрица» будет относиться к матрице, соответствующей частичному блоку. Точка 0 расположена в (I + a)-м столбце частичной матрицы Pa.

Элемент, имеющий значение 1 в частичной матрице Pb, расположенный в той же строке, что и точка 0, будет упоминаться как «точка 1». По той же причине, что и точка 0, точка 1 расположена в (i + b)-м столбце частичной матрицы Pb.

Далее, элемент, имеющий значением 1 в частичной матрице Pс, расположенный в том же самом столбце, что и точка 1, будет упоминаться как «точка 2». Так как частичная матрица Pc является матрицей, полученной сдвигом соответствующих столбцов единичной матрицы I вправо по остатку от деления Ns на c, точка 2 расположена в (i + b - c)-й строке частичной матрицы Pc.

В дополнение, элемент, имеющий значение 1 в частичной матрице Pd, расположенный в той же самой строке, что и точка 2, будет упоминаться как «точка 3». Точка 3 расположена в (i + b - c + d)-м столбце частичной матрицы Pd.

В заключение, элемент, имеющий значение 1 в частичной матрице Pa, расположенный в том же самом столбце, что и точка 3, будет упоминаться как «точка 4». Точка 4 расположена в (i + b - c + d - a)-й строке частичной матрицы Pa.

В циклической структуре кода LDPC, проиллюстрированной на фиг.6, если существует цикл с длиной 4, точка 0 и точка 4 расположены в одной и той же позиции. То есть соотношение между точкой 0 и точкой 4 определено равенством (2)

i ≅ i + b - c + d - a(mod Ns)или

i + a ≅ i + b - c + d(mod Ns)(2)

Равенство (2) может быть переписано в виде равенства (3)

a + c ≅ b + d(mod Ns)(3)

Как результат, когда удовлетворено соотношение по равенству (3), сформирован цикл с длиной 4. Вообще, когда точка 0 и точка 4 изначально идентичны друг другу, задано соотношение i ≅ i + p(b - c + d - e)(mod Ns), и удовлетворено следующее соотношение, показанное в равенстве (4).

p(a - b + c - d)≅0(mod Ns).(4)

Другими словами, если положительное целое число, обладающее минимальным значением среди положительных целых чисел, удовлетворяющих равенству (4) для заданных a, b, c и d, определено как 'p', цикл с длиной 4p становится циклом, имеющим минимальную длину в циклической структуре блочного кода LDPC, проиллюстрированной на фиг.6.

В итоге, как описано выше, для (a - b + c - d) ≠ 0, если удовлетворено gcd(Ns, a - b + c - d) = 1, то p = Ns. Здесь, gcd(Ns, a - b + c - d) является функцией для расчета «наибольшего общего делителя» целых чисел Ns и a - b + c - d. Поэтому цикл с длиной 4Ns становится циклом с минимальной длиной.

Метод Ричардсона-Урбанке будет использован в качестве технологии кодирования для блочного кода LDPC. Так как метод Ричардсона-Урбанке используется в качестве технологии кодирования, сложность кодирования может быть минимизирована, в то время как вид матрицы контроля четности становится подобным виду нижней треугольной матрицы.

Со ссылкой на фиг.7, далее будет приведено описание матрицы контроля четности, имеющей вид, подобный виду полной нижней треугольной матрицы.

Фиг.7 иллюстрирует матрицу контроля четности, имеющую вид, подобный виду полной нижней треугольной матрицы. Матрица контроля четности, проиллюстрированная на фиг.7, отлична от матрицы контроля четности, имеющей вид полной нижней треугольной матрицы в представлении части контроля по четности. На фиг.7 верхним индексом (или показателем) apq матрицы P перестановок информационной части является 0 ≤ apq ≤ Ns - 1 или apq = ∞, как описано выше. Матрица P перестановок с верхним индексом apq = 0, то есть матрица P0 перестановок информационной части, представляет единичную матрицу , а матрица P перестановок с верхним индексом apq =∞, то есть матрица P∞ перестановок, представляет нулевую матрицу. На фиг.7 'p' представляет количество строк частичных блоков, помещенных в информационную часть, а 'q' представляет количество столбцов частичных блоков, помещенных в часть контроля по четности. К тому же верхние индексы ap, x и y матриц P перестановок, помещенных в часть контроля по четности, представляют показатели матрицы P перестановок. Однако для удобства разъяснения, разные верхние индексы ap, x и y используются для проведения различия части контроля по четности от информационной части. То есть на фиг.7, и также являются матрицами перестановок, а верхние индексы с a1 по ap пронумерованы последовательно по отношению к частичным матрицам в диагональной части у части контроля по четности. В дополнение, Px и Py также являются матрицами перестановок, и, для удобства разъяснения, они проиндексированы разным способом, чтобы отличать часть контроля по четности от информационной части. Если предполагается, что длиной блока блочного кода LDPC, обладающего матрицей контроля четности, проиллюстрированной на фиг.7, является N, сложность кодирования блочного кода LDPC линейно возрастает относительно длины N блока (0(N)).

Наибольшая проблема кода LDPC, обладающего матрицей контроля четности по фиг.7, состоит в том, что если частичный блок определен как Ns, формируется Ns узлов контроля, чьими степенями всегда являются 1, в факторном графе блочного кода LDPC. Узлы контроля со степенью 1 не могут влиять на улучшение производительности на основании итерационного декодирования. Поэтому стандартный нерегулярный код LDPC, основанный на методике Ричардсона-Урбанке, не включает в себя узел контроля со степенью 1. Поэтому матрица контроля четности по фиг.7 будет предполагаться в качестве базисной матрицы контроля четности для того, чтобы конструировать матрицу контроля четности, из условия, чтобы она давала возможность эффективного кодирования, наряду с исключением узла контроля со степенью 1. В матрице контроля четности по фиг.7, составленной из частичных матриц, выбор частичной матрицы является очень важным фактором для улучшения производительности блочного кода LDPC, так что нахождение подходящего критерия выбора для частичной матрицы также становится очень важным фактором.

Далее будет приведено описание способа для конструирования матрицы контроля четности блочного кода LDPC на основании вышеприведенного блочного кода LDPC.

Для того чтобы облегчить способ конструирования матрицы контроля четности блочного кода LDPC и способа для кодирования блочного кода LDPC, матрица контроля четности, проиллюстрированная на фиг.7, предполагается сформированной 6 частичными матрицами, как проиллюстрировано на фиг.8.

Фиг.8 - схема, иллюстрирующая матрицу контроля четности по фиг.7, которая разделена на 6 частичных блоков. Со ссылкой на фиг.8, матрица контроля четности блочного кода LDPC, проиллюстрированная на фиг.7, разделена на информационную часть 's', первую часть p1 контроля по четности и вторую часть p2 контроля по четности. Информационная часть 's' представляет часть матрицы контроля четности, отображаемую в реальное информационное слово во время процесса кодирования блочного кода LDPC, аналогично информационной части, описанной в связи с фиг.7, но для удобства разъяснения, информационная часть 's' изображена другими ссылочными символами. Первая часть p1 контроля по четности и вторая часть p2 контроля по четности представляют части матрицы контроля четности, отображаемые в реальный контроль по четности во время процесса кодирования блочного кода LDPC, аналогично части контроля по четности, описанной в связи с фиг.7, и часть контроля по четности разделена на две части.

Частичные матрицы A и C соответствуют частичным блокам A(802) и C(804) информационной части 's', частичные матрицы B и D соответствуют частичным блокам B(806) и D(808) первой части p1 контроля по четности, а частичные матрицы T и E соответствуют частичным блокам T(810) и E(812) второй части p2 контроля по четности. Хотя матрица контроля четности разделена на 7 частичных блоков на фиг.8, должно быть отмечено, что '0' не является отдельным частичным блоком, и, так как частичная матрица Т, соответствующая частичному блоку T(810), имеет вид полной нижней треугольной формы, область, где нулевые матрицы скомпонованы на основе диагонали, представлена посредством '0'. Процесс по упрощению способа кодирования с использованием частичных матриц информационной части 's', первой части p1 контроля по четности и второй части p2 контроля по четности будет описан позже, со ссылкой на фиг.10.

Далее, частичные матрицы по фиг.8 будут описаны ниже в материалах настоящей заявки, со ссылкой на фиг.9.

Фиг.9 - схема, иллюстрирующая транспонированную матрицу частичной матрицы B, показанной на фиг.8, частичную матрицу E, частичную матрицу T и обратную матрицу частичной матрицы Т в матрице контроля четности по фиг.7.

Со ссылкой на фиг.9 частичная матрица BT представляет транспонированную матрицу частичной матрицы В, а частичная матрица T-1 представляет обратную матрицу частичной матрицы T.

представляет . Матрицы перестановок, проиллюстрированные на фиг.9, например, , могут быть единичной матрицей. Как описано выше, если верхним индексом матрицы перестановок, то есть a1, является 0, будет единичной матрицей. К тому же, если верхний индекс матрицы перестановок, то есть a1, увеличивается на предопределенное значение, матрица перестановок циклически сдвигается на предопределенное значение, так что матрица перестановок будет единичной матрицей.

Со ссылкой на фиг.10 далее будет приведено описание последовательности операций конструирования матрицы контроля четности блочного кода LDPC.

Фиг.10 - блок-схема последовательности операций способа, иллюстрирующая процедуру формирования матрицы контроля четности обычного блочного кода LDPC. До того как дано описание по фиг.10, должно быть отмечено, что, для того чтобы сформировать блочный код LDPC, должны быть определены размер кодовой комбинации и скорость кодирования блочного кода LDPC, который должен формироваться, а размер матрицы контроля четности должен устанавливаться согласно определенному размеру кодовой комбинации и скорости кодирования. Если размер кодовой комбинации блочного кода LDPC представлен посредством N, скорость кодирования представлена посредством R, размером матрицы контроля четности становится N(1 - R) × N. Фактически, процедура для формирования матрицы контроля четности блочного кода LDPC, проиллюстрированная на фиг.10, выполняется только однажды, так как матрица контроля четности первоначально формируется, чтобы быть подходящей для состояния системы связи, и после этого сформированная матрица контроля четности используется.

Со ссылкой на фиг.10 на этапе 1011 контроллер разделяет матрицу контроля четности с размером N(1 - R) × N всего на p × q блоков, в том числе, p блоков по горизонтальной оси и q блоков по вертикальной оси, а затем переходит на этап 1013. Так как каждый из блоков имеет размер Ns ×Ns, матрица контроля четности составлена из Ns ×p столбцов и Ns ×q строк. На этапе 1013 контроллер сортирует p×q блоков, выделенных из матрицы контроля четности, в информационную часть 's', первую часть p1 контроля по четности и вторую часть p2 контроля по четности, а затем переходит на этап 1015 и 1021.

На этапе 1015 контроллер разделяет информационную часть 's' на ненулевые блоки или ненулевые матрицы и нулевые блоки или нулевые матрицы согласно степени распределения для гарантирования хорошей производительности блочного кода LDPC, а затем переходит на этап 1017. Так как степень распределения для гарантирования хорошей производительности блочного кода LDPC была описана выше, ее подробное описание здесь будет опущено. На этапе 1017 контроллер определяет матрицы перестановок, из условия, что минимальная длина блочного цикла должна быть максимизирована, как описано выше, в ненулевых матричных частях в блоках, имеющих низкую степень из числа блоков, определенных согласно распределению степеней, для гарантирования хорошей производительности блочного кода LDPC, а затем переходит на этап 1019. Матрицы перестановок должны определяться, принимая во внимание блочные циклы не только информационной части 's', но также и первой часть p1 контроля по четности и второй части p2 контроля по четности.

На этапе 1019 контроллер случайным образом определяет матрицы перестановок в ненулевых матричных частях в блоках, имеющих высокую степень, среди блоков, определенных согласно распределению степеней, для гарантирования хорошей производительности блочного кода LDPC, а затем заканчивает процедуру. Даже когда определены матрицы перестановок, которые должны применяться к ненулевым матричным частям в блоках, имеющих высокую степень, матрицы перестановок должны определяться так, что минимальная длина цикла блочного цикла максимизирована, а матрицы перестановок определены с учетом блочных циклов не только информационной части 's', но также первой части p1 контроля по четности и второй части p2 контроля по четности. Пример матриц перестановок, скомпонованных в информационной части 's' матрицы контроля четности, проиллюстрирован на фиг.7.

На этапе 1021 контроллер разделяет первую часть p1 контроля по четности и вторую часть p2 контроля по четности на 4 частичные матрицы B, T, D и E, а затем переходит на этап 1023. На этапе 1023 контроллер вводит ненулевые матрицы Py и перестановок в два частичных блока из числа частичных блоков, составляющих частичную матрицу В, а затем переходит на этап 1025. Структура для ввода ненулевых матриц Py и перестановок в два частичных блока из числа частичных блоков, составляющих частичную матрицу В, была описана со ссылкой на фиг.9.

На этапе 1025 контроллер вводит единичные матрицы I в диагональные частичные блоки частичной матрицы Т, вводит конкретные матрицы , ,..., перестановок в (i, i + 1)-е частичные блоки под диагональными элементами частичной матрицы Т, а затем переходит на этап 1027. Структура для ввода единичных матриц I в диагональные частичные блоки частичной матрицы Т и ввода конкретных матриц , ,..., перестановок в (i, i + 1)-е частичные блоки под диагональными элементами частичной матрицы Т была описана со ссылкой на фиг.9.

На этапе 1027 контроллер вводит частичную матрицу Px в частичную матрицу D, а затем переходит на этап 1029. На этапе 1029 контроллер вводит матрицу перестановок только в последний частичный блок в частичной матрице E, а затем заканчивает процедуру. Структура для ввода 2-х матриц перестановок только в последний частичный блок из числа частичных бло