Способ изготовления плат гибридных интегральных схем крючатова в.и.

Иллюстрации

Показать всеИзобретение относится к электротехнике, в частности к технологии изготовления плат гибридных интегральных схем, и может быть использовано в радиоэлектронной промышленности, приборостроении и вычислительной технике. Технический результат - повышение качества и снижение трудоемкости изготовления плат гибридных интегральных схем. Достигается тем, что технологические перемычки образуют из проводящего слоя многослойной структуры с получением на заготовке рисунка проводников, полученного фотолитографической обработкой, и последующим селективным травлением проводящего и резистивного слоев между проводниками и пленочными технологическими перемычками, а после электролитического осаждения дополнительного проводящего и защитного слоя проводника выполняют селективное химическое стравливание пленочных технологических перемычек. На подложку наносят трехслойное покрытие, состоящее из слоя адгезива, на который осаждают проводящий и защитный слой, на последний наносят фоторезист, соответствующий рисунку проводников с технологическими перемычками и окантовки, по меньшей мере, с одной стороны периметра заготовки, между которыми удаляют резист и выполняют селективное химическое стравливание проводящего и резистивного слоев с получением на заготовке рельефа рисунка проводников и окантовки, соединенных пленочными технологическими перемычками. Трехслойное покрытие подложки получают последовательным напылением в вакууме слоев ванадия, меди и хрома. Электролитическое наращивание на проводниках слоя меди до номинальной толщины осуществляют после удаления резиста с поверхности проводников, окантовки и пленочных технологических перемычек, последние со всех сторон повторно покрывают фоторезистом, а на проводниках и окантовке выполняют селективное химическое стравливание защитного слоя хрома, после чего к окантовке, электрически соединенной со слоем меди проводников посредством пленочных технологических перемычек, примыкают электрод постоянного тока, с помощью которого на слой меди проводников дополнительно осаждают ионы меди электролита до образования на проводниках слоя меди номинальной толщины. На проводники с номинальной толщиной слоя меди со всех сторон осаждают электролитический буферный слой из никеля, на последний осаждают защитный слой из золота, после чего выполняют селективное химическое стравливание пленочных технологических перемычек и окантовки, образуя плату гибридной интегральной схемы. 2 з.п. ф-лы, 6 ил.

Реферат

Изобретение относится к области электротехники, в частности к технологии изготовления плат гибридных интегральных схем СВЧ с тонкой структурой, и может быть использовано в радиоэлектронной промышленности, приборостроении и вычислительной технике.

Известен способ нанесения на печатную схему токопроводящих дорожек, полученных отпечатыванием их на подложке с помощью красителя, содержащего полимерный состав, насыщенный электропроводящими частицами, которые покрывают гальваническим раствором с отложением на токопроводящих дорожках слоя меди. (Патент RU №2218680 С2. Способ и устройство для нанесения на печатную схему токопроводящих дорожек. - МПК7: Н05К 3/18. - 2003.12.10). Недостатком известного технического решения является сложность технологии гальванического нанесения на печатную схему токопроводящих дорожек, особенно электрически не соединенных между собой, что исключает возможность одновременного изготовления большого количества плат.

Известен способ изготовления печатных плат путем последовательного нанесения на металлическую пластину двухслойного диэлектрического оксидоалюминиевого и оксидомедного гальванического покрытия, состоящего из оксида алюминия (оксида меди) и оксида хрома, получение методом фотолитографии рисунка электропроводящей схемы и нанесение на него двухслойного электропроводящего металлического покрытия из меди и никеля в вакууме из газовой фазы путем термораспада металлоорганических соединений. (Патент RU №2282319 С2. Способ изготовления печатных плат. - МПК7: Н05К 3/18. - 2006.08.20). Недостатком известного технического решения является наличие по периметру проводников на боковых сторонах открытого пояска меди, образованного после стравливания слоев никеля и меди с пробельных мест, подвергающего проводники окислению и разрушению.

Известен способ изготовления плат гибридных интегральных схем СВЧ, который заключается в очистке подложки, нанесении в вакууме многослойной структуры, включающей резистивный (адгезионный) и проводящий слои, фотолитографической обработке заготовки, селективном травлении проводящего и резистивного слоев с получением на заготовке рисунка проводников, снятии фоторезиста, приварке технологических перемычек, электролитическом осаждении проводящего и защитного слоев до получения проводников, удалении технологических перемычек, резке плат и контроле размеров. (Кн. Бушминский И.П., Морозов Г.В. Технология гибридных интегральных схем СВЧ: Учеб. пособие. - М.: Высш. школа, 1980. - 285 с., ил. - стр.276). Данный способ принят за прототип.

Недостатком известного способа, принятого за прототип, является невысокое качество и надежность плат гибридных интегральных схем в работе из-за приварки к проводникам технологических перемычек и сложности последующего удаления их механическим способом.

Основной задачей, на решение которой направлено заявляемое изобретение, является повышение качества изготовления плат гибридных интегральных схем.

Техническим результатом, достигаемым при осуществлении заявляемого способа, является повышение качества и снижение трудоемкости изготовления плат гибридных интегральных схем.

Указанный технический результат достигается тем, что в известном способе изготовления плат гибридных интегральных схем, заключающемся в очистке подложки, нанесении в вакууме многослойной структуры, включающей резистивный (адгезионный) и проводящий слои, фотолитографической обработке заготовки, селективном травлении проводящего и резистивного слоев с получением на заготовке рисунка проводников, снятии фоторезиста, образовании между проводниками технологических перемычек, электролитическом осаждении проводящего и защитного слоев до получения проводников и удалении технологических перемычек, согласно предложенному техническому решению

на многослойную структуру дополнительно наносят защитный слой заготовки, на последний наносят резистивную маску из фоторезиста, соответствующую рисунку проводников с технологическим перемычками и окантовкой, по крайней мере, с одной стороны периметра заготовки, между которыми удаляют резист и выполняют селективное химическое стравливание многослойной структуры до получения на подложке рельефа из проводников и окантовки, соединенных между собой пленочными технологическими перемычками, затем удаляют резист с поверхностей проводников, окантовки и технологических перемычек, последние повторно покрывают фоторезистом, причем со всех сторон, затем на поверхностях проводников и окантовки выполняют селективное химическое стравливание защитного слоя заготовки, после чего к окантовке, электрически соединенной с проводящим слоем проводников посредством технологических перемычек, примыкают электрод постоянного тока, с помощью которого электролитическим осаждением наращивают проводящий слой проводников до заданной толщины, на который затем наносят защитный слой проводников, после чего выполняют селективное химическое стравливание технологических перемычек и окантовки;

многослойное покрытие подложки получают последовательным напылением в вакууме слоев ванадия, меди и хрома;

защитный слой проводников выполняют последовательным электролитическим осаждением буферного слоя из никеля, на который осаждают защитный слой из золота, после чего выполняют селективное химическое стравливание технологических перемычек и окантовки, образуя плату гибридной интегральной схемы.

Приведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественными всем признакам заявленного способа изготовления плат гибридных интегральных схем, отсутствуют. Следовательно, заявленное техническое решение соответствует условию патентоспособности «новизна».

Результаты поиска известных решений в данной области техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявляемого технического решения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками из заявляемого технического решения преобразований на достижение указанного технического результата. Следовательно, заявляемое техническое решение соответствует условию патентоспособности «изобретательский уровень».

На представленных фигурах схематично показаны основные технологические переходы процесса изготовления плат гибридных интегральных схем:

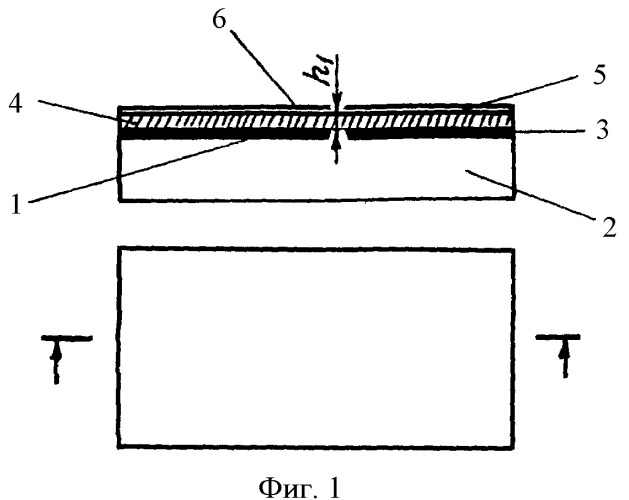

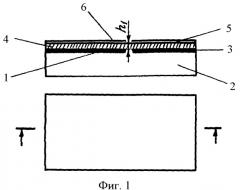

на фиг.1 - нанесение на подложку трехслойного покрытия;

на фиг.2 - фотолитография рисунка проводников и окантовки с технологическими перемычками;

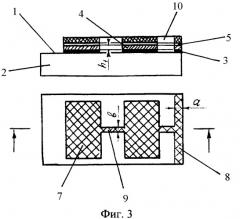

на фиг.3 - формирование рельефа из проводников, окантовки и пленочных технологических перемычек;

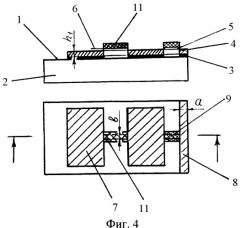

на фиг.4 - нанесение на пленочные технологические перемычки защитного фоторезиста и удаление защитного слоя с поверхности проводников;

на фиг.5 - формирование проводников платы гибридной интегральной схемы;

на фиг.6 - удаление пленочных технологических перемычек и окантовки.

Сущность предложенного способа изготовления плат гибридных интегральных схем заключается в следующем.

На очищенную поверхность 1 подложки 2 в вакууме последовательно наносят трехслойное покрытие из адгезионного подслоя 3, например из ванадия (V), затем проводящего слоя 4 из меди (Cu1) толщиной h1 и защитного слоя 5 из хрома (Cr). (Фиг.1). Полученную заготовку подвергают фотолитографической обработке с выделением на поверхности 6 трехслойного покрытия (V-Cu1-Cr) рисунка проводников 7 и окантовки 8, по меньшей мере, с одной стороны периметра заготовки, соединенных между собой технологическими перемычками 9. (Фиг.2). Между проводниками 7, окантовкой 8 и технологическими перемычками 9 удаляют резист 10 и выполняют селективное химическое стравливание защитного слоя 5 и проводящего слоя 4 и адгезионного слоя 3 (Cr-Cu1-V) с получением на заготовке рельефа рисунка проводников 7 и окантовки 8 шириной а с пленочными технологическими перемычками 9 шириной b. (Фиг.3). После этого с пленочных технологических перемычек 9 удаляют резист 10, затем как поверхность 6, так и боковые стороны пленочных технологических перемычек 9 покрывают фоторезистом 11. (Фиг.4). На проводниках 7 и окантовке 8 выполняют селективное химическое стравливание защитного слоя 5 из хрома (Cr). Затем к слою 4 из меди (Cu1) окантовки 8, электрически соединенной посредством технологических перемычек 9 со слоем 4 из меди (Cu1) проводников 7, примыкают электрод 12 постоянного тока, с помощью которого на слой 4 меди (Cu1) проводников 7 дополнительно осаждают второй слой 13 толщиной h2 из ионов меди (Cu2) электролита до образования на проводниках 7 слоя меди (Cu1+Cu2) номинальной толщины h=(h1+h2), на которые со всех сторон осаждают электролитический буферный слой 14 из никеля (Ni), на последний осаждают защитный слой 15 из золота (Au). (Фиг.5). После этого выполняют селективное химическое стравливание слоев 10-5-4-3 пленочных технологических перемычек 9 и слоев 4-3 окантовки 8, образуя плату гибридной интегральной схемы. (Фиг.6).

Пример осуществления способа.

На очищенную поверхность 1 подложки 2 из поликора платы гибридной интегральной схемы СВЧ размером 60,0×48,0 мм и толщиной 0,5-1,0 мм напылением в вакууме последовательно наносили трехслойное покрытие, сначала осаждали подслой 3 из ванадия (V), затем тонкий слой 4 из меди (Cu1) толщиной h1=1,5±0,5 мкм и защитный слой 5 из хрома (Cr). На поверхность 6 заготовки фотолитографией наносили рисунок проводников 7 и окантовки 8 с одной стороны периметра платы, соединенных между собой технологическими перемычками 9, из фоторезиста 10. Между проводниками 7, окантовкой 8 и технологическими перемычками 9 удаляли резист 10 и выполняли селективное химическое стравливание защитного слоя 5 из хрома (Cr), проводящего слоя 4 из меди (Cu1) и адгезионного подслоя 3 из ванадия (V) с получением на подложке 2 рельефа рисунка проводников 7 и окантовки 8 шириной а=3,0 мм с пленочными технологическими перемычками 9 шириной b=50÷100 мкм. После этого с пленочных технологических перемычек 9 удаляли резист 10, затем как поверхность 6, так и боковые стороны пленочных технологических перемычек 9 повторно покрывали фоторезистом 11, а на проводниках 7 и окантовке 8 выполняли селективное химическое стравливание защитного слоя 5 из хрома (Cr). Затем к слою 4 из меди (Cu1) окантовки 8, электрически соединенной посредством пленочных технологических перемычек 9 со слоем 4 из меди (Cu1) на проводниках 7, примыкали электрод 12 постоянного тока, с помощью которого на слой 4 меди (Cu1) проводников 7 с h1=1,5±0,5 мкм при плотности тока 0,5÷1,0 А/м2 и температуре 20±5°С выполняли электролитическое наращивание Cu2 второго слоя 13 толщиной h2=10±3 мкм до получения на проводниках 7 слоя меди (Cu1+Cu2) с номинальной толщиной h=(h1+h2), на которые со всех сторон осаждали электролитический буферный слой 14 из никеля (Ni) толщиной 1,5±0,5 мкм, на последний таким же образом осаждали защитный слой 15 из золота (Au) толщиной 2,5±0,5 мкм. После этого выполняли селективное химическое стравливание слоев 10-5-4-3 пленочных технологических перемычек 9 и слоев 4-3 окантовки 8, и в итоге получали плату гибридной интегральной схемы СВЧ.

Предложенный способ позволит повысить качество и снизить трудоемкость изготовления плат гибридных интегральных схем.

1. Способ изготовления плат гибридных интегральных схем, заключающийся в очистке подложки, нанесении в вакууме многослойной структуры, включающей резистивный (адгезионный) и проводящий слои, фотолитографической обработке заготовки, селективном травлении проводящего и резистивного слоев с получением на заготовке рисунка проводников, снятии фоторезиста, образовании между проводниками технологических перемычек, электролитическом осаждении проводящего и защитного слоев до получения проводников и удалении технологических перемычек, отличающийся тем, что на многослойную структуру дополнительно наносят защитный слой заготовки, на последний наносят резистивную маску из фоторезиста, соответствующую рисунку проводников с технологическим перемычками и окантовкой, по крайней мере, с одной стороны периметра заготовки, между которыми удаляют резист и выполняют селективное химическое стравливание многослойной структуры до получения на подложке рельефа из проводников и окантовки, соединенных между собой пленочными технологическими перемычками, затем удаляют резист с поверхностей проводников, окантовки и технологических перемычек, последние повторно покрывают фоторезистом, причем со всех сторон, затем на поверхностях проводников и окантовки выполняют селективное химическое стравливание защитного слоя заготовки, после чего к окантовке, электрически соединенной с проводящим слоем проводников посредством технологических перемычек, примыкают электрод постоянного тока, с помощью которого электролитическим осаждением наращивают проводящий слой проводников до заданной толщины, на который затем наносят защитный слой проводников, после чего выполняют селективное химическое стравливание технологических перемычек и окантовки.

2. Способ по п.1, отличающийся тем, что многослойное покрытие подложки получают последовательным напылением в вакууме слоев ванадия, меди и хрома.

3. Способ по п.1, отличающийся тем, что защитный слой проводников выполняют последовательным электролитическим осаждением буферного слоя из никеля, на который осаждают защитный слой из золота, после чего выполняют селективное химическое стравливание технологических перемычек и окантовки, образуя плату гибридной интегральной схемы.