Радиолокационный приемник с каналами высокого разрешения

Иллюстрации

Показать всеИзобретение относится к приемному тракту радиолокационных или аналогичных систем и предназначено для обеспечения высокопроизводительной первичной цифровой обработки сигналов в реальном масштабе времени во всех режимах работы бортовой радиолокационной станции. Достигаемым техническим результатом изобретения является обеспечение двухчастотного режима приема радиолокационных сигналов, расширение полосы пропускания приемного тракта, обеспечение высокого разрешения по дальности, достигается он за счет того, что радиолокационный приемник с каналами высокого разрешения содержит n приемных каналов с входным сигналом второй промежуточной частоты, включающих каждый усилитель промежуточной частоты, аналого-цифровой преобразователь, цифровой формирователь квадратур, устройство цифрового гетеродинирования, постоянное запоминающее устройство, цифровой сумматор, адаптер и передатчик данных, кроме этого, введены формирователь опорных частот и n приемных каналов высокого разрешения с входным сигналом первой промежуточной частоты. 2 з.п. ф-лы, 3 ил.

Реферат

Изобретение относится к приемному тракту радиолокационных или аналогичных систем и предназначено для обеспечения высокопроизводительной первичной обработки сигналов во всех режимах работы бортовой радиолокационной станции (БРЛС).

В данной работе рассматривается только низкочастотная часть радиолокационного приемного тракта, в которой производится обработка принятого сигнала после переноса спектра сигнала на промежуточные частоты. Почти все радиолокационные приемники строятся по супергетеродинному принципу. Усиленный отраженный сигнал преобразуется в сигналы промежуточных частот путем смешивания с сигналом гетеродина. Для получения конечной промежуточной частоты, обычно лежащей в пределах от 0,1 МГц до 100 МГц, может понадобиться не одна ступень преобразования. В данном случае применено двойное преобразование частоты принятого сигнала в промежуточную частоту.

Одним из основных факторов, определяющих структуру радиолокационного приемника, является выбранный метод обработки сигнала на промежуточной частоте: разделение на квадратурные составляющие и перенос спектра сигнала на видеочастоту с обеспечением возможности перестройки частоты гетеродина.

В настоящее время для этой цели широко используются аналоговые фазовые детекторы [Дудник П.И., Чересов Ю.И. Авиационные радиолокационные устройства. - М.: ВВИА им. Проф. Н.Е.Жуковского, 1986, с.247, рис.8.15] и разложение принимаемого сигнала на квадратурные составляющие [патент US №5627856]. При этом сигнал гетеродина может быть фиксированным (fг=fп) или перестраиваемым по частоте. В первом случае для управления значением центральной частоты полосы анализа применяется метод цифрового гетеродинирования после оцифровки сигнала [патент РФ №2225623]. Во втором случае для получения сигнала гетеродина применяются специальные, довольно сложные устройства - цифровые управляемые гетеродины (ЦУГ) [патент US №4292635 А, патент РФ №2123709].

Наиболее близким по технической сущности является радиолокационный приемник с цифровым гетеродинированием [патент РФ №2225623, МПК G01S 7/285, 7/26], содержащий кварцевый генератор, формирователь опорного сигнала, два цифровых сумматора, магистраль параллельной информации, n каналов приема, состоящих каждый из аналогового сумматора и когерентного приемника с цифровым выходом. В этом радиолокационном приемнике применен аналоговый метод преобразования сигнала, поступающего в канал приема на второй промежуточной частоте. Использование аналогового метода переноса спектра сигнала на видеочастоту имеет ряд недостатков, которые приводят к искажению спектра сигнала. В предлагаемом техническом решении для основных приемных каналов применен цифровой метод разложения сигнала на квадратурные составляющие и перенос спектра на видеочастоту. Кроме этого, ни в одном из вышеперечисленных аналогов не применяется обработка сигнала на первой промежуточной частоте, оптимальное значение которой лежит в диапазоне от 1 ГГц до 5 ГГц. Предлагается дополнительно ввести приемные каналы высокого разрешения с входным сигналом на первой промежуточной частоте, что позволяет обеспечить разрешение по дальности БРЛС около одного метра.

Технической задачей, на решение которой направлено настоящее изобретение, является введение режима обработки радиолокационных сигналов на первой промежуточной частоте с целью расширения полосы пропускания приемного тракта для обеспечения высокого разрешения по дальности.

Технический результат достигается тем, что радиолокационный приемник с каналами высокого разрешения содержит n (n - целое число) приемных каналов, включающих каждый аналого-цифровой преобразователь, устройство цифрового гетеродинирования, постоянное запоминающее устройство и цифровой сумматор, в каждый приемный канал введены: усилитель промежуточной частоты, цифровой формирователь квадратур, адаптер и передатчик данных. Вход усилителя промежуточной частоты является входом сигнала второй промежуточной частоты, а выход последовательно соединен с аналого-цифровым преобразователем, цифровым формирователем квадратур, устройством цифрового гетеродинирования, цифровым сумматором и передатчиком данных. Выход передатчика данных является выходом приемного канала. Выход постоянного запоминающего устройства соединен со вторым входом устройства цифрового гетеродинирования. Первый выход адаптера соединен с управляющим входом устройства цифрового гетеродинирования, а второй выход адаптера соединен с управляющим входом цифрового сумматора. Выход синхронизации аналого-цифрового преобразователя соединен с входами синхронизации цифрового формирователя квадратур, устройства цифрового гетеродинирования, цифрового сумматора и передатчика данных. Кроме этого, в радиолокационный приемник с каналами высокого разрешения введены формирователь опорных частот и n приемных каналов высокого разрешения. Каждый приемный канал высокого разрешения включает: полосовой фильтр первой промежуточной частоты, фазовый детектор, первый и второй фильтры нижних частот, первый и второй операционные усилители, первый и второй аналого-цифровые преобразователи высокого разрешения, первый и второй цифроаналоговые преобразователи и устройство цифровой обработки. Вход полосового фильтра первой промежуточной частоты является входом сигнала первой промежуточной частоты. Выход полосового фильтра первой промежуточной частоты соединен с входом фазового детектора, выход реальной квадратуры сигнала фазового детектора последовательно соединен с первым фильтром нижних частот, первым операционным усилителем, первым аналого-цифровым преобразователем высокого разрешения и входом реальной квадратуры сигнала устройства цифровой обработки. Выход мнимой квадратуры сигнала фазового детектора последовательно соединен со вторым фильтром нижних частот, вторым операционным усилителем, вторым аналого-цифровым преобразователем высокого разрешения и входом мнимой квадратуры сигнала устройства цифровой обработки. Выход устройства цифровой обработки является выходом приемного канала высокого разрешения. Вход формирователя опорных частот является входом опорного сигнала. Первый выход формирователя опорных частот соединен с управляющим входом аналого-цифрового преобразователя, второй выход формирователя опорных частот соединен с управляющими входами первого и второго аналого-цифровых преобразователей высокого разрешения, третий выход формирователя опорных частот соединен с управляющим входом фазового детектора. Синхронизирующие выходы первого и второго аналого-цифровых преобразователей высокого разрешения соединены соответственно с входами сигналов данных реальной квадратуры и сигналов данных мнимой квадратуры устройства цифровой обработки. Вход первого цифроаналогового преобразователя соединен с выходом реальной квадратуры кода устройства цифровой обработки, а выход - с управляющим входом первого операционного усилителя. Вход второго цифроаналогового преобразователя соединен с выходом мнимой квадратуры кода устройства цифровой обработки, а выход - с управляющим входом второго операционного усилителя. Управляющие входы усилителя промежуточной частоты, адаптера и устройства цифровой обработки соединены с интерфейсом центрального процессора. Тактовые входы усилителя промежуточной частоты, цифрового сумматора и устройства цифровой обработки являются входами тактового импульса. Входы начала отсчета по дальности цифрового сумматора и устройства цифровой обработки являются входами импульса начала отсчета.

В радиолокационном приемнике с каналами высокого разрешения формирователь опорных частот может содержать первый, второй, третий и четвертый умножители частоты, первый, второй, третий, четвертый и пятый полосовые фильтры, первый, второй, третий, четвертый, пятый, шестой и седьмой усилители, первый и второй режекторные фильтры, первый, второй формирователи частоты дискретизации и усилитель-ограничитель. При этом вход первого умножителя частоты является входом опорного сигнала Fоп. Выход первого умножителя частоты последовательно соединен с первым полосовым фильтром, первым усилителем, первым режекторным фильтром, вторым усилителем и первым формирователем частоты дискретизации, выход которого является первым выходом формирователя опорных частот. Вход третьего усилителя соединен с входом усилителя-ограничителя и выходом первого режекторного фильтра. Выход третьего усилителя последовательно соединен со вторым умножителем частоты, вторым полосовым фильтром, четвертым усилителем и вторым формирователем частоты дискретизации, выход которого является вторым выходом формирователя опорных частот. Выход усилителя-ограничителя последовательно соединен со вторым режекторным фильтром, третьим полосовым фильтром, пятым усилителем, третьим умножителем частоты, четвертым полосовым фильтром, шестым усилителем, четвертым умножителем частоты, пятым полосовым фильтром и седьмым усилителем, выход которого является третьим выходом формирователя опорных частот.

В радиолокационном приемнике с каналами высокого разрешения устройство цифровой обработки может содержать первую и вторую схемы балансировки, первый и второй преобразователи, первый и второй регистры, первый и второй буферы, первое и второе оперативные запоминающие устройства, синхронизатор и передатчик данных канала высокого разрешения. При этом первый вход первого регистра является входом реальной квадратуры сигнала устройства цифровой обработки и соединен со вторым входом первой схемы балансировки. Второй вход первого регистра является входом сигналов данных реальной квадратуры устройства цифровой обработки и соединен с первым входом первой схемы балансировки, вторым и третьим входами первого буфера, вторым входом первого оперативного запоминающего устройства, третьим входом второго буфера, вторым входом второго оперативного запоминающего устройства и первым входом синхронизатора. Выход первой схемы балансировки соединен с входом первого преобразователя, выход которого является выходом реальной квадратуры кода устройства цифровой обработки. Выход первого регистра соединен с первым входом первого буфера, выход которого соединен с первым входом первого оперативного запоминающего устройства. Выход первого оперативного запоминающего устройства соединен с первым входом передатчика данных канала высокого разрешения, выход которого является выходом приемного канала высокого разрешения. Первый вход второго регистра является входом мнимой квадратуры сигнала устройства цифровой обработки и соединен со вторым входом второй схемы балансировки. Второй вход второго регистра является входом сигналов данных мнимой квадратуры устройства цифровой обработки и соединен с первым входом второй схемы балансировки и вторым входом второго буфера. Выход второй схемы балансировки соединен с входом второго преобразователя, выход которого является выходом мнимой квадратуры кода устройства цифровой обработки. Выход второго регистра соединен с первым входом второго буфера, выход которого соединен с первым входом второго оперативного запоминающего устройства. Выход второго оперативного запоминающего устройства соединен со вторым входом передатчика данных канала высокого разрешения. Второй, третий и четвертый входы синхронизатора являются соответственно тактовым, синхронизации и информационным входами устройства цифровой обработки. Первый выход синхронизатора соединен с четвертыми входами первого и второго оперативных запоминающих устройств. Второй выход синхронизатора соединен с третьими входами первого и второго оперативных запоминающих устройств. Третий, четвертый, пятый и шестой выходы синхронизатора соединены соответственно с третьим, четвертым, пятым и шестым входами передатчика данных канала высокого разрешения.

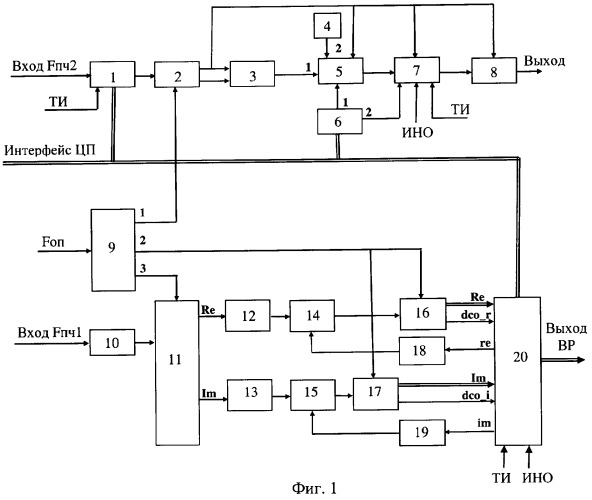

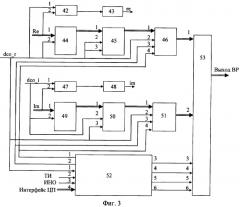

На фиг.1 представлена функциональная схема радиолокационного приемника с каналом высокого разрешения, на фиг.2 - функциональная схема формирователя опорных частот, на фиг.3 - функциональная схема устройства цифровой обработки.

На фиг.1 представлен одноканальный радиолокационный приемник с каналом высокого разрешения, n-ые приемные каналы имеют аналогичную структуру.

Радиолокационный приемник с каналом высокого разрешения содержит: усилитель промежуточной частоты 1, аналого-цифровой преобразователь 2, цифровой формирователь квадратур 3, постоянное запоминающее устройство 4, устройство цифрового гетеродинирования 5, адаптер 6, цифровой сумматор 7, передатчик данных 8, формирователь опорных частот 9, полосовой фильтр первой промежуточной частоты 10, фазовый детектор 11, первый 12 и второй 13 фильтры нижних частот, первый 14 и второй 15 операционные усилители, первый 16 и второй 17 аналого-цифровые преобразователи канала высокого разрешения, первый 18 и второй 19 цифроаналоговые преобразователи, устройство цифровой обработки 20.

Вход усилителя промежуточной частоты 1 является входом сигнала второй промежуточной частоты Fпч2, а выход последовательно соединен с аналого-цифровым преобразователем 2, цифровым формирователем квадратур 3, устройством цифрового гетеродинирования 5, цифровым сумматором 7 и передатчиком данных 8, выход которого является выходом приемного канала. Выход постоянного запоминающего устройства 4 соединен со вторым входом устройства цифрового гетеродинирования 5. Первый выход адаптера 6 соединен с управляющим входом устройства цифрового гетеродинирования 5, а второй выход соединен с управляющим входом цифрового сумматора 7. Синхронизирующий выход аналого-цифрового преобразователя 2 соединен с входами синхронизации цифрового формирователя квадратур 3, устройства цифрового гетеродинирования 5, цифрового сумматора 7 и передатчика данных 8. Вход полосового фильтра первой промежуточной частоты 10 является входом сигнала первой промежуточной частоты Fпч1, выход полосового фильтра первой промежуточной частоты 10 соединен с входом фазового детектора 11. Выход реальной квадратуры сигнала «Re» фазового детектора 11 последовательно соединен с первым фильтром нижних частот 12, первым операционным усилителем 14, первым аналого-цифровым преобразователем канала высокого разрешения 16 и входом реальной квадратуры сигнала «Re» устройства цифровой обработки 20. Выход мнимой квадратуры сигнала «Im» фазового детектора 11 последовательно соединен со вторым фильтром нижних частот 13, вторым операционным усилителем 15, вторым аналого-цифровым преобразователем канала высокого разрешения 17 и входом мнимой квадратуры сигнала «Im» устройства цифровой обработки 20. Выход устройства цифровой обработки 20 является выходом приемного канала высокого разрешения. Вход формирователя опорных частот 9 является входом опорного сигнала Fоп. Первый выход формирователя опорных частот 9 соединен с управляющим входом аналого-цифрового преобразователя 2, второй выход формирователя опорных частот 9 соединен с управляющими входами первого 16 и второго 17 аналого-цифровых преобразователей канала высокого разрешения, третий выход формирователя опорных частот 9 соединен с управляющим входом фазового детектора 11. Синхронизирующие выходы первого 16 и второго 17 аналого-цифровых преобразователей канала высокого разрешения соединены соответственно с входами сигналов данных реальной квадратуры «dco_r» и сигналов данных мнимой квадратуры «dco_i» устройства цифровой обработки 20. Вход первого цифроаналогового преобразователя 18 соединен с выходом реальной квадратуры кода «re» устройства цифровой обработки 20, а выход - с управляющим входом первого операционного усилители 14. Вход второго цифроаналогового преобразователя 19 соединен с выходом мнимой квадратуры кода «im» устройства цифровой обработки 20, а выход - с управляющим входом второго операционного усилителя 15. Управляющие входы усилителя промежуточной частоты 1, адаптера 6 и устройства цифровой обработки 20 соединены с интерфейсом центрального процессора ЦП. Тактовые входы усилителя промежуточной частоты 1, цифрового сумматора 7 и устройства цифровой обработки 20 являются входами тактового импульса ТИ. Входы внешней синхронизации цифрового сумматора 7 и устройства цифровой обработки 20 являются входами импульса начала отсчета ИНО.

Функциональная схема формирователя опорных частот (фиг.2) содержит: первый умножитель частоты 21 [умножитель частоты входного сигнала на два], первый полосовой фильтр 22, первый усилитель 23, первый режекторный фильтр 24, второй усилитель 25, первый формирователь частоты дискретизации 26, усилитель-ограничитель 27, третий усилитель 28, второй умножитель частоты 29, второй полосовой фильтр 30, четвертый усилитель 31, второй формирователь частоты дискретизации 32, второй режекторный фильтр 33, третий полосовой фильтр 34, пятый усилитель 35, третий умножитель частоты 36, четвертый полосовой фильтр 37, шестой усилитель 38, четвертый умножитель частоты 39, пятый полосовой фильтр 40, седьмой усилитель 41.

Вход первого умножителя частоты 21 является входом опорного сигнала Fоп формирователя опорных частот 9. Выход первого умножителя частоты 21 последовательно соединен с первым полосовым фильтром 22, первым усилителем 23, первым режекторным фильтром 24, вторым усилителем 25 и первым формирователем частоты дискретизации 26, выход которого является первым выходом формирователя опорных частот 9. Вход третьего усилителя 28 соединен с входом усилителя-ограничителя 27 и выходом первого режекторного фильтра 33. Выход третьего усилителя 28 последовательно соединен со вторым умножителем частоты 29, вторым полосовым фильтром 30, четвертым усилителем 31 и вторым формирователем частоты дискретизации 32, выход которого является вторым выходом формирователя опорных частот 9. Выход усилителя-ограничителя 27 последовательно соединен со вторым режекторным фильтром 24, третьим полосовым фильтром 34, пятым усилителем 35, третьим умножителем частоты 36, четвертым полосовым фильтром 37, шестым усилителем 38, четвертым умножителем частоты 39, пятым полосовым фильтром 40 и седьмым усилителем 41, выход которого является третьим выходом формирователя опорных частот 9.

Функциональная схема устройства цифровой обработки (фиг.3) содержит: первую схему балансировки 42, первый преобразователь 43 [преобразователь параллельного кода в последовательный], первый регистр 44 [буферный регистр], первый буфер 45 [буферное оперативное запоминающее устройство типа FIFO - «первый вошел, первый вышел»], первое оперативное запоминающее устройство 46 [основное оперативное запоминающее устройство типа «FIFO»], вторую схему балансировки 47, второй преобразователь 48 [преобразователь параллельного кода в последовательный], второй регистр 49 [буферный регистр], второй буфер 50 [буферное оперативное запоминающее устройство типа FIFO], второе оперативное запоминающее устройство 51 [основное оперативное запоминающее устройство типа FIFO], синхронизатор 52, передатчик данных канала высокого разрешения 53 [передатчик данных в виде последовательных кодов с уровнями LVDS - Low-Voltage Differential Signaling].

Первый вход первого регистра 44 является входом реальной квадратуры сигнала «Re» устройства цифровой обработки 20 и соединен со вторым входом первой схемы балансировки 42. Второй вход первого регистра 44 является входом сигналов данных реальной квадратуры «dco_r» устройства цифровой обработки 20 и соединен с первым входом первой схемы балансировки 42, вторым и третьим входами первого буфера 45, вторым входом первого оперативного запоминающего устройства 46, третьим входом второго буфера 50, вторым входом второго оперативного запоминающего устройства 51 и первым входом синхронизатора 52. Выход первой схемы балансировки 42 соединен с входом первого преобразователя 43, выход которого является выходом реальной квадратуры кода «re» устройства цифровой обработки 20.

Выход первого регистра 44 соединен с первым входом первого буфера 45, выход которого соединен с первым входом первого оперативного запоминающего устройства 46. Выход первого оперативного запоминающего устройства 46 соединен с первым входом передатчика данных канала высокого разрешения 53, выход которого является выходом приемного канала высокого разрешения ВР. Первый вход второго регистра 49 является входом мнимой квадратуры сигнала «Im» устройства цифровой обработки 20 и соединен со вторым входом второй схемы балансировки 47. Второй вход второго регистра 49 является входом сигналов данных мнимой квадратуры «dco_i» устройства цифровой обработки 20 и соединен с первым входом второй схемы балансировки 47 и со вторым входом второго буфера 50. Выход второй схемы балансировки 47 соединен с входом второго преобразователя 48, выход которого является выходом мнимой квадратуры кода «im» устройства цифровой обработки 20. Выход второго регистра 49 соединен с первым входом второго буфера 50, выход которого соединен с первым входом второго оперативного запоминающего устройства 51. Выход второго оперативного запоминающего устройства 51 соединен со вторым входом передатчик данных канала высокого разрешения 53. Второй, третий и четвертый входы синхронизатора 52 являются соответственно (ТИ) тактовый импульс, синхронизации (ИНО) импульс начала отсчета и информационным (Интерфейс ЦП) центрального процессора входами устройства цифровой обработки 20. Первый выход синхронизатора 52 соединен с четвертыми входами первого 46 и второго 51 оперативных запоминающих устройств. Второй выход синхронизатора 52 соединен с третьими входами первого 46 и второго 51 оперативных запоминающих устройств. Третий, четвертый, пятый и шестой выходы синхронизатора 52 соединены соответственно с третьим, четвертым, пятым и шестым входами передатчика данных канала высокого разрешения 53.

Рассмотрим работу радиолокационного приемника с каналами высокого разрешения на примере прохождения принимаемого сигнала по одному приемному каналу. Поскольку построение n-ых каналов идентично первому каналу, то прохождение принимаемого сигнала по ним будет аналогично.

Входной сигнал на второй промежуточной частоте Fпч2 с СВЧ-приемника (не показанного на фиг.1) поступает на вход усилителя промежуточной частоты 1. При этом усилитель промежуточной частоты 1 обеспечивает программно-регулируемое усиление и управляемую частотную селекцию сигналов. Более подробно схема усилителя промежуточной частоты 1 описана в изобретении («Модуль усилителя промежуточной частоты», патент РФ №2291556). С выхода усилителя промежуточной частоты 1 сигнал поступает на вход аналого-цифрового преобразователя 2, на тактовый вход которого поступает сигнал частоты дискретизации с первого выхода формирователя опорных частот 9.

С выхода аналого-цифрового преобразователя 2 сигнал в цифровой форме поступает на цифровой формирователь квадратур 3. Синхронизирующий выход аналого-цифрового преобразователя 2 соединен с входами синхронизации цифрового формирователя квадратур 3, устройства цифрового гетеродинирования 5, цифрового сумматора 7 и передатчика данных 8. С выхода цифрового формирователя квадратур 3 цифровые сигналы, соответствующие реальной Re и мнимой Im квадратурным составляющим сигнала, поступают на первый вход устройства цифрового гетеродинирования 5, на второй вход которого поступают корректирующие коэффициенты с выхода постоянного запоминающего устройства 4. Код частоты цифрового гетеродина поступает на управляющий вход устройства цифрового гетеродинирования 5 с первого выхода адаптера 6. После гетеродинирования сигнал поступает на цифровой сумматор 7, где происходит суммирование отсчетов сигнала на интервале одного элемента дальности. Количество суммируемых выборок, задержка начала зоны приема относительно импульса начала отсчета ИНО, количество элементов дальности в зоне приема, задержка начала кадра относительно тактового импульса (количество пропускаемых импульсов начала отсчета ИНО, следующих после тактового импульса) и размер кадра (количество импульсов начала отсчета ИНО в кадре) определяются соответствующими кодами, поступающими на управляющий вход цифрового сумматора 7 со второго выхода адаптера 6.

После суммирования отсчетов сигнала в цифровом сумматоре 7 производится деление суммарного сигнала на количество суммируемых выборок (нормировка данных) и полученный сигнал поступает на передатчик данных 8, который обеспечивает передачу выходной цифровой информации в устройство вторичной обработки сигналов радиолокационной станции по последовательным LVDS шинам.

Входной сигнал на первой промежуточной частоте Fпч1 с СВЧ-приемника (в СВЧ-приемнике предусмотрено разветвление сигнала первой промежуточной частоты) поступает на вход полосового фильтра первой промежуточной частоты 10 и далее на фазовый детектор 11, на управляющий вход которого поступает сигнал опорной частоты Fоп с третьего выхода формирователя опорных частот 9. В фазовом детекторе 11 формируются реальная Re и мнимая Im квадратурные составляющие сигнала, которые поступают соответственно на входы первого 12 и второго 13 фильтров нижних частот. С выхода первого фильтра нижних частот 12 сигнал через первый операционный усилитель 14 поступает на вход первого аналого-цифрового преобразователя канала высокого разрешения 16, с выхода которого в цифровой форме поступает на вход реальной квадратуры сигнала «Re» устройства цифровой обработки 20. С выхода второго фильтра нижних частот 13 сигнал через второй операционный усилитель 15 поступает на вход второго аналого-цифрового преобразователя канала высокого разрешения 17, с выхода которого в цифровой форме поступает на вход мнимой квадратуры сигнала «Im» устройства цифровой обработки 20. Устройство цифровой обработки 20 обеспечивает прием данных, поступающих из первого 16 и второго 17 аналого-цифровых преобразователей канала высокого разрешения, и передачу их по последовательным шинам LVDS на выход канала высокого разрешения. Кроме этого, устройство цифровой обработки 20 формирует сигналы балансировки, которые для реальной квадратуры поступают с выхода реальной квадратуры кода «re» устройства цифровой обработки 20 через первый цифроаналоговый преобразователь 18 на управляющий вход первого операционного усилителя 14, для мнимой квадратуры поступают с выхода мнимой квадратуры кода «im» устройства цифровой обработки 20 через второй цифроаналоговый преобразователь 19 на управляющий вход второго операционного усилителя 15.

Синхронизация устройства цифровой обработки 20 по приему информации от аналого-цифрового преобразователя канала высокого разрешения обеспечивается сигналами DCO (Data Clock Output), поступающими с синхронизирующего выхода первого аналого-цифрового преобразователя канала высокого разрешения 16 на вход сигналов данных реальной квадратуры «dco_r» и устройства цифровой обработки 20 и с синхронизирующего выхода второго аналого-цифрового преобразователя канала высокого разрешения 17 на вход сигналов данных мнимой квадратуры «dco_i» устройства цифровой обработки 20.

Управление радиолокационным приемником с каналами высокого разрешения производится центральным процессором БРЛС по интерфейсу SMI (Serial Management Interface) через приемопередатчики SMI усилителя промежуточной частоты 1, адаптера 6 и устройства цифровой обработки 20. Синхронизация работы приемных каналов обеспечивается тактовым импульсом ТИ, поступающим из синхронизатора БРЛС на тактовые входы усилителя промежуточной частоты 1, цифрового сумматора 7 и устройства цифровой обработки 20, импульсом начала отсчета ИНО, поступающим из синхронизатора БРЛС на входы начала отсчета по дальности цифрового сумматора 7 и устройства цифровой обработки 20.

На вход формирователя опорных частот 9 поступает опорный сигнал Fоп с задающего генератора БРЛС. Формирователь опорных частот 9 обеспечивает частотную фильтрацию опорного сигнала и формирование дифференциальных сигналов частоты дискретизации с уровнями и формой сигналов, необходимых для работы аналого-цифровых преобразователей приемного канала и приемного канала высокого разрешения, а также формирование сигнала опорной частоты фазового детектора.

Формирователь опорных частот 9 (фиг.2) работает следующим образом. Опорный сигнал с частотой опорного сигнала Fоп поступает на вход первого умножителя частоты 21, где его частота умножается на два, и поступает на первый полосовой фильтр 22, настроенный на частоту опорного сигнала 2Fоп. Отфильтрованный сигнал через первый усилитель 23 поступает на первый режекторный фильтр 24, настроенный на частоту Fоп. С первого режекторного фильтра 24 через второй усилитель 25 сигнал поступает на первый формирователь частоты дискретизации 26, где обеспечивается формирование дифференциального сигнала частоты дискретизации опорного сигнала 2Fоп, который с первого выхода формирователя опорных частот 9 поступает на аналого-цифровой преобразователь 2.

Для формирования других сигналов опорной частоты с первого режекторного фильтра 24 сигнал с частотой опорного сигнала 2Fоп поступает на усилитель-ограничитель 27 и через третий усилитель 28 на второй умножитель частоты 29, где его частота умножается на два. С выхода второго умножителя частоты 29 сигнал поступает на второй полосовой фильтр 30, который настроен на частоту опорного сигнала 4Fоп. Co второго полосового фильтра 30 через четвертый усилитель 31 сигнал поступает на второй формирователь частоты дискретизации 32, где обеспечивается формирование дифференциального сигнала частоты дискретизации опорного сигнала 4Fоп, который со второго выхода формирователя опорной частоты 9 поступает на первый 16 и второй 17 аналого-цифровые преобразователи канала высокого разрешения.

С усилителя-ограничителя 27 сигнал поступает на второй режекторный фильтр 33, настроенный на частоту опорного сигнала 2Fоп, и далее на третий полосовой фильтр 34, настроенный на третью гармонику сигнала с частотой 2Fоп. С выхода третьего полосового фильтра 34 сигнал с частотой опорного сигнала 6Fоп через пятый усилитель 35 поступает на третий умножитель частоты 36, где его частота умножается на два. С выхода третьего умножителя частоты 36 сигнал поступает на четвертый полосовой фильтр 37, который настроен на частоту опорного сигнала 12Fоп, и далее через шестой усилитель 38 на четвертый умножитель частоты 39, где его частота умножается на два. Далее сигнал поступает на пятый полосовой фильтр 40, который настроен на частоту опорного сигнала 24Fоп, и через седьмой усилитель 41 на третий выход формирователя опорной частоты 9, с которого на вход фазового детектора 11.

Рассмотрим работу устройства цифровой обработки 20 по функциональной схеме фиг.3. Устройство цифровой обработки 20 представляет собой устройство, предназначенное для приема данных, поступающих из микросхем аналого-цифрового преобразователя с высокой частотой дискретизации и передачи их в устройство вторичной обработки сигналов с частотой, соответствующей протоколу передачи данных по последовательным LVDS шинам.

Данные, поступающие на вход реальной квадратуры сигнала «Re» устройства цифровой обработки 20, записываются в первый буферный регистр 44 и первый буфер 45 сигналами сигналов данных реальной квадратуры «dco_r», поступающими из первого аналого-цифровых преобразователей канала высокого разрешения 16. Данные, поступающие на вход мнимой квадратуры синала «Im» устройства цифровой обработки 20, записываются во второй буферный регистр 49 и второй буфер 50 сигналами сигналов данных мнимой квадратуры «dco_i», поступающими из второго аналого-цифрового преобразователя канала высокого разрешения 17. Чтение данных из буферного оперативного запоминающего устройства и их запись в основное оперативное запоминающее устройство во всех каналах производится сигналом сигналов данных реальной квадратуры «dco_r» первого канала. Этот же сигнал поступает на первый вход синхронизатора 52 для формирования сигнала «wr_en» - разрешения записи данных в основное оперативное запоминающее устройство. Со второго выхода синхронизатора 52 сигнал «wr_en» поступает на третьи входы первого 46 и второго 51 оперативных запоминающих устройств [основных оперативных запоминающих устройств типа FIFO]. Сигнал «wr_en» формируется в соответствии с поступающими по управляющей шине SMI на управляющий вход устройства цифровой обработки 20 кодами задержки начала зоны приема относительно импульса начала отсчета ИНО, количества элементов дальности в зоне приема, задержки начала кадра относительно тактового импульса ТИ (количества пропускаемых импульсов начала отсчета ИНО, следующих после тактового импульса ТИ) и размера кадра (количества импульсов начала отсчета ИНО в кадре). Тактовый импульс ТИ поступает на второй вход синхронизатора 52, импульс начала отсчета ИНО - на третий вход, а на четвертый вход поступает управляющая информация по интерфейсу ЦП.

Данные из первого 46 и второго 51 оперативных запоминающих устройств поступают в передатчик данных канала высокого разрешения 53, с выхода первого оперативного запоминающего устройства 46 на первый вход передатчика данных канала высокого разрешения 53 и с выхода второго оперативного запоминающего устройства 51 на второй вход передатчика данных канала высокого разрешения 53, где преобразуются в последовательные коды в соответствии с протоколом передачи данных. Коды начала кадра, начала пачки и конца пачки передаются в служебных разрядах в соответствии с поступающими на передатчик данных канала высокого разрешения 53 из синхронизатора 52 сигналами: «ink» - импульс начала кадра, «inp» - импульс начала приема и «ikp» - импульс конца приема. Сигнал «ink» - с третьего выхода синхронизатора 52 на третий вход передатчика данных канала высокого разрешения 53, «inp» - с четвертого выхода синхронизатора 52 на четвертый вход передатчика данных канала высокого разрешения 53 и «ikp» - с пятого выхода синхронизатора 52 на пятый вход передатчика данных канала высокого разрешения 53.

Для формирования сигнала чтения данных «rdclock» из оперативных запоминающих устройств первого 46 и второго 51 используется сигнал «flvds» (частота LVDS), который также используется для синхронизации передатчика данных канала высокого разрешения 53 и поступает с шестого выхода синхронизатора 52 на шестой вход передатчика данных канала высокого разрешения 53. Сигнал чтения данных «rdclock» поступает с первого выхода синхронизатора 52 на четвертые входы первого 46 и второго 51 оперативных запоминающих устройств.

Первая 42 и вторая 47 схемы балансировки формируют управляющие коды в соответствии с состоянием старшего (знакового) разряда данных. Эти коды преобразуются в первом 43 и втором 48 преобразователях параллельного кода в последовательный и поступают с выхода реальной составляющей кода «re» устройства цифровой обработки 20 на вход первого цифроаналогового преобразователя 18 и с выхода мнимой составляющей кода «im» устройства цифровой обработки 20 на вход второго цифроаналогового преобразователя 19. Напряжения с выходов цифроаналоговых преобразователей поступают на первый 14 и второй 15 операционные усилители для компенсации постоянной составляющей сигналов.

Для подтверждения возможности реализации технического решения был изготовлен опытный образец четырехканального радиолокационного приемника с двумя каналами высокого разрешения с тактико-техническими характеристиками для конкретной бортовой радиолокационной станции.

Управление радиолокационным приемником от центрального процессора осуществлено с использованием интерфейса SMI (Serial Management Interface). Приемопередатчики интерфейса SMI адаптера, усилителя промежуточной частоты и устройства цифровой обработки реализованы на ПЛИС (программируемая логическая интегральная схема) и обеспечивают преобразование последовательного кода управляющей информации, поступающей по интерфейсу SMI в параллельный код управляющих сигналов.

Полосовые фильтры выполнены на LC - элементах. Умножители, усилители, фазовый детектор, аналого-цифровой преобразователь и цифроаналоговые преобразователи выбраны из промышленно выпускаемой элементной базы.

Цифровая обработка сигнала, поступающего с аналого-цифрового преобразователя, организована на базе ПЛИС и обеспечивает выполнение следующих операций: цифровое формирование квадратур входного сигнала, фильтрацию