Цифровой синтезатор частот

Иллюстрации

Показать всеИзобретение относится к радиосвязи и может быть использовано в помехозащищенных системах связи в качестве формирователя многочастотного сигнала. Достигаемый технический результат - обеспечение независимой регулировки как количества моногармоник и величин их частот, так и регулировки начальных фаз моногармоник. Цифровой синтезатор частот содержит опорный генератор, N цифровых интеграторов, N преобразователей кода, сумматор кода с N информационными входами, цифроаналоговый преобразователь, фильтр нижних частот, N блоков установки начальных фаз моногармоник синтезируемых колебаний, каждый из которых содержит сумматор-вычитатель и регистр памяти. 1 з.п. ф-лы, 3 ил.

Реферат

Изобретение относится к радиосвязи и может быть использовано в эффективных по скрытности передаваемых сообщений системах связи в качестве формирователя многочастотного сигнала, в котором в процессе передачи информации можно менять как количество моногармоник и номиналы их частот, так и начальные фазы для каждой из частот моногармоник независимо друг от друга, что делает данный сигнал практически неподдающимся расшифровке.

Известен цифровой синтезатор частот [Авторское свидетельство СССР №1205249, кл. Н03В 19/00, 1984], обеспечивающий формирование многочастотного сигнала, содержащий образцовый генератор, преобразователь кода, цифроаналоговый преобразователь (ЦАП), фильтр нижних частот, выход которого подключен к шине выходного сигнала синтезатора, N цифровых интеграторов, информационные входы которых соединены с N шинами кодов синтезируемых частот, мультиплексор, N информационных входов которого соединены с выходами соответствующих цифровых интеграторов, а выход - с входом преобразователя кодов, накапливающий сумматор, информационный вход которого соединен с выходом преобразователя кодов, а выход с информационным входом ЦАП, а также блок синхронизации, вход которого соединен с выходом образцового генератора, первая группа выходов соединена с входом тактирования каждого цифрового интегратора и ЦАП, вторая группа выходов соединена с адресным входом мультиплексора, а третья группа выходов соединена с входами тактирования мультиплексора и преобразователя кода, а также с входами тактирования и установки нуля накапливающего сумматора.

Однако данный цифровой синтезатор частот имеет низкую частоту дискретизации fд, которая зависит от времени занесения кода в накапливающий сумматор, т.е. от быстродействия последнего, а частота дискретизации согласно теореме В.А.Котельникова определяет максимальную синтезируемую частоту синтезатора Fmax<fд/2. Кроме того, частота дискретизации данного синтезатора, как это следует из формулы fд=f0/N+1, где f0 - частота следования импульсов на выходе образцового генератора; N - количество частот в выходном сигнале синтезатора, уменьшается с ростом N. Таким образом, недостатком данного синтезатора является ограниченный со стороны высоких частот Fmax диапазон синтезируемых колебаний, который уменьшается с ростом N.

Наиболее близким к предлагаемому изобретению является цифровой синтезатор частот [Патент РФ №2030092, кл. Н03В 19/00], содержащий опорный генератор, N цифровых интеграторов, N преобразователей кода, сумматор кодов с N информационными входами, последовательно соединенные ЦАП и фильтр нижних частот (ФНЧ), выход которого является выходом устройства, причем тактовый вход ЦАП подключен к выходу опорного генератора (ОГ) и соединен с тактовыми входами N цифровых интеграторов, информационные входы которых являются кодовыми шинами задания синтезируемых частот, а выходы соединены с соответствующими входами N преобразователей кодов, выходы которых подключены к соответствующим информационным входам сумматора кодов с N информационными входами, выход которого соединен с информационным входом ЦАП, а тактовый вход с выходом ОГ.

При этом сумматор кодов с N информационными входами выполнен в виде log2N суммирующих блоков, каждый из которых выполнен на N/2r регистрах памяти, где r - номер суммирующего блока, при этом первый и второй входы сумматоров первого суммирующего блока являются соответствующими из N информационных входов сумматора кодов с N информационными входами, выход каждого из сумматоров в каждом из суммирующих блоков подключен к входу соответствующего регистра памяти, выход каждого из регистров памяти с нечетным номером r-го суммирующего блока соединен с первым входом соответствующего сумматора (r+1)-го суммирующего блока, выход каждого из регистров памяти с четным номером r-го суммирующего блока соединен со вторым входом соответствующего сумматора (r+1)-го суммирующего блока, тактовые входы всех регистров памяти всех суммирующих блоков объединены и являются тактовым входом сумматора кодов с N информационными входами, выходом которого является выход регистра памяти (log2N)-го суммирующего блока.

Кроме того, каждый из N цифровых интеграторов содержит последовательно соединенные умножитель кода, первый сумматор, первый регистр памяти, второй регистр памяти, мультиплексор, блок синхронизации, Р каналов, каждый из которых выполнен в виде последовательно соединенных корректора кода, сумматора и регистра памяти, выход которого подключен к соответствующему информационному входу мультиплексора, при этом входы умножителя кода и корректоров кода Р каналов объединены и являются информационным входом цифрового интегратора, другой вход первого сумматора объединен с другими входами сумматоров Р каналов и подключен к выходу первого регистра памяти, тактовые входы первого и второго регистров памяти и регистров памяти Р каналов объединены и подключены к первому выходу блока синхронизации, второй и третий выходы которого соединены соответственно с первым и вторым управляющими входами мультиплексора, выход которого является выходом цифрового интегратора, а тактовый вход блока синхронизации является входом тактирующего сигнала цифрового интегратора.

Данный цифровой синтезатор частот обеспечивает получение многочастотного сигнала с расширенным в область высоких частот Fmax диапазоном синтезируемых колебаний при обеспечении независимости максимальной синтезируемой частоты синтезатора от количества частот в формируемом многочастотном сигнале, в состав которого могут включаться моногармоники из диапазона частот Fmin-Fmax работы синтезатора в любом наборе, частоты отдельных составляющих которых можно менять независимо друг от друга посредством изменения управляющих кодов установки частоты KFi.

Однако недостатком данного синтезатора многочастотных сигналов является то, что он не имеет возможности изменения начальных фаз моногармоник из диапазона рабочих частот. В результате указанного недостатка при использовании данного устройства в системах связи не удается, как показано в работе [Н.П.Суворов. О развитии теории сигналов. - Радиотехника, 1985, вып.72, с.47-53], обеспечить такую же скрытность при передаче сообщений, как в помехозащищенных системах связи, в которых в процессе передачи информации можно менять как количество частот (моногармоник) в излучаемом сигнале, так и их начальные фазы.

Предлагаемым изобретением решается задача расширения функциональных возможностей устройства за счет обеспечения независимой регулировки как количества моногармоник и величин их частот посредством изменения управляющих кодов KFi, так и обеспечения независимой регулировки в пределах от 0 до 360° начальных фаз моногармоник посредством изменения Kϕi кодов установки фазы. Это, при использовании предлагаемого устройства в системах связи, повышает скрытность радиосвязи. Объясняется это тем, что формируемый предлагаемым устройством сложный многочастотный сигнал, в котором в процессе передачи сообщения можно менять как количество частот моногармоник и их номиналы в излучаемом сигнале, так и начальные фазы для каждой частоты, практически не поддается расшифровке.

Для достижения этого технического результата в цифровой синтезатор частот, содержащий опорный генератор, N цифровых интеграторов, N преобразователей кода, сумматор кода с N информационными входами, последовательно соединенные ЦАП и ФНЧ, выход которого является выходом устройства, причем тактовый вход ЦАП подключен к выходу ОГ и соединен с тактовым входом сумматора кодов с N информационными входами, выход которого соединен с информационным входом ЦАП, а соответствующие информационные входы соединены с соответствующими выходами N преобразователей кодов, выход ОГ также подключен к тактовым входам N цифровых интеграторов, информационные входы которых являются кодовыми шинами задания синтезируемых частот, при этом сумматор кодов с N информационными входами выполнен в виде log2N суммирующих блоков, каждый из которых выполнен на N/2r сумматорах и N/2r регистрах памяти, где r - номер суммирующего блока, при этом первый и второй входы сумматоров первого суммирующего блока являются соответствующими из N информационных входов сумматора кодов с N информационными входами, выход каждого из сумматоров в каждом из суммирующих блоков подключен к входу соответствующего регистра памяти, выход каждого из регистров памяти с нечетным номером r-го суммирующего блока соединен с первым входом соответствующего сумматора (r+1)-го суммирующего блока, выход каждого из регистров памяти с четным номером r-го суммирующего блока соединен со вторым входом соответствующего сумматора (r+1)-го суммирующего блока, тактовые входы всех регистров памяти всех суммирующих блоков объединены и являются тактовым входом сумматора кодов с N информационными входами, выходом которого является выход регистра памяти (log2N)-го суммирующего блока, а каждый из N цифровых интеграторов содержит последовательно соединенные умножитель кода, первый сумматор, первый регистр памяти, второй регистр памяти и мультиплексор, а также блок синхронизации и Р каналов, каждый из которых выполнен в виде последовательно соединенных корректора кода, сумматора и регистра памяти, выход которого подключен к соответствующему информационному входу мультиплексора, при этом входы умножителя кода и корректоров кода Р каналов объединены и являются информационным входом цифрового интегратора, другой вход первого сумматора объединен с другими входами сумматоров Р каналов и подключен к выходу первого регистра памяти, тактовые входы первого и второго регистров памяти и регистров памяти Р каналов объединены и подключены к первому выходу блока синхронизации, второй и третий выходы которого соединены соответственно с первым и вторым управляющими входами мультиплексора, выход которого является выходом цифрового интегратора, а тактовый вход блока синхронизации является входом тактирующего сигнала цифрового интегратора, дополнительно введены N блоков установки начальных фаз моногармоник синтезируемых колебаний, первые информационные входы которых являются кодовыми сигналами задания начальных фаз моногармоник из диапазона синтезируемых частот, а вторые информационные входы, тактовый вход и выход которого подключены соответственно к выходам соответствующих N цифровых интеграторов, выходу опорного генератора и к информационным входам соответствующих N преобразователей кодов.

При этом каждый из N блоков установки начальных фаз моногармоник синтезируемых колебаний содержит последовательно соединенные сумматор-вычитатель и регистр памяти, выход и тактовый вход которого являются соответственно выходом и тактовым входом блока установки начальных фаз, первыми и вторыми информационными входами которого являются соответственно первый и второй входы сумматора-вычитателя.

Сопоставительный анализ с прототипом показывает, что заявляемый синтезатор отличается наличием новых блоков: N блоков установки начальных фаз моногармоник синтезируемых колебаний и их связями с остальными элементами схемы. Таким образом, заявляемый синтезатор соответствует критерию изобретения «новизна».

Сравнение заявляемого решения с другими техническими решениями показывает, что сумматоры-вычитатели и регистры памяти, входящие в состав каждого из N блоков установки начальных фаз моногармоник синтезируемых колебаний, широко известны и их схемотехническая реализация не вызывает затруднений. Однако, при соединении данных блоков в соответствии с указанными связями с остальными элементами схемы в заявляемом цифровом синтезаторе частот они, в составе блоков установки начальных фаз, проявляют новые свойства, что приводит к расширению функциональных возможностей устройства путем получения многочастотного сигнала с возможностью независимого оперативного изменения начальных фаз моногармоник из диапазона рабочих частот синтезатора при сохранении диапазона синтезируемых колебаний и обеспечении независимости максимальной синтезируемой частоты синтезатора от количества частот в формируемом многочастотном сигнале. В результате этих новых технических возможностей предлагаемый цифровой синтезатор частот при его использовании в системах связи позволяет повысить скрытность передаваемой информации от противоположной стороны. Это позволяет сделать вывод о соответствии технического решения критерию «существенные отличия».

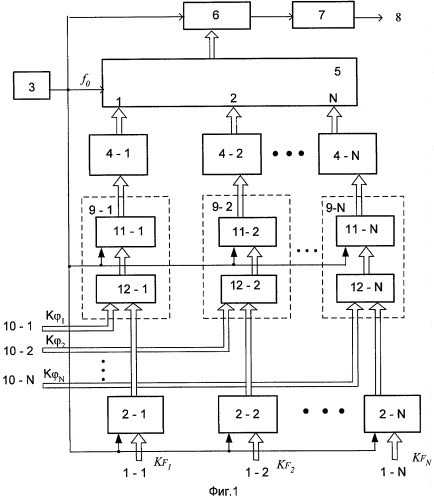

На фиг.1 представлена структурная электрическая схема цифрового синтезатора частот.

Цифровой синтезатор частот (фиг.1) содержит шины 1-1, 1-2,...,1-N кодов синтезируемых частот, цифровые интеграторы 2-1, 2-2,...,2-N, опорный генератор 3, преобразователи 4-1, 4-2,...,4-N кода, сумматор 5 кодов с N информационными входами, ЦАП 6,фильтр 7 нижних частот и шину 8 выходного сигнала, блоки установки начальных фаз моногармоник 9-1, 9-2,...,9-N, шины 10-1, 10-2,...,10-N кодов задания начальных фаз моногармоник синтезируемых частот. Выход опорного генератора 3 соединен с тактовыми входами ЦАП 6, сумматора 5 кодов с N информационными входами, блоков 9-1, 9-2,...,9-N установки начальных фаз и тактовыми входами N цифровых интеграторов 2-1, 2-2,...,2-N, информационные входы которых являются кодовыми шинами 1-1, 1-2,...,1-N задания синтезируемых частот, а выходы соединены с входами соответствующих блоков 9-1, 9-2,...,9-N установки начальных фаз моногармоник. Выходы последних подсоединены к входам соответствующих преобразователей 4-1, 4-2,...,4-N кода, выходы которых подключены к соответствующим информационным входам сумматора 5 кодов с N информационными входами, выход которого соединен с информационным входом ЦАП 6. Выход ЦАП соединен с входом фильтра 7 нижних частот, выход которого является выходной шиной 8 цифрового синтезатора частот.

Каждый из N блоков 9 установки начальных фаз моногармоник синтезируемых колебаний содержит последовательно соединенные сумматор-вычитатель 12 и регистр памяти 11, выход и тактовый вход которого являются соответственно выходом и тактовым входом блока 9 установки начальных фаз, первыми и вторыми информационными входами которого являются соответственно первый и второй входы сумматора-вычитателя 12.

Количество блоков установки начальных фаз 9-1, 9-2,...,9-N равно количеству цифровых интеграторов 2-1, 2-2,...,2-N и количеству блоков 4-1, 4-2,...,4-N преобразователей кода и равно наибольшему числу моногармоник в синтезируемом многочастотном сигнале.

При этом сумматор кодов 5 с N информационными входами и каждый из N цифровых интеграторов 2 для сохранения верхней границы диапазона синтезируемых колебаний и обеспечения независимости максимальной синтезируемой частоты синтезатора от количества частот в формируемом многочастотном сигнале выполнен в соответствии со схемами прототипа [Патент РФ №2030092], приведенными на фиг.2, 3.

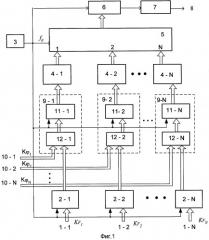

Сумматор 5 кодов с N информационными входами (фиг.2) выполнен в виде log2N суммирующих блоков 13, каждый из которых выполнен на N/2r сумматорах 14 и N/2r регистрах 15 памяти, где r - номер суммирующего блока. Первый и второй входы сумматоров 14 первого суммирующего блока 13-1 являются соответствующими из N информационных входов сумматора 5 кодов с N информационными входами, выход каждого из сумматоров 14 в каждом из log2N суммирующих блоков 13 подключен к входу соответствующего регистра 15 памяти. Выход каждого из регистров памяти с нечетным номером r-го суммирующего блока соединен с первым входом соответствующего сумматора 14 (r+1)-го суммирующего блока, выход каждого из регистров памяти с четным номером r-го суммирующего блока соединен с вторым входом соответствующего сумматора 14 (r+1)-го суммирующего блока. Тактовые входы всех регистров 15 памяти всех суммирующих блоков объединены и являются тактовым входом сумматора 5 кодов с N информационными входами, выходом которого является выход регистра памяти 13-log2N суммирующего блока.

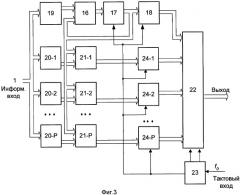

Каждый из N цифровых интеграторов 2 (фиг.3) содержит последовательно соединенные умножитель 19 кода, первый сумматор 16, первый регистр 17 памяти, второй регистр 18 памяти и мультиплексор 22, а также блок 23 синхронизации и Р каналов, каждый из которых выполнен в виде последовательно соединенных корректора 20 кода, сумматора 21 и регистра 24 памяти, выход которого подключен к соответствующему информационному входу мультиплексора 22. Входы умножителя 19 кода и корректоров 20-1, 20-2,...,20-Р кода Р каналов объединены и являются информационным входом цифрового интегратора 2. Другой вход первого сумматора 16 объединен с другими входами сумматоров 21-1, 21-2,...,21-Р Р каналов и подключен к выходу первого регистра 17 памяти. Тактовые входы первого 17 и второго 18 регистров памяти и регистров 24-1, 24-2,...,24-Р памяти Р каналов объединены и подключены к первому выходу блока 23 синхронизации, второй и третий выходы которого соединены соответственно с первым и вторым управляющими входами мультиплексора 22. Выход мультиплексора является выходом цифрового интегратора 2, а тактовый вход блока 23 синхронизации - входом тактирующего сигнала цифрового интегратора.

Принцип действия цифрового синтезатора частот, как и устройства прототипа, основан на одновременном вычислении кодов выборок N колебаний заданных частот и последующем формировании суммарного многочастотного сигнала.

Синтезатор работает следующим образом.

Сигнал на шине 8 выходного сигнала синтезатора U(t)вых представляет собой сумму гармонических функций, например синусоид единичной амплитуды:

где t - текущее время, соответствующее моментам nT0 (n=0, 1, 2,...);

- номер функции;

Fi и ϕi - соответственно синтезируемая частота и начальная фаза i-й функции.

Частоты Fi произвольны, не связаны какими-либо соотношениями и задаются на шинах 1-1, 1-2,...,1-N кодов КFi синтезируемых частот F1, F2,...,FN.

Начальные фазы ϕi, каждой i-й функции также произвольны, не связаны какими-либо соотношениями и задаются на шинах 10-1, 10-2,...,10-N кодов Kϕi задания начальных фаз моногармоник синтезируемых колебаний.

Цифровые интеграторы 2-1, 2-2,...,2-N по тактовым импульсам, поступающим от опорного генератора 3 с частотой дискретизации fo, формируют на своих выходах коды, соответствующие фазе синусоидального колебания в дискретные моменты времени.

Код текущей фазы синтезируемой частоты Fi с выхода цифровых интеграторов 2-1, 2-2,...,2-N поступает на вторые информационные входы соответствующих блоков 9-1, 9-2,...,9-N установки начальных фаз моногармоник синтезируемых колебаний. В сумматорах-вычитателях 12-1, 12-2,...,12-N данных блоков код фазы каждой i-й функции корректируется кодом Kϕi, поступающим на первые информационные входы сумматоров-вычитателей 12-1, 12-2,...,12-N с шин 10-1, 10-2,...,10-N задания начальных фаз моногармоник синтезируемого колебания, на соответствующую величину сдвига фазы ϕi. В результате этого на выходах сумматоров-вычитателей 12-1, 12-2,...,12-N формируется код текущей фазы синтезируемой моногармоники с учетом добавки ϕi, которая может меняться в каждом канале устройства от 0 до 360°. Таким образом, изменяя ϕi путем изменения кода Kϕi, можно менять фазы моногармоник в синтезируемом многочастотном сигнале.

Код текущей фазы с выхода сумматоров-вычитателей 12-1, 1 2-2,...,1 2-N, равный:

где

Ki - код синтезируемой частоты;

R - параметр (емкость) цифрового интегратора;

через буферные регистры 11-1, 1-2,...,11-N памяти, тактируемые частотой f0 ОГ, поступает на соответствующие входы преобразователей 4-1, 4-2,...,4-N кода фазы.

Введение дополнительных регистров 11-1, 11-2,...,11-N позволяет снизить требования к быстродействию устройства за счет известного приема «конвеерного» построения цифровых схем.

Преобразователи 4-1, 4-2,...,4-N кода представляют собой фазосинусные преобразователи и осуществляют переход от отсчетов коды фазы к отсчетам кодов амплитуд моногармоник генерируемых колебаний.

Сумматор 5 кодов в каждый тактовый момент времени nT0 вычисляет сумму кодов выборок N синусоид и формирует на выходе коды К(nT0), соответствующие выборкам суммарного сигнала в данные моменты времени.

Сигнал на выходе ЦАП 6 представляет собой ступенчато постоянную аппроксимацию функции U(t)вых с периодом дискретизации Т0.

Фильтр 7 нижних частот отделяет побочные компоненты спектра, связанные с дискретизацией.

В предложенном синтезаторе, принцип действия которого, как и прототипа, основан на одновременном формировании кодов выборок всех N колебаний заданных частот и последующем формировании суммарного многочастотного сигнала, тактовая частота (частота дискретизации) не зависит от количества частот в формируемом сигнале и определяется выражением

где tmax - наибольшее время срабатывания одного из функциональных узлов синтезатора.

В результате этого максимальная синтезируемая частота предлагаемого синтезатора, во-первых, равна максимальной синтезируемой частоте прототипа и, во-вторых, не зависит от количества частот в многочастотном сигнале.

При этом преимущество предложенного цифрового синтезатора частот по сравнению с прототипом состоит в следующем.

В прототипе отсутствует возможность изменения начальных фаз моногармоник из диапазона рабочих частот синтезатора, что ограничивает его применение в перспективных системах радиосвязи с повышенной помехоустойчивостью.

В предложенном цифровом синтезаторе частот, во-первых, как и в прототипе, обеспечивается независимая друг от друга установка количества моногармоник и величин их частот посредством изменения управляющих кодов КFi установки частоты и, во-вторых, за счет введения дополнительных N блоков установки начальных фаз моногармоник синтезируемого колебания и соединении их в соответствии с указанными связями с остальными элементами схемы обеспечивается независимая регулировка в пределах от 0 до 360° начальных фаз моногармоник посредством изменения кодов Kϕi установки фазы. Это существенно расширяет функциональные возможности устройства и повышает при его использовании в системах радиосвязи помехозащищенность последних. Достигается это тем, что формируемый предлагаемым цифровым синтезатором сложный многочастотный сигнал, в котором в процессе передачи информации можно менять как количество частот и их номиналы, так и начальные фазы каждой из частот, практически не поддается расшифровке [Н.П.Суворов. О развитии теории сигналов. - Радиотехника, 1985, вып.72, с.47-53].

1. Цифровой синтезатор частот, содержащий опорный генератор, N цифровых интеграторов, N преобразователей кода, сумматор кодов с N информационными входами, последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом устройства, тактовый вход цифроаналогового преобразователя подключен к выходу опорного генератора и соединен с тактовым входом сумматора кодов с N информационными входами, выход которого соединен с информационным входом цифроаналогового преобразователя, а соответствующие информационные входы соединены с соответствующими выходами N преобразователей кода, выход опорного генератора также подключен к тактовым входам N цифровых интеграторов, информационные входы которых являются кодовыми шинами задания синтезируемых частот, при этом сумматор кодов с N информационными входами выполнен в виде log2N суммирующих блоков, каждый из которых выполнен на N/2r сумматорах и N/2r регистрах памяти, где r - номер суммирующего блока, при этом первый и второй входы сумматоров первого суммирующего блока являются соответствующими из N информационных входов сумматора кодов с N информационными входами, выход каждого из сумматоров в каждом из суммирующих блоков подключен к входу соответствующего регистра памяти, выход каждого из регистров памяти с нечетным номером r-го суммирующего блока соединен с первым входом соответствующего сумматора (r+1)-го суммирующего блока, выход каждого из регистров памяти с четным номером r-го суммирующего блока соединен со вторым входом соответствующего сумматора (r+1)-го суммирующего блока, тактовые входы всех регистров памяти всех суммирующих блоков объединены и являются тактовым входом сумматора кодов с N информационными входами, выходом которого является выход регистра памяти (log2N)-го суммирующего блока, а каждый из N цифровых интеграторов содержит последовательно соединенные умножитель кода, первый сумматор, первый регистр памяти, второй регистр памяти и мультиплексор, а также блок синхронизации и Р каналов, каждый из которых выполнен в виде последовательно соединенных корректора кода, сумматора и регистра памяти, выход которого подключен к соответствующему информационному входу мультиплексора, при этом входы умножителя кода и корректоров кода Р каналов объединены и являются информационным входом цифрового интегратора, другой вход первого сумматора объединен с другими входами сумматоров Р каналов и подключен к выходу первого регистра памяти, тактовые входы первого и второго регистров памяти и регистров памяти Р каналов объединены и подключены к первому выходу блока синхронизации, второй и третий выходы которого соединены соответственно с первым и вторым управляющими входами мультиплексора, выход которого является выходом цифрового интегратора, а тактовый вход блока синхронизации является входом тактирующего сигнала цифрового интегратора, отличающийся тем, что дополнительно содержит N блоков установки начальных фаз моногармоник синтезируемых колебаний, первые информационные входы которых являются кодовыми сигналами задания начальной фазы моногармоник из диапазона синтезируемых частот, а вторые информационные входы, тактовый вход и выход которого подключены соответственно к выходам соответствующих N цифровых интеграторов, выходу опорного генератора и к информационным входам соответствующих N преобразователей кода.

2. Синтезатор частот по п.1, отличающийся тем, что каждый из N блоков установки начальных фаз моногармоник синтезируемых колебаний содержит последовательно соединенные сумматор-вычитатель и регистр памяти, выход и тактовый вход которого являются соответственно выходом и тактовым входом блока установки начальных фаз, первыми и вторыми информационными входами которого являются соответственно первый и второй входы сумматора-вычитателя.